高精度可编程信号发生器的设计与实现

2014-03-06潘金云刘列峰孙刘洋

潘金云 武 杰 刘列峰 孙刘洋

高精度可编程信号发生器的设计与实现

潘金云1,2武 杰1,2刘列峰1,2孙刘洋1,2

1(中国科学技术大学 核探测技术与核电子学国家重点实验室 合肥 230026)

2(中国科学技术大学 近代物理系 合肥 230026)

随着集成电路的发展,现代物理电子设备的仿真、测试、检测和维护过程中,经常需要使用到高精度的信号发生器。传统意义上的信号发生器主要利用振荡器产生信号,但振荡器的精度不高成为了限制其应用范围的瓶颈。所以为了解决高精度的需求,本文利用频率合成的技术,提出了一种基于Sigma-Delta数模转换器(Digital to Analog Converter, DAC)的可编程高精度信号发生器的设计与实现方法。经过实际测量,设计的信号发生器信噪比(Signal-to-Noise Ratio, SNR)好于110 dB,总谐波失真(Total Harmonic Distortion, THD)小于-110 dB,支持单端和差分输出,同时便携稳定。精度方面远高于市面上可以买到的信号发生器。

信号发生器,可编程,Sigma-Delta调制,高精度

随着集成电路的发展,现代物理电子设备的仿真、测试、检测和维护都对信号发生器的精度提出了很高的要求。如高精度采集板卡、高性能滤波器的性能测试等。信号发生器按照频率改变的方式,基本可以分为调谐式信号发生器、扫频式信号发生器、程控式信号发生器和频率合成式信号发生器等。前三种信号发生器的信号都是直接由模拟电路实现的振荡器产生,性能容易受元器件精度和周围环境影响,如温度、湿度、气压等。频率合成式信号发生器以高稳定度石英振荡器作为标准频率源,利用频率合成技术形成所需之任意频率的信号,具有与标准频率源相同的频率准确度和稳定度。所以频率合成技术对于高精度信号发生器是个很好的选择。

目前市面上常用的信号发生器种类和功能都很多,一般总谐波失真(Total Harmonic Distortion, THD)在-70dB左右,并且是单端输出[1],对于需要高精度模拟信号的应用,显然无法满足要求。本文从实际需求出发,利用频率合成的技术,基于高精度的Sigma-Delta数模转换器(Digital to Analog Converter, DAC),提出了一个可编程高精度信号发生器的设计与实现方法,给出了信号发生器的硬件设计和测试结果。用户不仅可以直接通过按键控制输出波形类型、调节波形参数并显示在液晶屏上,还可以通过算法让CPU产生用户自定义波形数据,实现信号源的可编程性。其主要性能指标为:输出带宽0-125Hz,信噪比(Signal-to-Noise Ratio, SNR)大于110dB,总谐波失真小于-110dB,频率和幅度连续可调,并支持单端和差分输出。

1 设计原理和硬件实现

近10年来,频率合成技术的发展经历了三代历程:第一代,直接频率合成技术;第二代,锁相频率合成技术;第三代,直接数字频率合成技术。直接频率合成以晶体振荡器作为信号源导致杂散分量多,难以做到较高的精度。锁相频率合成由于锁相环的本身的惰性环节,锁定时间长,频率切换速度慢且系统复杂。直接数字频率合成从相位概念出发,具有精确的相位、极高的频率分辨率和快速的频率转换时间,特别适用各种信号源的频率合成[2]。

直接频率合成的核心是相位累加器,系统性能的关键则依赖DAC和后端的低通滤波器。当代的数模信号转换的精度和速度都越来越高,常见的数模转换器类型包括并行型、折叠型、逐次逼近型、Sigma-Delta过采样型等[3]。除了Sigma-Delta过采样型,其他几种类型都为奈氏数模转换器,虽然它们速度很快,但是精度却很差。Sigma-Delta DAC是一种把高分辨率信号用脉冲密度调制编码为低分辨率信号的方法,同时运用了过采样和噪声整形技术,让噪声分布到更高的频段,降低有效带宽内的噪声功率,从而使DAC具有更好的抗混叠能力和更高的分辨率,降低了对后端滤波器的性能要求。虽然高精度是以牺牲转换速度为代价[4],但是对于200Hz以内的低频高精度的信号发生器Sigma-Delta型模数转换器却是个合适的选择。

1.1 设计原理

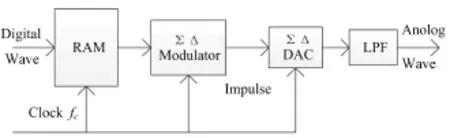

本信号发生器的原理图如图1所示,存储数字波形的RAM在取样时钟的作用下,依次读出其中的波形数值,送至Sigma-Delta调制器,将数字波形调制成脉冲密度,即1bit的数据流。脉冲密度再经过高精度的Sigma-Delta DAC转换为模拟波形,模拟波形经低通滤波器滤除高频成分,从而得到高精度的模拟信号。RAM中特定的数字波形,会被调制成对应的脉冲密度,从而产生相应的模拟信号。这样,用户只需要通过特定算法编写RAM中的波形数据,就可以产生所需要的模拟信号。这意味着信号发生器的可编程性是可以实现的。

图1 信号发生器原理图Fig.1 Schematic diagram of signal generator.

1.2 硬件实现

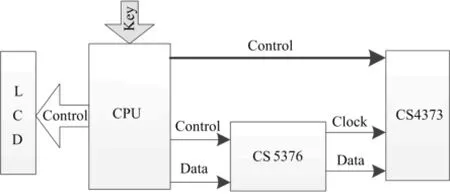

信号发生器的硬件结构如图2所示。CPU是整个系统的控制中心,直接控制着波形发生模块和液晶屏。CPU与波形发生器之间的数据通信方式为串行外设接口(Serial Peripheral Interface, SPI),接口中还包括同步等触发信号,如图3。

图2 信号发生器硬件图Fig.2 Hardware structure of signal generator.

图3 信号发生器触发同步特性Fig.3 Synchronization of signal generator.

在按键的控制作用下,一方面,由CPU依照特定算法产生波形的数字信号,通过SPI发送至CS5376并存储在RAM空间;另一方面,CPU产生控制信号,在液晶屏上显示波形信息和参数等。

正常工作时,CS5376的测试码流(Test Bit Stream, TBS)发生器将波形调制成1 bit数据流并送给CS4373,经模数转换和滤波,产生连续、高精度的差分或单端信号。CS4373的时钟和同步信号由CS5376依据输出数据速率决定,操作模式和输出幅度受CPU控制。由此,该信号发生器的输出是可编程的,幅度、频率可调的高性能信号。

信号源的触发同步特性是在CPU的控制下完成的,同步使能(MSEN和TSYNC置高)时,当CS5376检测到CPU产生的上升沿同步信号,在同步控制器的作用下,一方面给CS4373产生同步信号,使其内部寄存器复位,但此时没有同步时钟输入,DAC仍处于不工作状态;另一方面,CS5376复位内部TBS Generator的读取RAM的指针位置并开始读取波形数据并调制,同时产生同步的时钟信号,供DAC使用。

由图2可以看出,CPU是整个系统的控制核心。另外,由于Sigma-Delta调制在过采样和噪声整形方面的优异表现,非常适合高性能信号发生器的需求。所以CS5376和CS4373是系统性能的关键。

1.3 CS5376介绍

CS5376的TBS Generator主要由插值器和Sigma-Delta调制器构成,在采样时钟的控制下,循环读取RAM空间中的波形数据,经插值、调制、滤波成1bit的数据流,并传递给CS4373。因此用户只需编写相应的波形算法,利用CPU实现并通过SPI传递给CS5376,从而实现可编程的波形输出。插值器的作用是将同一个数字波形点反复多次调制,以进一步提高输出波形的精度。

CS5376为用户提供的TBS RAM空间大小为1024×24bit,所以用户最多可以写入1024个24bit的数字波形点。由于Sigma-Delta调制的结构特点,要求波形数据在首尾处必须连续,也就是当波形从一端复制平移到另一端,必须描绘出一条平滑的曲线。另外,用户还可以通过改变插值器的数值、输出数据速率、波形数据个数来改变波形频率。信号频率计算方法是:信号频率×波形数据个数×(插值器值+1)=输出数据速率。

CS5376的数字波形的数据编码方式为补码形式,最高位为符号位,有效位数为23位,所以幅度调整的最小步长为满幅度的1/223。依据信号频率的计算公式,在保证足够的过采样率前提下,也就是插值器中的数值不变。信号频率调整的最小步长为1/1024。

1.4 CS4373介绍

CS4373数字芯片的核心是一个24bit Sigma-Delta DAC,接收来自CS5376的1 bit数据流,经过内部反混叠滤波和衰减器衰减后输出。其有BUF和OUT两路差分输出,BUF是信号经放大器放大后的输出,负载能力强,性能精度稍差。差分OUT输出时典型的THD和SNR分别是-118dB和114dB,能够满足设计要求。CS4373的时钟和同步信号由CS5376产生,并输入至时钟控制模块产生需要的内部时钟。

由于CS4373是高精度的Sigma-Delta DAC,原则上对参考电压的要求非常高,Vref±间的电压要求为2.500V,同时要求差分布线,否则会直接影响模拟输出的精度。图4给出了参考电源的电路图。如图4所示,每个输出都相当于一个低通滤波器,用来进一步确保参考电源的稳定性。CS4373建议使用Linear Technology公司的高精度参考电源LT1019AIS8-2.5,并在输出端加上低通滤波来产生参考电压,实际输出为2.499V,为可接受范围。

图4 参考电源电路图Fig.4 Voltage reference circuit.

2 测试方案和结果

2.1 测试目标

系统设计目标:SNR>110dB,THD<-110dB,信号范围0-125Hz。根据信噪比的理论公式:SNR=6.02N+1.76可知,需要的理想测试ADC为20位,考虑到非理想情况和设计余量,测试的ADC选择为基于CompactRIO的24位高精度数据采集模块[5]。测试内容包括SNR和THD两个性能指标。

2.2 测试结果

测试系统主要可以产生正弦波、方波、脉冲波三种波形,主要测试信号针对10Hz、25Hz、31.25Hz、50Hz和125Hz的正弦波,幅度为2.5V差分输出。信号经24bit高精度数据采集模块采集8192个点,并传递给LabVIEW做快速傅里叶变换(Fast Fourier Transformation, FFT)和频谱分析。各频率下的测试结果如表1所示。其中,10Hz、31.25Hz、125Hz的频谱图如图5所示,图5中横坐标采用的是对数坐标,物理意义为对应的信号频率。仔细观察信号的频谱可以发现,频谱图中主峰频宽很窄,所有谐波分量都小于-110dB,频谱图中50Hz附近有一个-90dB左右的仅次于主峰的次峰。经过比较其他频率的信号频谱和采集卡不加测试信号时的频谱发现,此干扰信号始终存在且幅度不变,所以推断其为市电干扰,可以通过在输出端添加滤波器或者采用电池供电加以消除。

表1 测试数据Table 1 Testing data.

图5 正弦波测试频谱Fig.5 Spectrum of testing sine wave.

经过测算,不考虑市电干扰前提下,各信号的信噪比都大于110dB,总谐波失真小于-110dB,如表1所示。所以本设计基本满足设计目标,能够很好地应用于物理电子学设备的仿真、测试、检测与维护。此外,用户还可以利用系统的可编程性,运用新的算法,实现用户自定义波形,这无疑会极大地扩展本设计的适用范围,给科研工作带来很大的便利。

1 伍尚坤, 宋克柱, 吴义华. 高谱纯度低频信号源的设计与实现[J]. 核电子学与探测技术, 2006, 26(6): 936-938

WU Shangkun, SONG Kezhu, WU Yihua. A high-performance wave-generator based on DAC[J]. Nuclear Electronics and Detection Technology, 2006, 26(6): 936-938

2 石雄. 直接数字频率合成技术的研究与应用华[D]. 武汉: 华中科技大学, 2007

SHI Xiong. Research and application of direct digital synthesis technology[D]. Wuhan: Huazhong University of Science and Technology, 2007

3 张宏伟. 12位100 MSPS Pipeline ADC的设计与实现[D].长春: 国防科学技术大学, 2009

ZHANG Hongwei. The design and realization of a 12 bit, 100 MSPS, Pipeline ADC[D]. Changchun: National University of Defense Technology, 2009

4 孔阳. 一种适用于地震勘探仪器的低运算量数字滤波器的设计与研究[D]. 合肥: 中国科学技术大学, 2011

KONG Yang. Research on low power digital filter for seismic exploration system[D]. Hefei: University of Science and Technology of China, 2011

5 王丁丁, 武杰, 张杰, 等. 基于CompactRIO的数据采集模块设计[J]. 核技术, 2012, 35(7): 539-542

WANG Dingding, WU Jie, ZHANG Jie, et al. A data acquisition module based on CompactRIO[J]. Nuclear Techniques, 2012, 35(7): 539-542

CLC TL824

Design and implementation of a high-precision programmable signal generator

PAN Jinyun1,2WU Jie1,2LIU Liefeng1,2SUN Liuyang1,2

1(State Key Laboratory of Particle Detection & Electronics, University of Science and Technology of China, Hefei 230026, China)

2(Department of Modern Physics, University of Science and Technology of China, Hefei 230026, China)

Background: With the development of integrated circuits, the high-precision signal generator is always used in the process of simulation, testing, inspection and maintenance of electronic equipment in modern physics. The traditional signal generator generates signal by using oscillator, but the precision of oscillator is not high enough which becomes a bottleneck limiting the scope of application. Purpose: The aim is to address the needs of high-precision of signal generator, and design a programmable high-resolution signal generator. Methods: The direct digital frequency synthesizer technique and Sigma-Delta Digital to Analog Converter (DAC) were adopted to design this proposed high-precision signal generator. Digital chips CS5376 and CS4373 were employed together with the CompactRIO DAC to achieve the target of 110 dB signal-to-Noise Ratio (SNR) and -110 dB Total Harmonic Distortion (THD). Programmable waveform was prepared in the mainframe using appropriate software platform such as Matlab, LabVIEW, etc. Results: After the actual measurement, the designed signal generator is proved to be with the noise ratio of SNR better than 110dB, and the total harmonic distortion THD less than -110dB, and performs excellent in portability and stability. Conclusion: The performance of signal generator meets the need of our testing.

Signal generator, Programmable, Sigma-Delta modulator, High-resolution

TL824

10.11889/j.0253-3219.2014.hjs.37.070402

国家重大科技专项(No.2011ZX05008-005-061)及国家重大科研装备研制项目“深部资源探测核心装备研发”(No.ZDYZ2012-1-05-03)资助

潘金云,男,1988年出生,2011年毕业于中国科学技术大学,现为硕士研究生,研究方向为高速数据采集与嵌入式系统设计

武杰,E-mail: wujie@ustc.edu.cn

2014-03-25,

2014-04-23