一种采用硬件加速器的卫星导航接收机通用验证平台

2014-01-10黄仰博

陈 雷,黄仰博,葛 锐,欧 钢

(国防科技大学 电子科学与工程学院,长沙 410073)

1 引言

随着集成电路(integrated circuit,IC)设计规模日益增大,制造水平逐步提升,其仿真验证成为了当前IC设计的主要瓶颈之一。硬件加速器强大的仿真速度和查错能力使之成为大规模设计验证的优秀解决方案之一[1]。纵观全球,随着全球定位、导航服务需求飞速增长,用户对定位精度、接收机各方面性能都提出更高的要求。同时,包括北斗卫星导航系统(BeiDou navigation satellite system,BDS)、全球定位系统(global positioning system,GPS)和伽利略卫星导航系统(Galileo navigation satellite system,Galileo)在内的全球卫星导航系统(global navigation satellite system,GNSS)逐渐采用新型信号结构和新调制方式[2-3],这使得接收机基带数据处理的通道数倍增。为了适应如同复合二进制偏移载波(composite binary offset carrier,CBOC)信号、时分二进偏移载波(time multiplexed binary offset carrier,TMBOC)信号、改进的二进制偏移载波(alternate binary offset carrier,AltBOC)等调制的新体制信号的接收[4-5],其捕获跟踪算法的复杂度也逐渐提高,这对接收机基带处理芯片的设计提出了更高要求。当前,主流的集成电路功能仿真验证方法依旧是动态模拟仿真,即产生测试向量,并将测试向量加载到设计上,通过硬件描述语言(hardware description language,HDL)模拟器得到测试结果。将这些结果与参考结果相比较,以此来验证设计的正确性。然而,软件模拟器进的仿真速度会随着设计规模的急剧增大迅速降低。在PentiumⅣ的设计验证中,Intel公司使用了6 000个节点的PC Farm进行仿真,而测试的向量不过相当于实际系统运行2min所执行的测试向量[6]。

随着数字集成电路模块化,设计由很多IP核(intellectual property core,IP Core)帮助完成,芯片功能日益复杂,芯片的 “流片”成本越来越昂贵,一次 “流片”甚至需要上百万美元。为保证设计出的芯片性能是理想的,必须在流片前进行全面的有效的验证。当前,IC设计已经实现了标准化,而验证设计还没有一个规范的标准,其效率和速度还有很大的提升空间。根据系统完备性计算公式,假设每个IP有一个缺陷且导致系统5%的缺陷,那么10个IP缺陷将导致整个系统的完备性降为(95%)10=59.9%。因此一个完备的仿真对于IC设计是至关重要的。

当前主流的仿真手段主要有:软件仿真、硬件加速仿真器和现场可编程门阵列(field-programmable gate array,FPGA)在线仿真。软件仿真主要依赖 ModelSim、NC-Sim、ISE-Simulation等工具,其特点是调试方便,可见波形数量多,采样点数没有限制,浏览方便,但速度较慢,目前只有kHz量级。FPGA在线仿真速度最快、价格较便宜,但对于调试和故障排查非常不方便,需要添加Chip-Scope抓取波形,每改一次抓取信号就必须重新编译、布局、布线、生成二进制文件,对于稍微复杂的工程设计,一次流程就是几个小时,且抓取波形数量、长度都受到器件和内核空间制约(最长只有131 072点)。这对于故障调试、信号分析非常不利。硬件仿真加速器兼具了以上两种仿真方法的优点:调试方便、可见波形数量多、采样点数没有限制,可见波形长度没有限制、不需要综合布局布线,编译上线快、仿真速度快(相对软件仿真而言)通常在MHz级。对于设计师来说,最方便的是可以设置触发条件(断点),让程序在仿真触发条件满足时暂停,并可从断点处继续运行,这是前两种仿真手段所无法达到的,但其成本是三种仿真方法中最贵的。因此,中小规模的IC设计可以采用软件仿真;而中大规模或团队在多地点共同设计的情况更适合用硬件加速器[7]。本文所设计的验证平台主要采用Cadence公司推出的 Cadence®Incisive®Palladium®Ⅲ硬件加速器仿真器,其外形如图1所示。

图1 Palladium®Ⅱ加速器/仿真器

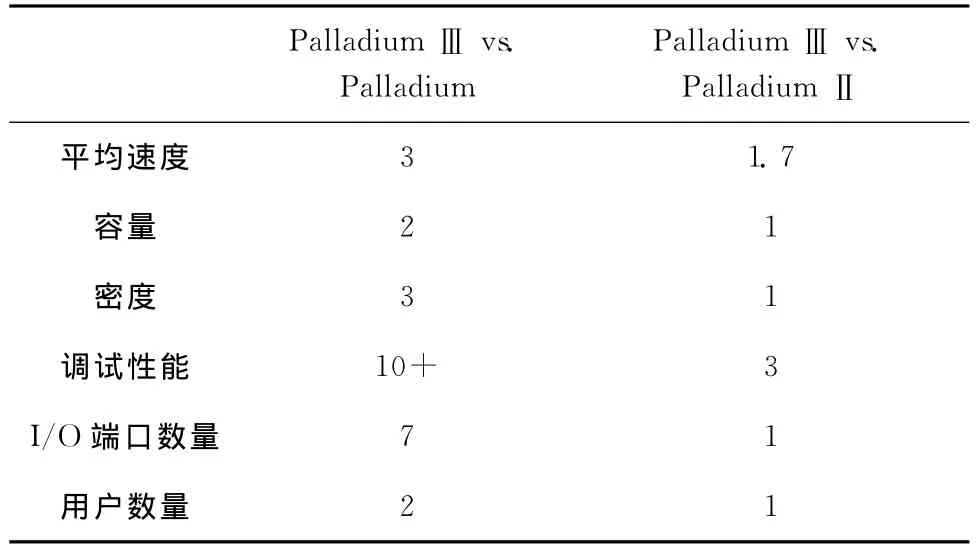

该仿真平台是业界第一个结合了高性能系统级验证自动化和验证管理、快速设计轮转,同时适合系统级芯片各个阶段设计及验证的硬件辅助验证解决方案。实现了所有工程设计和功能验证的硬件、软件以及全系统确认的自动化[8]。如表1所示,相比PalladiumⅡ,PalladiumⅢ的运行时间性能提升近1倍,调试环境优越。复杂设计的仿真速度接近2MHz,比普通仿真的性能高100万倍[8]。

表1 PalladiumⅢ与上一代系统的运行时间性能对比(倍数)[9]

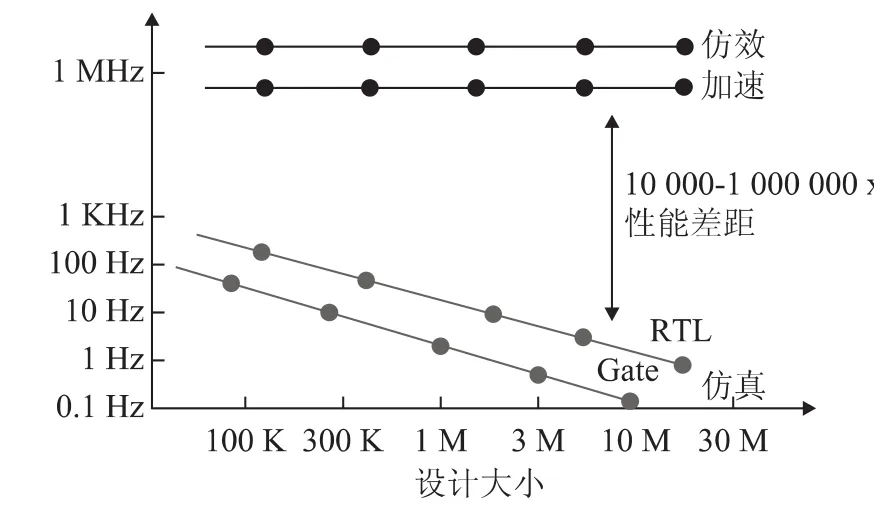

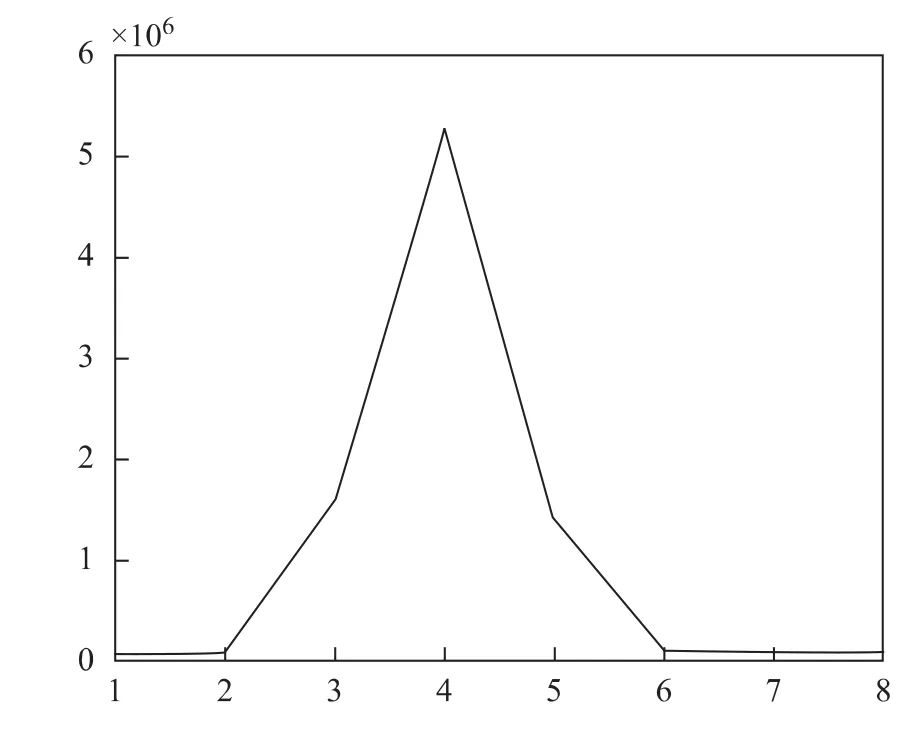

图2给出了大系统仿真速率(emulation)和软件仿真(simulation)随着规模增大变化曲线[9]。由图2可知,Palladium仿真时效性能并不随硬件规模增大而降低,而传统的仿真性能随着规模增大成比例的下降。对于10MHz规模的IC仿真,Palladium仿真效率相对传统仿真可提1 000万倍。

图2 大规模设计的在线仿真效能相比传统仿真提升10 000~1 000 000倍

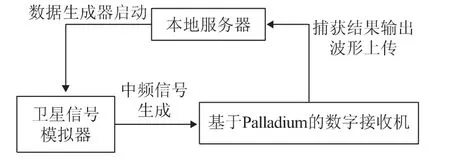

2 基于Palladium加速器的卫星导航接收机通用验证平台基本框图

基于Palladium加速器的卫星导航接收机通用验证平台主要由本地服务器、卫星信号模拟器、Palladium硬件加速器组成。其基本框图如下图3所示:

图3 卫星导航接收机通用验证平台基本框图

其中本地服务器的主要功能是完成测试向量的配置、初始化参数设置、启动控制Palladium设备上传波形以及检查确认。

卫星信号模拟器的主要功能是产生导航接收机所需要的各类导航卫星信号。特别的对于多体制导航接收机设计验证,信号生成器可以模拟产生实时的GPS、Galileo的民用信号以及BDS的军、民用卫星信号。并将产生的中频或者基带信号直接输出给Palladium加速器中的待测模块。

Palladium硬件加速器的主要功能是将测试工程导入设备,通过中央处理器(central processing unit,CPU)阵列模拟专用集成电路(application specific integrated circuit,ASIC)的基本单元,通过硬件电路实现逻辑功能的加速仿真验证。并将测试状态及结果实时输出给本地服务器,并在触发点处采集内部信号波形上传。

3 基于Palladium加速器的卫星导航接收机通用验证平台运行策略

3.1 实时数据生成策略

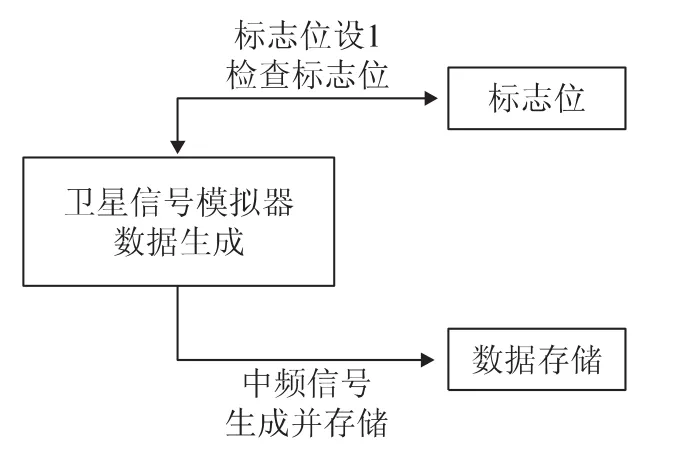

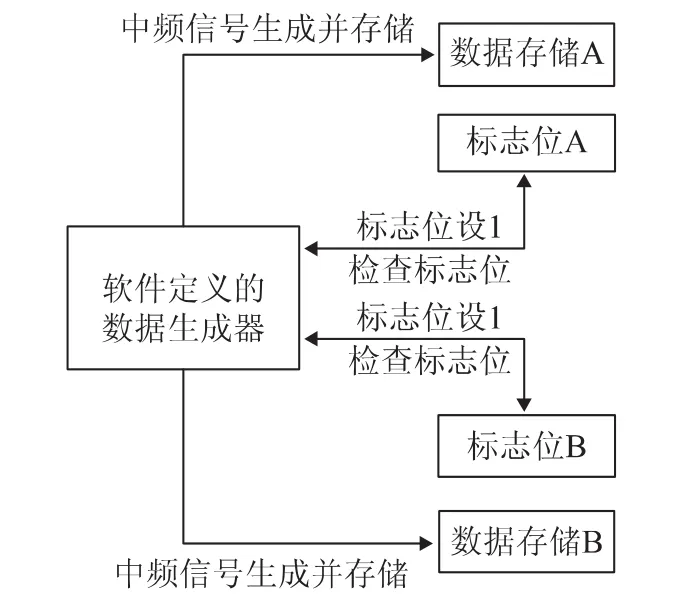

如图4所示,实时数据生成策略是通过软件定义的信号生成单元,配置卫星参数,启动并生成1ms的BDS某颗卫星某频点中频信号的数据。

信号生成单元在存储区设定标志位,当数据生成完毕并且未被提取存在的时候,标志位为1,生成器停止并等待数据提取;当数据被提取完毕后,标志位清除,数据生成单元继续生成下1ms中频数据。

图4 导航卫星信号模拟单元实时数据生成策略示意图

如图5所示,由于数据生成需要一定的运行时间,等待数据提取也需要一定的时间,为了使输入Palladium仿真器的数据保持连续,必须采取乒乓操作的策略。数据生成器设置2个1ms的数据存储区A和B,当仿真器从存储区调去数据文件A的同时,生成单元产生下一个1ms数据文件B,产生完毕后提示等待提取数据。前1ms数据文件A调用完毕并将标志位清0后,生成单元再产生下1ms数据生成并存储于A文件。标志位A置1。仿真器读完B文件后再切换到文件A。

图5 数据生成单元乒乓操作示意图

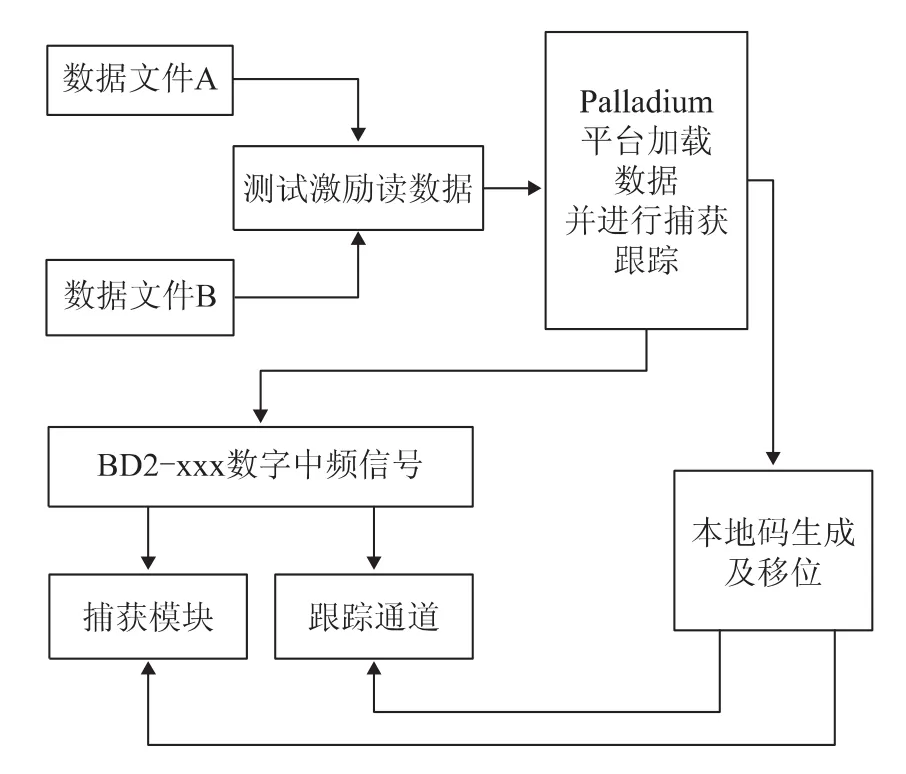

3.2 Palladium数据读取策略

Palladium仿真验证平台数据读取策略如图6所示,Palladium读取文件时,首先调用A文件,并将A文件中的数据置入仿真测试激励中定义的虚拟随机存取存储器(random access memory RAM)中,通过测试模块将数据输入待测模块。A文件数据读取完毕后产生page_switch标志,调取文件B,并将A文件标志位清零。测试激励读入数据后,将数据分别送入捕获模块和跟踪模块。于此同时,本地码生成模块也将通过测试激励将本地码加载到捕获跟踪通道中。

图6 Palladium仿真平台数据读取策略

其中,捕获模块通过移位相关累加后搜索最大值对应码片,获得捕获结果,并将捕获结果送入跟踪单元,跟踪单元转换捕获结果后进行精细跟踪。具体算法及实现不在此赘述。

4 芯片仿真验证流程与结果

4.1 芯片方针验证流程

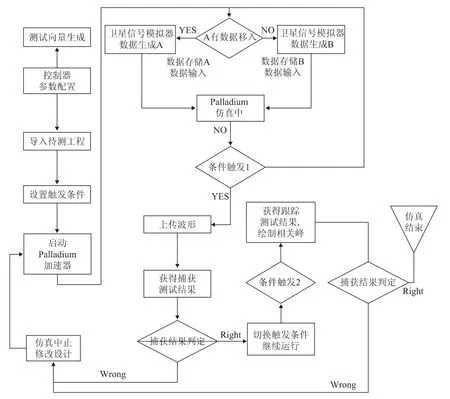

为了验证芯片设计的功能和性能,有必要对芯片进行全面细致的仿真。正如引言中所述,任何一个细小的错误,其迭代的结果对系统完备性的影响是非差严重的,并且对于接收机芯片设计来说也是必须避免的。这就要求对芯片的功能仿真和性能仿真必须准确且完备。对于卫星导航接收机基带芯片来说,有非常多的功能和性能项目需要仿真验证,由于本文侧重于介绍芯片研发所使用的Palladium仿真验证平台的设计,故在此仅对芯片仿真验证的主要流程进行介绍,完备的功能性能验证不在此赘述。采用Palladium硬件加速器的卫星导航接收机通用验证平台运行流程图如图7所示。

图7 芯片仿真验证流程图

芯片仿真验证的主要流程依次为:测试向量生成、控制器参数配置、导入待测工程、设置触发条件、启动Palladium加速器、数据移入(同时生成下一段数据)、Palladium仿真进行、捕获触发条件满足后暂停、上传波形、输出捕获结果、捕获结果判定、启动跟踪、跟踪触发条件满足、输出数据并绘制相关峰、根据相关峰判定跟踪结果。

4.2 具体验证步骤

1)测试向量生成

测试激励生成并会同待测模块共同编译。现实情况下的数字信号处理器(digital signal processor,DSP)完成的功能在此由RTL实现的微处理器(advanced reduced instruction set computer machines,ARM)核实现,完成总线控制信号的产生和控制,集成在处理器子模块中。配置好Palladium工程编译所需要的各类IP库,将测试工程代码和测试激励在服务器中进行工程编译。此阶段可验证代码语法的正确性,如果编译工具报告错误,则返回上一步骤修改后重新上传编译。

2)控制器参数配置

控制器参数通过Metrowerks Code Warrior for ARM Developer Suite软件配置信号类型、总线地址译码、寄存器读写以及捕获、跟踪通道的相关参数。具体过程不再赘述。将编译后将产生hex文件存放于服务器中,启动Palladium工程后将加载上述配置文件。

3)导入待测工程

通过工具命令语言(tool command language,TCL)启动Palladium工程的用户界面,导入预先设定好的工程脚本,系统将按照脚本配置好仿真所需的各类数据、代码文件的路径和参数。

4)信号仿真启动

待测工程导入完毕后,启动Matlab定义的数据生成单元,根据需要模拟的信号类型配置相关参数,并开始运行,生成数据文件。待乒乓操作的2组数据都生成完毕,即Matlab软件界面给出等待用户提取数据的提示时,可启动Palladium工程。

5)设置触发条件并启动Palladium加速器

在Palladium硬件加速仿真验证软件界面中的SDL Editor中,修改所需要的触发条件。这类似于Chip-Scope中的触发条件,不同点在于Palladium仿真既可以在触发条件处上传波形,又可以在触发条件处暂定整个工程的运行,这是硬件调试无法完成的。并且Palladium仿真可在工程仿真过程中随时暂定并修改触发条件。

6)条件触发、上传波形

相对于Chip-Scope中抓取实际数据波形而言,Palladium硬件加速仿真的优势在于它的可见波形多,容量大。在Palladium仿真过程中,可以看到代码中的所有信号的波形,并且能够逐段上传波形,而在Chip-Scope中,受制于FPGA硬件规模和工程规模,抓取的波形数量是有限的,抓取数据长度也是有限的;相对于Modersim、NCSim等软件仿真而言,Palladium硬件加速仿真的优势在于它的仿真速度急快。基于CPU模拟ASIC最小逻辑单元的原理,Palladium仿真虽然无法达到FPGA片上实际运行的时钟速率,但相对NCSim仿真提高了1 000倍[10]。

当Palladium工程满足触发条件,会在触发条件设置处(相当于C程序中的断点)中止运行,停等待用户响应。此时,可通过脚本上传触发条件满足后任意时间长度的数据波形。通过Sim-Vision软件可以查看波形和仿真结果。

7)获得捕获测试结果

捕获结果可以实时输出,也可以通过设置触发条件中止仿真并上传波形后通过波形数据找到数字接收机捕获模块的计算结果。Palladium仿真平台中的数字接收机将该捕获结果转换后送入跟踪通道,跟踪通道通过捕获结果修正相关峰的搜索范围。

8)获得跟踪测试结果

调整处理器配置参数,将BDS某频点信号的捕获结果作为跟踪仿真的输入,同时推算跟踪模块本地码生成模块的起始时间,配置相关参数后,以相关值计算完毕为触发条件,运行Palladium仿真系统,进行跟踪通道的仿真测试。

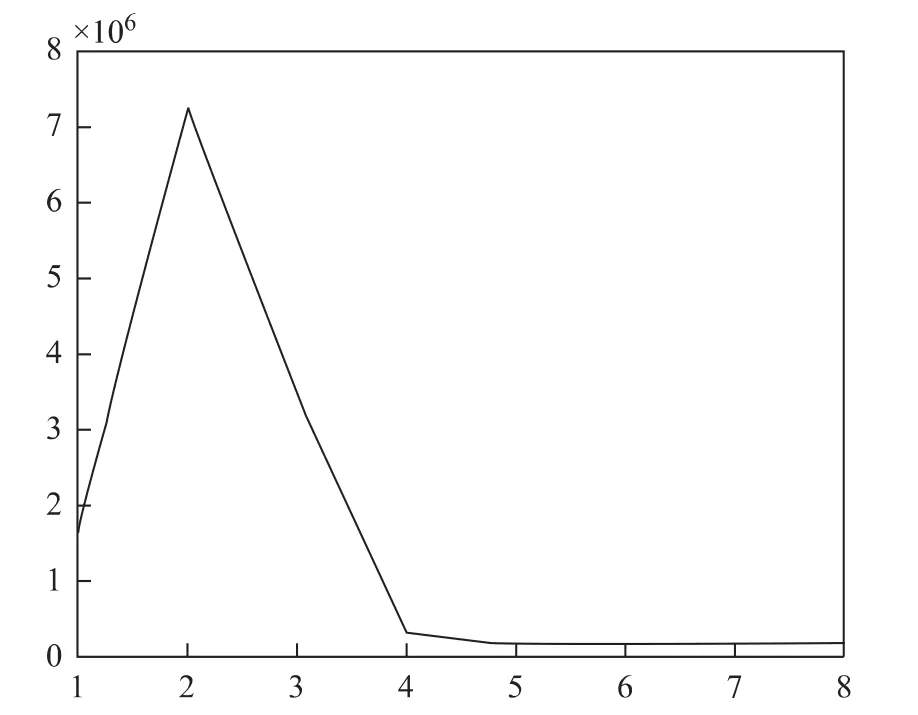

触发条件满足后Palladium通过脚本指令将数据上传至服务器中,并通过Matlab启动相关值转换并绘图,如图8所示。由图可知,当前相关值偏移约为2个码片,这和设置的本地码起始时间有对应关系。

图8 第一次跟踪获得相关峰

根据相关峰偏移量,将处理器中配置的本地码起始时间提早2个码片,再次仿真,获得正确的跟踪结果。其相关峰如图9所示。

图9 相关峰:起始时间修正后的跟踪结果

根据用户需要,还可以将相关峰绘图配置为准实时模式,自动上传相关值计算结果并绘图,类似于接收机监控软件监视相关峰的工作场景。

接收机对BDS该频点信号的捕获和跟踪完成,仿真试验结束。

4.3 仿真结果分析

通过以上仿真验证流程,完成了BDS某频点接收通道捕获和跟踪功能的快速仿真验证。相比ISim或NC-Sim仿真,Palladium平台的仿真速度有成倍数的提高,其方便灵活地触发条件设置功能使得仿真验证更加方便快捷,实验结果更加直观清晰。若仿真验证发现错误,修改代码后重新编译仿真也仅仅需要数分钟的时间,而ISE重新生成bit文件上板调试往往需要数小时甚至一天时间,相比之下其仿真测试的效率有了明显提高。此外还可通过改变信号模拟器的相关参数,方便地测试接收机在不同多普勒频移条件下的捕获性能等。以上实验的结果证明了采用Palladium仿真验证平台设计的可行性以及所验证的卫星导航接收机基带芯片捕获和跟踪的功能正确性。

5 结论

通过本文介绍以及实例讲解,体现了采用Palladium硬件加速器的卫星导航接收机通用验证平台设计的实用价值。该平台的搭建显著提高了数字接收机仿真验证效率,大大加快了导航接收机功能验证的速度。其灵活方便的触发条件配置和强大的波形查阅能力使得代码功能测试验证更加全面,特别是对于数字接收机基带处理芯片的开发,降低了芯片设计的风险,缩短了IC研发周期,确保了芯片原型设计的成功,加速产品的面世和升级。

[1] 杨津,张盛,林孝康.一款视频解码芯片的硬件仿真加速[J].电子器件,2010,33(5):565-567.

[2] 涂日玮.新体制GNSS信号捕获算法特性研究[D].哈尔滨:哈尔滨工业大学,2012.

[3] LIU Jing-nan.China’s Regional Compass System:12Satellites in 2012—ICD Next Year?[EB/OL].(2009-12-15)[2014-02-18].http://www.insidegnss.com/node/1697.

[4] 匿名.China Reveals Updated Compass/Beidou-2GNSS Signal Plan.[EB/OL].(2009-12-15)[2014-02-18].http://www.inside-gnss.com/node/1624.

[5] SLEEWAEGEN J M,WILDE W D,MARTIN H R.Galileo AltBOC Receiver[EB/OL].(2009-12-15)[2014-02-18].http://www.septentrio.com/sites/default/files/papers/GallileoAltBOC_paperFinal.pdf.

[6] BENTLEY B.Validating a Modern Microprocessor[J].Computer Aided Verification,2005(3576):2-4.

[7] 匿名.硬件仿真器成大规模IC 设计新宠[EB/OL].(2013-03-08)[2014-02-18].http://www.21ic.com/news/analog/201303/160027.htm.

[8] 江琦.Cadence推出INCISIVE PALLADIUM Ⅲ加速器/仿真器[EB/OL].(2006-12-07)[2014-02-18].http://news.eworks.net.cn/category8/news21727.htm.

[9] Cadence Design Systems,Inc.Cadence Palladium Series with Incisive XE Software:Hardware/Software Co-verification and System-level Verification[EB/OL].[2014-02-18].http://www.cadence.com/rl/resources/datasheets/incisive_enterprise_palladium.pdf.

[10] 徐健,罗天柱.CADENCE硬件仿真器在 Ethernet交换芯片验证中的应用[J].中国集成电路,2005(76):76-78.