基于HMC703锁相环的X波段线性扫频源设计与实现*

2013-12-29秦聚超

秦聚超,姜 弢

(哈尔滨工程大学信息与通信工程学院,哈尔滨150001)

线性扫频源是调频连续波雷达系统(Frequency Modulated Continuous Wave Radar System)的核心,其性能将直接影响系统整体性能[1-3]。采用分立元件制作的线性扫频源,为了提高线性度,加入了很多控制器,导致线性扫频源系统很复杂、体积大,线性度一般为±5%左右,量产与调试比较困难,在很多的场合不能满足要求[4-5]。采用锁相环技术设计扫频源具有输出频率高,频率稳定度高,相位噪声低,线性度高,杂散抑制好等优点。因为采用集成器件,此线性扫频源体积很小,加入负反馈,这样可以使扫频源的线性度达到千分之几,可以满足大部分扫频雷达的要求。

本文提出了一种基于锁相环HMC703线性扫频源的设计方法。与用分立器件实现线性扫频源相比,此线性扫频源具有电路结构简单,体积小,调试工作量小,抗干扰能力强等特点。

1 HMC703的基本工作原理

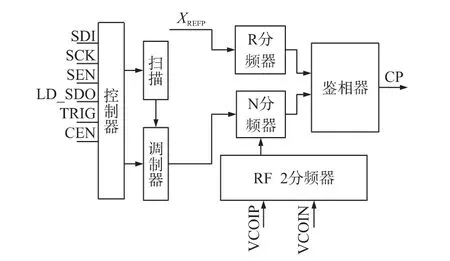

HMC703的原理框图如图1所示,它由控制器部分,扫描控制部分,调制器,可编程R分频器,可编程N分频器,鉴相器,RF 2分频器和电荷泵组成。当输入信号小于4 GHz时,RF 2分频器不使能,当输入信号大于4 GHz,并且小于8 GHz时,RF 2分频器需要使能。HMC703工作原理为:由芯片外部提供的参考信号FREF通过XREFP引脚输入,经过R分频器分频后输入到鉴相器,作为鉴相器的参考信号,即频率合成器的鉴相频率FPFD。VCO信号经过VCOIN引脚,进入一个可程控制2分频器,然后进入N分频器得到FN,FN与鉴相频率FPFD进行比较,两者的相位差转换为与之成比例的脉冲输出,经过电荷泵输出控制信号。从CP引脚输出的脉冲通过芯片外的环路滤波器积分后滤除鉴相杂散信号,变为带有相位误差的鉴相控制信号,并输入到VCO的电压控制端,从而使VCO锁定在固定的频率。

图1 HMC703原理框图

HMC703工作电源电压为3.3 V,电荷泵工作电压为5 V,最高鉴相频率为115 MHz,射频输入功率为-15 dBm~-3 dBm,参考信号输入功率一般为6 dBm。HMC703可以工作在整数模式和小数模式,有着很好的相位噪声系数。内部寄存器读写具有双重缓冲,使频率控制更加精确,通过控制寄存器可以很方便的实现线性扫频,FSK调制,PSK调制。精确工作模式下,它内部的24 bit的小数频率调制器可以实现0频差。它内部没有集成VCO,因而使用很灵活,价格也比较低。

2 HMC703的工作模式

HMC703可以工作在整数模式,小数模式,精确频率模式,FM调制模式,PM调制模式,扫频工作模式,除了整数模式外,其他工作模式都应该开启小数模式。小数工作模式可以得到很好的频率步进,精确频率模式可以使小数模式频率的误差为0。FM,PM工作模式可以用在简单的通信工作中,通信速率由锁相环环路滤波器决定。扫频工作模式支持单向扫频,双向扫频,也支持用户自定义扫频,主要应用在FMCW雷达系统中。

根据不同的工作模式,辅助寄存器Reg 0Ah,Reg 0Ch,Reg 0Dh将被使用,如表1所示。

表1 工作模式

HMC703的工作模式很多,在线性扫频源中,我们只用到了扫频功能,故本文只介绍小数工作模式和自动双向扫频模式,掌握这两种工作模式其他功能也就可以很容易的实现。

2.1 小数工作模式

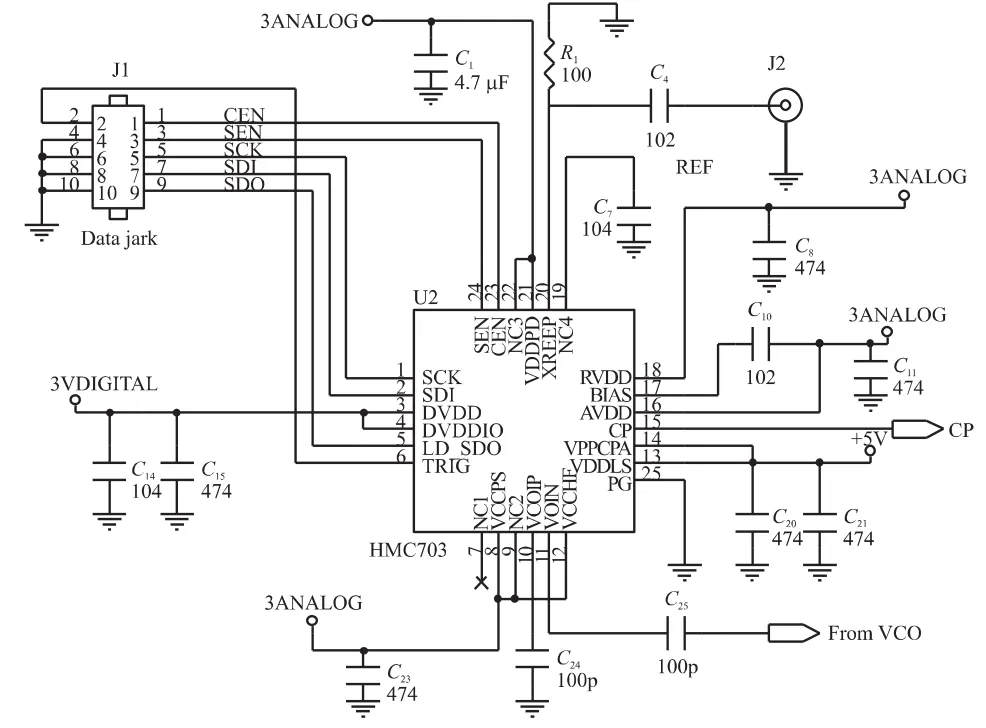

通过置 SD_MODE(Reg 06h[7:5])=0,HMC703工作在小数工作模式,计算VCO输出频率公式由下给出:

其中fps为通过 RF 2分频器后的频率;fvco为HMC703 RF引脚的频率;k为当RF 2分频器使能时,k=2,否则为1;Nint为整数分频比,为Reg 03h的值;Nfrac为小数部分,为Reg 04h的值;R为参考频率分频比;fxtal为参考信号频率。通过计算,只要将Reg 03h,Reg 04h数据写入HMC703,就可以输出相应的频率。

2.2 扫频工作模式

扫频工作模式分为自动双向扫频模式,触发双向扫频模式与触发单向扫频模式。为用户提供丰富的选择,使设计更加灵活。

自动双向扫频模式下,第一次触发发后,信号频率先由低到最高,当频率达到最大值时,又自动变到最低,然后自动循环,如图2所示。

HMC703扫频配置方法应该按下面的顺序配置

(1)使HMC703工作在小数模式(Reg 06h[7:5]=0)。

(2)确定起始频率,计算开始N,对 Reg 03h,Reg 04h进行编程。

(3)确定步进大小,计算终止N,对 Reg 0Ah,Reg 0Ch,Reg 0Dh 编程。

(4)改变 HMC703工作模式,Reg 06h[7:5]=5,6 或7。

注意:结束的N一定要正好等于起始的N加上步进的整数倍。

图2 自动双向触发扫频模式

3 线性扫频源参数设计

对于基于HMC703线性扫频源而言,系统设计主要是确定锁相环的参考输入频率XREF、鉴相频率FPFD、前置预分频器R、分频器N的大小,辅助寄存器大小以及有源环路滤波器参数。本文设计的线性扫频源输出扫频范围为10.45 GHz~10.85 GHz,相位噪声优于-85 dBc/Hz@10 kHz,杂散抑制优于-60 dBc,线性度优于0.3%。

从系统噪声上考虑,锁相环对系统噪声系统的影响为:

根据线性扫频源的系统求,设计的各参数为:工作模式为双向自动扫频模式,FREF=50 MHz,FPFD=50MHz,扫频时间为1 ms。结合HMC703的datasheet资料,确定reg 0~reg9,regA~regF的各寄存器值如表2所示。

表2 各寄存器值

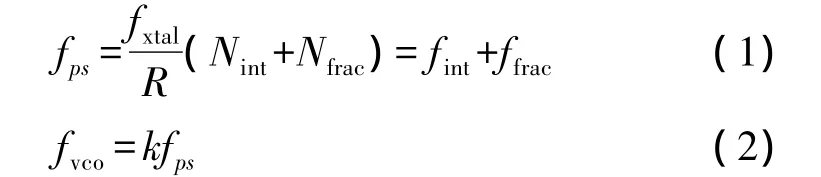

4 有源环路滤波器仿真设计

环路滤波器是一个低通滤波器,用来滤除高频杂散信号,对系统相位噪声,系统稳定度有着重要作用[6-7]。由于HMC513调谐电压范围为0~13 V,而HMC703电荷泵输出电压范围为0~5 V,故需要采用有源环路滤波器扩大锁相环输出的电源范围[8-13]。有源环路滤波器采用HITTITE公司提供的Hittite PLL Design Software进行设计。经过优化后的环路滤波器仿真图如图3所示,图中环路滤波器参数为:C1=1 nF,C2=22 nF,R2=330 Ω,R3=330 Ω,C3=560 pF,R4=33 Ω,C4=4.7 nF,Rb1=1 k Ω,Rb2=1 k Ω。从图4可以看到,在5.4 GHz(10.8 GHz二分频输出)在10 kHz时,相位噪声约为-106 dBc/Hz@10 kHz。

图3 有源环路滤波器仿真电路图

图4 5.4 GHz(10.8 GHz 2分频后得到)相位噪声仿真图

5 系统实现

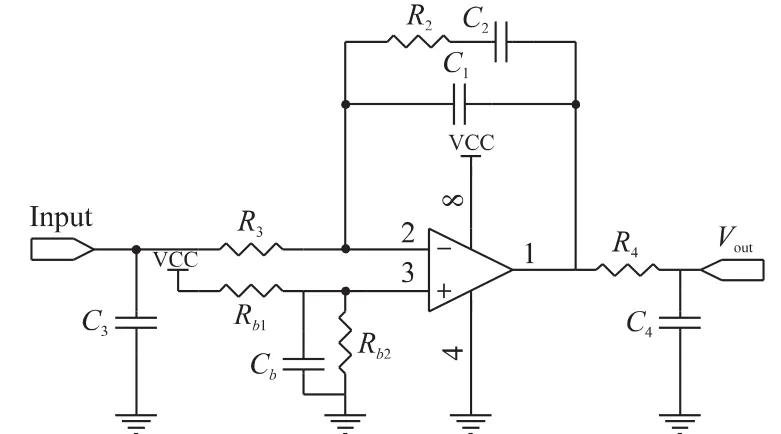

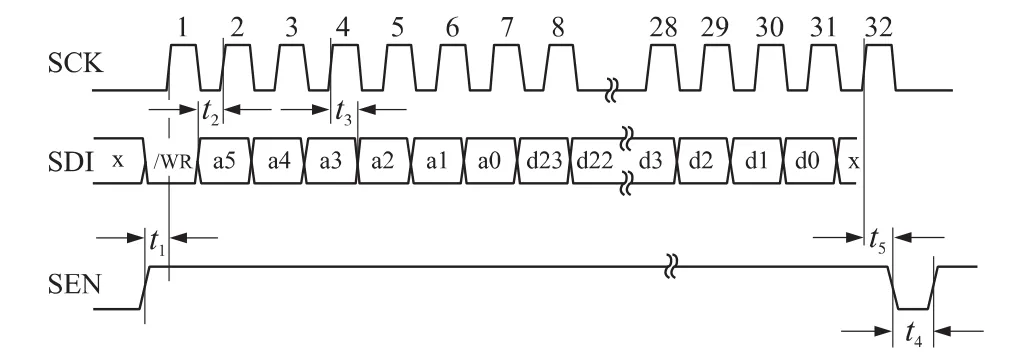

基于HMC703线性扫频源与ARM(stm32f107)控制器接口如图5所示,图中ARM的一个SPI口与HMC703的 SCK,SDI,SDO相连,ARM 的两个普通IO口与HMC703的CEN,SEN相连。SCK为SPI串行时钟输入,SEN为SPI使能端,高有效。SDI为串行数据输入。SDO为串行数据输出,同时也可以通过配置内部寄存器,输出不同的内部信号。HMC703有两种写入时序,本文采用标准的HMC Model,图6为数据写入寄存器的时序图。在SEN的上升沿选通SPI口,第1个时钟的上升沿,如果SDI为低电平,则为写操作,如果为高电平,则为读操作。后续在SCK上升沿到来时,SDI从MSB开始依次写入,其中前六位为寄存器地址,后24 bit为寄存器值,的最后一位无效位,共32 bit数据,LSB写入之后,SEN变为低电平,关闭SPI接口。

图5 线性扫频源HMC703连接原理图

图6 写入时序图

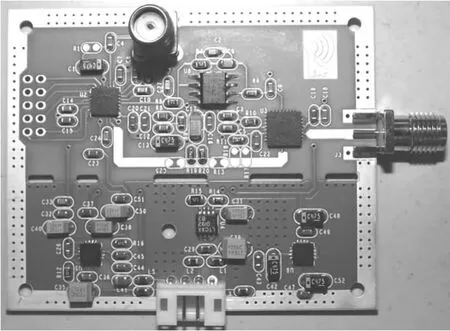

图7 实物图

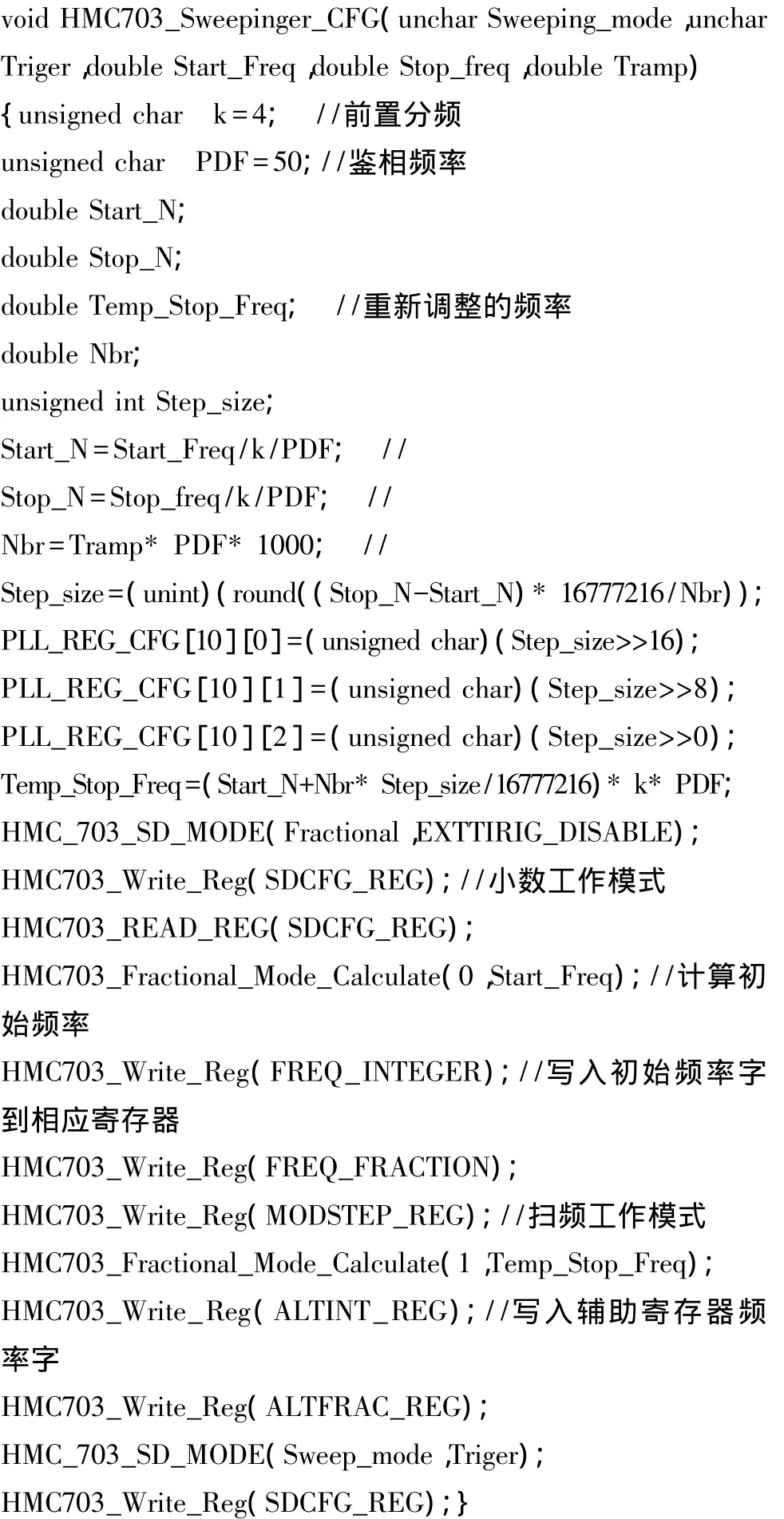

由于HMC703功能很多,限于篇幅,本文仅给出了HMC703扫频工作模式时各寄存器的计算程序。

参考程序为:

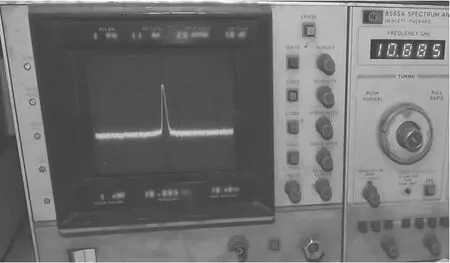

6 性能测试

频谱分析仪中心频率为10.8 GHz,首先测试单频时的工作,如图8所示,在单频小数模式下输出10.8 GHz信号。然后在双向扫频模式下测试,因为线性扫频源的扫描时钟与与频谱分析仪的扫描时钟不同步,所以导致测试现象为一系列分立的谱线,测试结果如图9所示。

图8 小数模式单频点测试

图9 自动双向扫频模式测试

7 结论

本文介绍了HMC703锁相环与HMC513压控振荡器与ARM控制器STM32F107设计的10.45 GHz~10.85 GHz线性扫频源的设计过程与设计方法,给出了有源环路滤波器的设计方法,通过硬件电路的制作与调试,实现了一个体积小,结构简单,性能较好的线性扫频源。

[1]Cotter W Sayre.无线通信设备与系统设计大全[M].张之超,黄世亮,吴海云,等译.北京:人民邮电出版社,2004:204-216.

[2]周宏雷.低相噪Ku波段频率合成器研究[D].成都:电子科技大学,2008:125-178.

[3]王铁.基于DDS+PLL技术的高性能频率源研究与实现[D].长沙:国防科技大学,2004:23-45

[4]恽小华,周白华,张国春.毫米波宽带超线性扫频源[J].电子学报,1996,24(2):100-103

[5]陈小清,李磊民.基于DDS+PLL的宽带扫频源的设计与实现[J].通信技术,2010,43(3):188-190

[6]迟忠君,徐云,常飞.频率合成技术发展概况[J].现代科学仪器,2006(3):21-24

[7]刘长明,陈叶民.有源环路滤波器的设计分析[J].无线工程,2009,39(12):37-39

[8]刘界.宽容环路滤波器的设计[D].南京:东南大学,2006:7-9

[9]王照峰,王仕成,苏德伦.锁相环电路的基本概念及应用研究[J].电气应用,2005,24(8):46-48

[10]徐述武,王海勇,唐云峰.基本ADF4350锁相频率合成器的频率源设计与实现[J].电子器件,2010,33(6):725-729

[11]刘丽平.锁相环中环路滤波器的设计与ADS仿真[J].信息通信,2010(4):28-29

[12]张珂勇.基本AD4111的锁相环频率合成器设计[J].电子设计工程,2012,20(24):81-83

[13]Carlosena A,Manuel-Lazaro A.General Mehtod for Phase Lock Loop Filters Analysis and Design[J].IET Circuits Devices Syst,2008,2(2):250-256