一种改进的被动型铷原子频标伺服电路

2013-12-23雷海东

雷海东

(江汉大学 物理与信息工程学院,湖北 武汉 430056)

0 引言

物理系统是被动型铷原子频标的核心部件,它提供一个频率稳定、线宽较窄的原子共振吸收线。经综合调制后,电子线路产生的源于石英晶体振荡器的带调制微波探询信号作用于物理系统,经量子鉴频后,通过伺服电路对量子鉴频信息的处理,最终将本振的输出频率锁定在铷原子的基态超精细0-0 跃迁中心频率上。现有大多数伺服电路根据综合提供的同步鉴相信号对量子鉴频信号进行同步鉴相,并根据鉴相结果信息采用独立的D/A 压控本振的方式实现整机的闭环锁定,最终通过本振输出稳定度较高的频率信号[1-2]。当微波探询信号位于原子吸收线宽范围内时,这样的方式是较理想的,但在实际应用中,由于具体所选的本振类型以及温度系数不同,在铷原子频标故障更换本振时,以及在不同的环境下每次上电时,本振本身每次输出的频率并不是固定不变的,有时会导致电子线路预置的微波探询信号的频率离原子共振吸收峰的峰值频率较远,使现有伺服电路实现整机闭环锁定的时间变长,甚至可能会使原子频标整机无法正常实现闭环锁定[3]。

随着直接数字合成DDS 技术的日益成熟,再加上其良好的信噪比输出,很多研究人员已经将DDS 技术应用于被动型铷原子频标综合调制领域,并且已经取得较好的实验与应用结果。鉴于此技术方案的成功,在被动型铷原子频标小型化、轻量化应用的趋势下,采用数字化DDS 与处理器芯片,将原子频标伺服环节与综合环节有机地综合起来,以一种小型化的结构改进现有电路的功能,实现整机的闭环锁定。

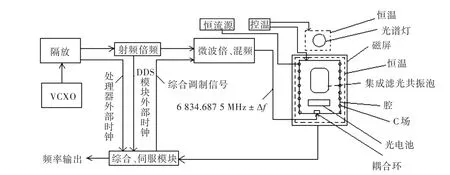

1 整机原理

集成化的综合、伺服单元应用于被动型铷原子频标的整机结构原理如图1 所示。压控石英晶体振荡器(VCXO)输出的10 MHz 频率信号经隔放处理后其中一路送至射频倍频单元,进行×16 次信号倍频处理,将得到的160 MHz 射频信号送至微波倍频、混频单元以及综合、伺服模块。隔放的另一路10 MHz 信号送至综合、伺服模块,经综合、伺服模块中的综合信号处理单元得到45.312 5 MHz±Δf 调制信号并送至微波倍频、混频单元。在微波倍频、混频单元中,对160 MHz射频信号及45. 312 5 MHz ± Δf 综合调制信号再分别作× 43 次信号倍频及混频处理,最终得到(160 MHz×43)-45.312 5 MHz± Δf =6 834.687 5 MHz±Δf 微波探询信号作用于物理系统,经物理系统对微波探询信号的量子鉴频处理后,将量子鉴频信号再反馈给综合、伺服模块,通过同步鉴相处理后,根据具体的量子纠偏信息来修改综合调制信号的频率值,最终实现整机的闭环锁定。

图1 整机结构原理图

2 综合、伺服模块

综合、伺服模块的结构如图2 所示。经隔放处理后的10 MHz 频率信号送至处理器的外部时钟输入端(XTAL),作为处理器工作时的时钟参考。处理器分别产生3 路相位关系可调整的方波信号,其中一路79 Hz 键控调频信号送至DDS1 的FSK 键控调频输入端口,一路79 Hz 同步鉴相参考信号用作同步鉴相,一路4 倍频调制信号用作锁定检测。经射频倍频得到的160 MHz 频率信号送至DDS1 的外部时钟基准输入端(RefClk),用作DDS1 工作时的参考时钟。通过处理器与DDS1间的串行通讯时序,DDS1 根据FSK 端处理器送来的79 Hz 键控调频方波信号的高、低电平状态分别选取内部48 位频率控制寄存器(F1、F0)中处理器输入的综合调制分频数值预置频率作为输出,从而产生原子频标综合环节中所需的45. 312 5 MHz ± Δf 调制信号输出。预置的两个频率控制寄存器F1、F0 中的频率差值Δf 则决定了微波探询信号调制深度的大小。与处理器控制DDS1 产生综合调制信号的原理类似,处理器通过串行通讯时序,将同样的分频数值传递给DDS2,产生不带调制的45. 312 5 MHz 频率信号输出。将DDS2 得到的45.312 5 MHz 频率信号送入DDS3 的外部时钟基准输入端(RefClk),用作DDS3 工作时的参考时钟。处理器根据串行通讯时序,将相应的整机频率输出数值传递给DDS3,从而得到原子频标整机频率信号输出。

图2 综合、伺服模块原理图

由于DDS1 及DDS2 的外部参考时钟信号频率为160 MHz,而综合调制产生的调制信号为45. 312 5 MHz,故对DDS1、DDS2 编程时不使用其内部的PLL 倍频模块,这样可以提高输入输出信噪比。处理器对DDS1、DDS2 分频数值输入编程时,按照下式进行设置:

式中f0为DDS 外部参考时钟信号的频率(如160 MHz),f 为预置在内部48 位频率控制寄存器F1或F0 中的信号频率(如45. 312 5 MHz),D 为处理器对DDS 输入的具体综合调制分频数值,以f = 45. 3125 MHz,f0= 160 MHz 为例,对应的数值D 为(45. 312 5 MHz/160 MHz)×248。将所得到的十进制值转化为二进制对应48 bits 的频率控制寄存器的值。根据相应的串行通讯时序,通过处理器将相应的48 bits 值写入DDS 缓冲区后,在DDS 的输出引脚端将会产生频率为45.312 5 MHz的综合调制信号输出。

将DDS2 产生的45. 312 5 MHz 频率信号送入DDS3 的外部时钟参考端,用作DDS3 工作时的参考时基。处理器根据(1)式将原子频标预置的10 MHz 整机输出频率值以二进制bit 的方式通过串行通讯时序送入DDS3 的缓冲区,使其在输出端产生相应的整机频率信号输出。由于DDS3 的外部参考时基采用DDS2 产生的综合调制频率信号,故在本方案中,当伺服环路得到相应的量子纠偏信息后,会修改相应的DDS2 的综合调制信号的频率,这样亦会引起DDS3 整机输出信号的频率发生变化,即替代了传统的通过D/A 压控晶振的方式来改变本振的输出频率值。值得注意的是,对于整机输出频率信号采用了直接数字合成的方式,使得原子频标在一定应用范围内充当了一个稳定度较高的综合器角色。用户可以根据实际应用中的要求,通过图2 中用户输入端口,方便地修改DDS3 的整机输出信号的频率值。

带调制的微波探询信号经过物理系统的量子鉴频处理后得到的量子鉴频信号送至处理器,处理器根据4 倍频调制信号(79 Hz × 4)对量子鉴频信号进行采集处理,判定此时刻所加的微波探询信号的频率与原子跃迁中心频率的关系,即判断此时刻微波探询信号的频率处于原子吸收线宽的锁定范围之内还是处于脱锁状态。

3 锁定判断

锁定判断的依据如图3 所示[4-5]。

图3 锁定检测原理图

图3 所示分为4 种情况:①微波探询信号的频率大于(小于)原子跃迁中心频率且在原子吸收线宽范围之内时,即f >fo(f <fo) ,经量子鉴频、光检放大、方波整形后得到的信号频率均与原来处理器产生的送至DDS1 键控调频输入端FSK 的79 Hz 调制信号的频率一致,只是由于原子驰豫时间及环路响应时间延时而存在相位上的差异,此时原子频标处于未锁定状态,出现图3 中所示的未锁定信号1 及未锁定信号2。②微波探询信号的频率等于原子跃迁中心频率时,即f = fo,方波整形后得到的信号频率是原调制信号的2倍,此时原子频标处于锁定状态,出现图3 所示的锁定信号。③微波探询信号的频率大大远离原子跃迁中心频率时,即f 未进入有效的量子鉴频吸收带宽范围之内,经处理后得到的信号将是一个持续的电平,此时原子频标处于脱锁状态。④另一种特殊的情况就是,在原子频标整机刚上电时(包含整机完全冷态上电与整机热态重新启动上电),光谱灯有一个张弛振荡的过程,此时从量子系统鉴频输出端会检测到高频无规律的信号波形,直至光谱灯进入正常工作状态,而整个张弛振荡过程持续时间由具体的整机冷态或热态决定。

对于这4 种情况,采用4 倍频调制信号采样时序的连续4 个上升沿作为触发脉冲,分别对量子鉴频后的信号进行电平采样,并分别记录为D1、D2、D3、D4。对于情况①,记录的4 个电平中有3 个低电平,1 个高电平;对于情况②,记录的电平有关系式D1=D3且D2=D4;对于情况③,记录的电平有关系式D1= D2=D3=D4;对于情况④,由于此时刻光谱灯处于张弛振荡过程,量子鉴频处的信号高频无规律,多组连续4个采样时序上升沿采样得到的数据中有可能会出现情况①或情况②或情况③,故无法通过采样电平进行判断。解决的方法是:由于在此环节中,所要判断的是原子频标是否处于锁定状态,情况④明显说明原子频标并未处于锁定,在综合调制信号部分,采用的调制信号是一个低频信号,具体方案中取79 Hz,在以连续4 个上升沿触发的4倍频调制信号频率的采样时序中,可以设置多于一组(连续4 个上升沿触发为一组)采样的判断方式,对多组采样得到的电平分别作原子频标锁定状态判断,并对多组判断做与运算,得到最终的锁定状态判断结果,这样就能够很好地解决情况④带来的问题。

4 闭环锁定

整个闭环锁定的时序判断图如图4 所示。

图4 锁定检测程序流程图

处理器根据4 倍频调制信号对量子鉴频信号进行采集处理判定锁定状态后,假如得到情况①和情况②的判断结果,则通过79 Hz 同步鉴相参考信号与量子鉴频信号作同步鉴相处理,判定微波探询信号的频率与原子跃迁中心频率的关系,并得到量子纠偏信息,通过小数值改变DDS1 输出的综合调制信号频率来最终实现原子频标的闭环锁定。假如得到情况③的判断结果,则说明此时刻微波探询信号的频率已经远离原子跃迁中心频率,即原子频标已经无法正常输出稳定的频率信号,此时刻通过大数值改变DDS1 输出的综合调制信号频率,达到大范围的频率拉偏目的。DDS1 具体的分频数值改变多少是以原子频标整机输出信号的频率稳定度为依据的。对于在某一固定采样时间T(s)内,以整个原子频标的输出信号(DDS3 输出)的频率稳定度为1 ×10-12来说,则DDS3 输出频率信号的频率绝对变化值为ΔfDDS3=10 MHz×(1×10-12)=10-5Hz,对于固定的用户预置的整机输出频率数值D ,通过(1)式可以方便地列出计算DDS3 环节中相应的外部时钟参考信号频率f 变化的计算公式:

可以求得相应的f = 45. 312 5 MHz ± 4. 5 × 10-5。对于DDS1 及DDS2 来说,外部参考时钟选用160 MHz,则其可控的最小的频率输出变化为160 MHz/ 248≈5.7 × 10-7,对于上述4.5 × 10-5综合调制信号频率的变化是可以满足的。

由于被动型铷原子频标的线宽通常在1 kHz范围,当整机处于脱锁状态时,微波探询信号的频率距离原子跃迁中心的频率要大于1 kHz,在某种故障状态时甚至会达到MHz 量级。在脱锁状态下,伺服系统需要大范围地拉偏微波探询信号的频率,即大范围地改变DDS1 及DDS2 输出的综合调制信号的频率值。具体的调整级别范围为:102、103、104、105、106Hz 等,通过处理器根据调整级别范围中从小至大的原则依次改变DDS1 及DDS2 的输出信号频率,每调整一次输出频率就检测此时刻原子频标所处的状态,直至出现如图3 所示的情况①或情况②才进入正常状态下的小数值频率纠偏,当实现整机的闭环锁定后,需要通过处理器同时更改DDS3 的整机输出频率数值,从而达到用户预置的输出信号频率。

5 结语

被动型铷原子频标因为其本身物理结构限制了其整机指标进一步提高的空间。针对现有成熟的原子频标技术方案,本文提出一种全新改进的伺服电路,通过原子频标本身现有的电子线路结构,从综合、伺服模块出发给出具体的改进方案,以克服现有被动型铷原子频标可能存在的产品缺陷。无论对于产品的性能提高,还是对于科研领域技术创新都有着比较明显的推动作用。

[1] 刘玉菲,高翔,吴亚明,等.不同原子频标的物理工作原理对比[J]. 微计算机信息:测控自动化,2006,22(4):170-172,158.

[2] 王义遒,王庆吉,傅济时,等. 量子频标原理[M]. 北京:科学出版社,1986:366-382.

[3] 刘淑琴,董太乾. 进一步提高Rb 原子频标频率稳定度的几点建议[C]//2001 年全国时间频率学术报告会论文集.成都:中国科学院国家授时中心,2001:75.

[4] Lei H D,Liu X D,Zhan Z M,et al.Study of lock instruction and fault detected based on the passive atomic frequency standard[C]//2011 International Conference on Multimedia Technology(ICMT). Hangzhou,2011:6043-6045.

[5] 雷海东. 数字移相在原子频标领域中的应用[J]. 江汉大学学报:自然科学版,2012,40(1):37-40.