32bit SOPC系统中SRAM的非常规使用*

2013-12-16李彬华陈小明

何 春,李彬华,陈小明

(昆明理工大学信息工程与自动化学院,云南 昆明 650504)

随着存储技术的发展,FPGA器件由于其低功耗、高性能、低成本和高可靠性等优点,在复杂逻辑电路和数字信号处理领域扮演着重要的角色,与其最为相关的是以FPGA芯片为核心,借助开发软件结合外设构成的嵌入式可编程片上系统(System-on-a-Programmable-Chip, SOPC)的应用。为了适应系统数据交换,FPGA系统开发板的典型应用都为主FPGA芯片配接闪存和外部随机存储器(Random Access Memory, RAM)的结构。闪存用来存储FPGA 配置信息和Nios II程序,配置信息和Nios II程序可于系统上电时,由FPGA内嵌的闪存配置控制器对FPGA芯片自动完成配置并引导程序在随机存储器中运行。随机存储器用于运行Nios II程序和处理任意类型数据,任意类型数据可以是以二进制方式存储的图像、声音数据等等。

近年来,国内外关于SOPC在天文成像和数据采集方面的应用越来越多。国外研究人员使用电子倍增电荷耦合器件(Electron-Multiplying Charge-Coupled Device, EMCCD)研制的相机,进行了微光成像实验,取得了极好的天文观测结果[1-2];国内研究人员也进行了大量的研究探讨,不仅是SOPC数据采集系统的构成[3-5],还把具体技术应用于实际,解决了不少非常实际的工程问题[6-9]。

本文以目前正在进行的一个基于EMCCD的成像系统研究项目中使用的系统板为例,介绍16位SRAM组件的设计过程及其在32 bit SOPC系统中的使用方法。

1 32位SOPC应用系统框架

为进行EMCCD成像系统的实验研究,设计了一块高速数模混合电路板,称为FPGA板。其模拟部分有非常重要的视频信号及其处理电路,数字部分主要由SOPC及其周边系统、图像和控制数据传输接口系统组成。SOPC及其周边系统框图如图1。系统使用Quartus II 8.0(32 bit)和Nios II 8.0(32 bit)作为软件开发平台。

图1 FPGA板SOPC及其周边系统框图

Fig.1 Schematic diagram of an SOPC and its interfaces in the FPGA board

该系统用于高速模拟视频信号的处理和模拟/数字(Analog-to-Digital, A/D)转换、CCD时钟的产生、相机的控制和图像数据传输等,是一个典型的高速低噪声数模混合系统。考虑到低噪声的要求,希望在保证相机控制和数据传输可靠性的前提下,尽量减小数字系统所占的比重。所以,要求电路板上的FPGA芯片及其周边电路规模不要太大。FPGA工作频率较高,成像控制与A/D转换、数据传输、测试和功能扩展等端口占用了FPGA芯片大量的I/O资源,从系统可靠性和芯片管脚资源的合理分配利用出发,FPGA板使用了单片IDT71V416S10作为扩展随机存储器。由于 IDT71V416S10为16位静态随机存储器芯片,不需要附加刷新控制,芯片的数据交换和控制端相对较少,利用FPGA一个独立的I/O组就可以对其进行控制并完成数据交换,方便在电路板的设计走线上对线路分布参数、阻抗匹配等问题进行处理,能够有效抑制数字信号传递过程中的开关噪声等问题,在满足系统工作需求的同时,节省了FPGA的I/O资源,也可以适应FPGA芯片中构建的SOPC系统与扩展随机存储器间进行高速数据交换。FPGA板的配置信息和Nios II程序存储在串行FLASH存储器芯片上。其他外围常规接口和I/O结构,不再赘述。

Quartus II默认的内嵌式SOPC系统为32位结构,常规使用方法是利用两片IDT71V416S10构成32位扩展随机存储器,而且内建的SRAM组件没有数据位宽的调整项,若FPGA板采用单片IDT71V416S10作为扩展随机存储器,在创建SOPC器件框架时不能使用SOPC组件库提供的成型组件,必须按照Avalon总线规范自行构建其框架。

2 16位SRAM组件设计

由Avalon总线规范[10-11]知道,Avalon总线拥有多种传输模式,以适应不同外设的要求。Avalon总线的基本传输模式是在一个主外设和一个从外设之间进行单字节、半字或字(8、16或32位)的传输。Avalon总线还支持一些高级传输模式和特性,例如支持需要延迟操作的外设、支持需要流传输操作的外设以及支持多个总线主设备并发访问。

IDT71V416S10容量=218×16=262 144×16=4 194 304 bit,即256 k×16=4 Mbit。

该芯片为18位地址、16位数据宽度的SRAM。在32位SOPC系统中Avalon总线可以直接对低16位或低几位总线进行读写,扩展随机存储器在符合Avalon总线规范的情况下,可以定义为不同的数据位宽。

2.1 SRAM的Verilog HDL框架程序设计

SOPC系统所用组件的设计,需要先构建其框架,然后才能进行组件创建。框架通常是使用某一种硬件描述语言(Hardware Description Language, HDL)编写的程序实现的。本文使用Verilog HDL构建16位SRAM的框架程序。为增加程序的可读性,约定:SRAM组件与SOPC内部系统时钟、复位和Avalon总线的关联信息,端口描述用小写字母表示;SRAM组件输出与实际SRAM芯片的关联信息,端口描述用大写字母表示。该程序命名为SRAM_16bit.v,其实体描述了必要的端口信号连接关系和数据写入规则。具体程序如下:

module SRAM_16bit

#(

parameter DATA_LEN=16, //数据位宽定义

parameter ADDR_LEN=18 //地址位宽定义

)

(

//自定义SRAM组件与系统时钟、 复位关联的端口

input clk,

input reset_n,

//自定义SRAM组件与avalon_slave关联的端口

input [(ADDR_LEN-1): 0] address,

input [(DATA_LEN/8-1): 0] byte_n, //字节使能信号byteenable_n

input write_n,

input [(DATA_LEN-1): 0] writedata,

input read_n,

output [(DATA_LEN-1): 0] readdata,

//自定义SRAM组件输出端口, 用于连接IDT71V416S10芯片

inout [(DATA_LEN-1): 0] SRAM_DATA,

output [(ADDR_LEN-1): 0] SRAM_ADDR,

output [(DATA_LEN/8-1): 0] SRAM_BE_N,

output SRAM_CS_N,

output SRAM_OE_N,

output SRAM_WE_N

);

//数据读出、写入规则和信号连接

assign SRAM_DATA=SRAM_WE_N? ′hz: writedata; //数据写入规则

assign readdata=SRAM_DATA;

assign SRAM_ADDR=address;

assign SRAM_BE_N=byte_n;

assign SRAM_WE_N=write_n;

assign SRAM_OE_N=read_n;

assign SRAM_CS_N=read_n & write_n; //CS片选有效规则

endmodule

端口描述中,字节使能信号byteenable_n可以控制对符合规范位宽的SRAM进行写操作。由Avalon总线规范,写入规则参考表1。

表1 字节使能信号对从端口的写入控制

SRAM_16bit.v程序中数据位宽DATA_LEN定义为16位时,byteenable_n位宽为2,这样Avalon主端口只能对从端口的低16位进行控制;DATA_LEN定义为32位时,byteenable_n位宽为4,Avalon主端口可以对从端口的满32位进行控制。

SRAM数据的读取遵循基本读传输方式,只要SRAM被选中和/或地址发生变化,SRAM就立刻返回数据。

SRAM_16bit.v程序中数据读出和写入规则的制定可参考IDT71V416S10数据手册中控制端与输出功能真值表[12]。数据线上的数据在读写状态切换瞬间如不处理会出现混乱,为避免读写操作发生冲突,读写转换过程中需使数据线呈高阻态,参见程序中数据写入规则。写和读的时候,SRAM芯片的片选必须有效,故取低电平有效的读和写相“与”,参见程序中CS片选有效规则。

2.2 16位SRAM组件创建

完成器件的框架程序设计后,就需要在Quartus II中创建SOPC器件,以便在Quartus II工程中进行调用。在SOPC Builder工作界面下,创建新的组件(Create new component……),加载SRAM_16bit.v文件,若程序校验无误,可在信号定义选项卡(Signals)中定义信号关联,如图2。

图2 SRAM信号关联定义

Fig.2 Definitions of the SRAM signals associated with interfaces

接下来需要根据端口的使用情况,在接口设置选项卡(interfaces)中增加端口或是删除无信号关联的多余端口并进行端口特性的设置。其中时序参数(Timing)的设置,必须参考实际器件的技术数据手册中器件的读/写时序,认真选取相应参数。IDT71V416S10的读/写时序如图3、4[12],其平均读写时间周期为10 ns,即tWC=tRC=10 ns,数据输出保持时间tOH=4 ns,输出使能等待时间为5 ns。这样,在时序参数设置中设定的参数取值如下:Setup=5 ns;Read Wait≥tRC+tOH(参考图3)。参照已设定的Hold参数,取Read Wait=tRC+Hold=20 ns;Write Wait≥tWC=10 ns(参考图4),取Writer Wait=10 ns;tOH=4 ns,为保证系统读出数据可靠,取Hold=10 ns。

图3 IDT71V416S10读时序[12]

Fig.3 Timing diagram of the read cycle of the IDT71V416S10[12]

图4 IDT71V416S10写时序[12]

Fig.4 Timing diagram of the write cycle of the IDT71V416S10[12]

另外,若要SOPC器件中的中央处理器(Central Processing Unit, CPU)可以将该SRAM作为扩展随机存储器使用,还必须在接口设置选项卡(interfaces)中在不推荐参数设置(Deprecated)中把Memory device项选上。最后在组件向导(Component Wizard)中填入包括组件名称、分组等信息后,可形成SOPC器件的新组件。

一个含16位SRAM的SOPC器件的局部框架如图5。新建的SRAM组件内建立了与中央处理器时钟的关联,可以直接工作,不必挂接avalon三态桥(avalon-MM Tristate Bridge)。

图5 包含16bit SRAM的SOPC器件局部框架

Fig.5 A part of the framework of the SOPC device with the 16bit SRAM

3 测试结果及应用说明

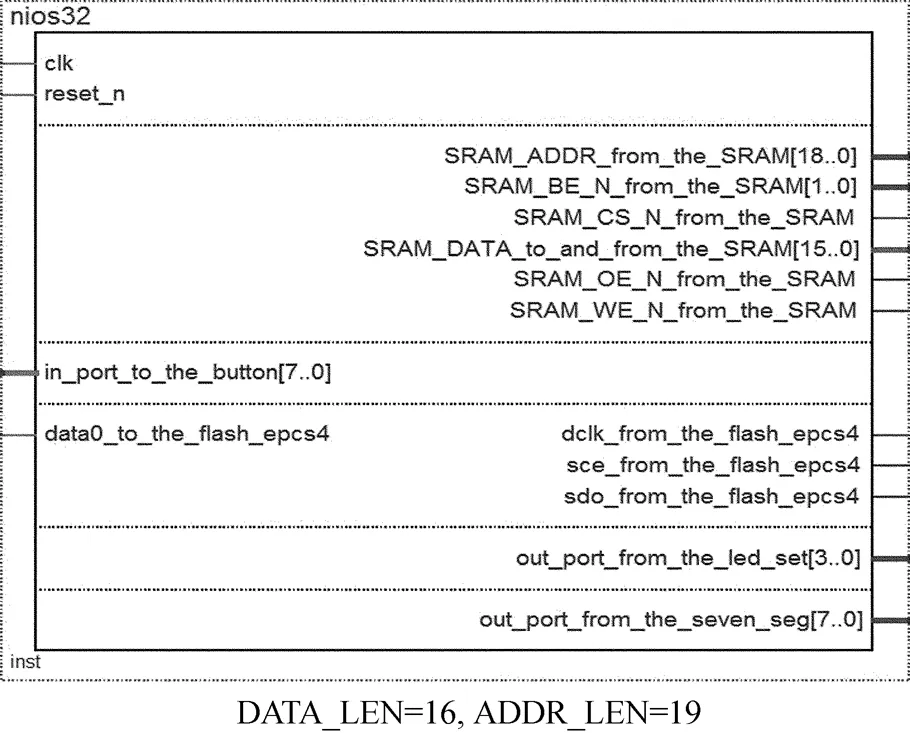

按照图5框架结构在Quartus II中形成的SOPC器件见图6,利用此器件形成的工程下载到FPGA板后,系统板上电加载Nios II程序对预设输入和输出响应正常,系统顺利工作运行。

此后,将一个EMCCD相机控制工程[13]下载到FPGA板,用示波器测得的相机时钟和控制波形的一部分如图7。该实测波形与仿真波形[13]一致,说明包括该16位SRAM在内的所有SOPC系统均工作正常。

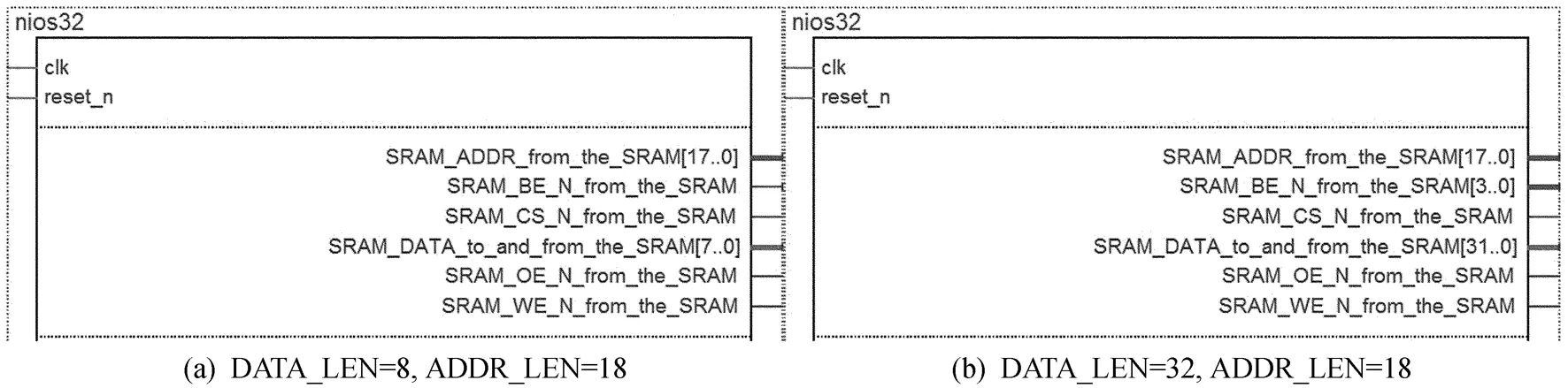

由于SRAM_16bit.v中存储器地址和数据位宽作了参数化处理,故其也可用于2片IDT71V416S10构建的256 k×32 bit的系统或类似SRAM芯片构建的其他系统。数据位宽不变,改变地址让ADDR_LEN=19,系统可使用512 k×16 Bit的芯片,见图8。固定地址,让数据位宽DATA_LEN为8或32,系统可使用256 k×8 Bit的芯片或256 k×32 Bit的芯片,见图9。

图6 Quartus II中使用的SOPC器件

Fig.6 An SOPC device used in a Quartus II test project

图7 实测的EMCCD相机时钟和控制波形

Fig.7 Measured waveforms of clocks and control signals in an EMCCD camera

4 结束语

本文针对天文用EMCCD相机项目的FPGA板上使用的16位扩展SRAM芯片,介绍了在Quartus II的SOPC开发系统中按照Avalon总线规范定制非常规位宽扩展随机存储器组件的方法,并在实际项目的FPGA板上进行了实验验证。按此思路,用户可根据实际情况和需要,对其他外设定制类似的SOPC组件,以构建合理且有效的SOPC系统。

图8 SRAM组件改变地址参数后的SOPC器件

Fig.8 An SOPC device after modifying address parameters of the SRAM

图9 改变SRAM组件数据位宽参数后的SOPC器件局部

Fig.9 SOPC devices with different data widths of the SRAM

[1] Mackay C D. Near diffraction limited visible imaging on 10M class telescopes with EMCCD[C]// J E Beletic, J W Beletic, P Amico. Scientific Detector for Astronomy. Springer, 2006, 336: 93-98.

[2] Downing M, Hubin N, Kasper M, et al. A dedicated L3Vision CCD for adaptive optics applications[C]// Beletic J E, Beletic J W, Amico P. Scientific Detector for Astronomy. Springer, 2006, 336: 321-328.

[3] 林鹏, 姚耐军, 郝庭柱, 等. 基于SOPC数据采集系统的研究[J]. 天津理工大学学报, 2006, 22(3): 39-41.

Lin Peng, Yao Naijun, Hao Tingzhu, et al. Study on the data collection system based on SOPC design[J]. Journal of Tianjin University of Technology, 2006, 22(3): 39-41.

[4] 姚国国, 李宝森, 王景贤, 等. 基于SOPC技术的数据采集系统设计[J]. 电子科技, 2008, 21(10): 68-71.

Yao Guoguo, Li Baosen, Wang Jingxian, et al. Design of the data acquisition system based on SOPC[J]. Electronic Science and Technology, 2008, 21(10): 68-71.

[5] Li B, Hu K, Wang Ch, et al. Data acquisition system based on the Nios II for a CCD camera[C]// Proceedings of SPIE, 2006, 6274: 62741C.

[6] 邱志强, 邓建, 叶彬浔, 等. 基于NiosⅡ嵌入式软核处理器的天文用IRFPA图像采集系统[J]. 天文研究与技术——国家天文台台刊, 2006, 3(4): 373-379.

Qiu Zhiqiang, Deng Jian, Ye Binxun, et al. Astronomical IRFPA image collecting system based on the Nios II soft-core embedded processor[J]. Astronomical Research & Technology——Publications of National Astronomical Observatories of China, 2006, 3(4): 373-379.

[7] Li B, Song Q, Ji K, et al. Method to implement the CCD timing generator based on FPGA[C]// Proceedings of SPIE, 2010, 7742: 77421Y.

[8] 和琳, 李彬华, 尚媛圆, 等. 行间转移CCD数字系统的VHDL设计[J]. 天文研究与技术——国家天文台台刊, 2010, 8(4): 380-387.

He Lin, Li Binhua, Shang Yuanyuan, et al. A VHDL design of digital system for an interline-transfer CCD[J]. Astronomical Research & Technology——Publications of National Astronomical Observatories of China, 2010, 8(4): 380-387.

[9] 朱丹, 王家宁, 朱玙骅, 等. 一种多核远程重构控制器的设计与实现[J]. 计算机工程, 2011, 37(9): 254-256.

Zhu Dan, Wang Jianing, Zhu Yuhua, et al. Design and Implementation of multi-core remote reconfigurable controller[J]. Computer Engineering, 2011, 37(9): 254-256.

[10]Altera Corporation. Avalon bus specification reference manual[EB/OL]. [2012-02-19]. http://www.altera.com.cn/literature/manual/mnl_avalon_bus.pdf.

[11]孙恺, 程世恒. Nios II系统开发设计与应用实例[M]. 北京: 北京航空航天大学出版社, 2007.

[12]Integrated Device Technology Inc. IDT71V416L10BEG Datasheet[EB/OL]. [2012-02-19].http://pdf1.alldatasheet.com/datasheet-pdf/view/124915/IDT/IDT71V416L10BEG.html.

[13]陈小明, 李彬华. EMCCD时序发生器的VHDL设计[J]. 计算机工程与应用, 2012, 48(1): 72-75.

Chen Xiaoming, Li Binhua. VHDL design of EMCCD timing generator[J]. Computer Engineering and Applications, 2012, 48(1): 72-75.