基于VMM的LTE 小区搜索模块验证

2013-12-14郑建宏

郭 旭,郑建宏

(重庆邮电大学通信与信息工程学院,重庆400065)

0 引言

摩尔定律指出,芯片上集成电路的数量每隔十八个月翻一倍。近年来,在百万门级ASIC项目的研发过程中,验证工作占用了大部分的设计开发时间。随着芯片设计复杂度的不断提高,功能验证的复杂度也以指数增长,功能验证已经成为了芯片研发的瓶颈。因此,如何提高芯片验证的效率,已经变得越来越重要。

SystemVerilog语言建立在Verilog语言的基础上,是IEEE Std 1364-2001 Verilog标准的扩展增强,并兼容Verilog2001,已经成为了新一代硬件设计和验证语言[1]。VMM(verifacation methodology manual)是Synopsys公司推出的基于SystemVerilog的验证方法学,已经得到了业内的广泛推广 。基于VMM验证方法学搭建起来的验证平台具有良好的结构性和可重用性,大大缩短了搭建验证平台所花费的时间。同时,VMM验证方法学支持带约束的随机激励生成、自动对比数据以及功能覆盖率驱动等功能,提高了验证的完备性和验证的效率,缩短了芯片的开发周期。

1 SystemVerilog和VMM方法学简介

1.1 SystemVerilog

SystemVerilog是新兴的一种工程语言:硬件描述与验证语言(hardware description and verification language,HDVL)。SystemVerilog使得工程师不但可以建模大型的复杂的ASIC设计,并且可以验证这些ASIC设计的功能是否达到了预期的目标[3]。

SystemVerilog的优点如下:①语言单一,是同时支持设计与验证的语言;②支持带约束的随机激励的产生;③支持覆盖率统计;④支持断言的验证;⑤提供面向对象的编程,有助于采用事务级的验证,提高验证的重用性[4]。

作为一门新兴的语言,SystemVerilog得到了来自SYNOPSYS,Mentor Graphic和Cadence三大 EDA厂家的大力支持,已经被业界各大公司广泛应用到实际的研发项目中。Verilog编译仿真器(verilog compile simulation,VCS),QuestaSim 以及 Incisive等多种仿真器都支持SystemVerilog的编译仿真,VMM等基于SystemVerilog的验证方法学也被广泛采用;SystemVerilog已逐渐取代VERA语言和e语言成为设计工程师和验证工程师的首选。

1.2 VMM方法学简介

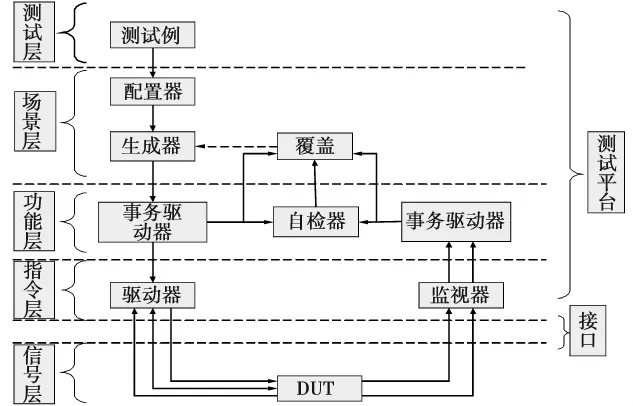

VMM验证方法学,是Synopsys公司推出的基于SystemVerilog语言建立的事务级的验证环境。验证工程师能够通过使用VMM验证方法学提供的带约束的随机激励、层次化结构以及覆盖率驱动等特点,来提高现今的验证效率,构建一个可重用的和通用的验证平台。VMM验证方法学是一种层次化的架构、事务级通信的验证方法学,VMM验证方法学的基本结构分为5层,即:测试层、场景层、功能层、命令层和信号层,每个层次都有独立的功能,验证平台的层次化结构如图1所示[5]。

场景层包含配置器(configure)和生成器(generator),此层位于测试层之下,可以产生带有一定约束关系的随机事务。场景层是以随机的序列和次序生成场景,从而产生相应场景的事务数据流。

图1 VMM验证平台结构Fig.1 Structure of VMM verification platform

功能层一般包含事务驱动器(transactor)、记分板(scoreboard)以及比较器(checker),它与高层模块的功能相关。功能层除了包含一些添加的协议检查器外,与物理层的信号传输没有必然的联系,它可以判断设计功能的正确性。

指令层一般包括驱动器(driver)、信号监视器(monitor)、总线功能模型(bus function model,BFM),这些组件都与设计的物理层协议有关。指令层能够通过信号层来驱动被测设计(design under test,DUT)的管脚,同时为功能层提供事务级的传输通道。

信号层为DUT提供信号级的连接,它能够采用SystemVerilog中一些特殊的结构,例如接口、端口、时钟等,将设计模块的管脚名进行抽象,从而使得当设计模块的管脚发生变化时不需要更改验证环境。

2 LTE小区搜索模块验证平台搭建

2.1 LTE小区搜索过程简介

移动终端(user equipment,UE)刚开机时,必须首先确定出LTE小区所在的频点,这是通过计算频点处的接收的信号强度指示 (received signal strength indicator,RSSI)来判断的,确定了系统频点后,需要检测出主同步信号(primary synchronization signal,PSS)所在的位置,这样UE就能够获取小区ID的一部分信息了,再利用这一部分信息去检测辅同步信号(secondary synchronization signal,SSS)就可以获得关于小区ID的全部信息,以及帧定时、循环前缀(cyclic prefix,CP)长度、双工模式等信息。去检测物理广播信道 (primary broadcast channel,PBCH)以获得更详细的小区信息。

2.2 LTE小区搜索模块功能介绍

LTE小区搜索模块主要完成的功能是小区初始搜索中对扇区ID和小区组ID的检测,即检测主同步信号PSS和辅同步信号SSS,以获得所在小区的物理层小区ID和与该小区的帧同步,用以UE的后续接入过程。小区搜索模块中快速傅立叶变换(fast fourier transform,FFT)功能采用基2的时间抽取运算方法。除了FFT功能外,小区搜索模块还具备频域软纠正、归一化因子和最大值输出、本地PSS和SSS的产生、SSS信号的分段相关等功能。

2.3 小区搜索模块所需验证功能点

1)寄存器的复位值和读写功能;

2)存储器的读写功能和清零功能;

3)中断使能情况下,中断信号能正确到来;

4)中断屏蔽情况下,中断标志寄存器能正确置位和中断标志寄存器清除功能;

5)功能时钟和接口时钟变频功能;

6)数字信号处理(digital signal processing,DSP)启动模块功能;

7)直接内存存取(direct memory access,DMA)启动模块功能;

8)输入输出数据控制功能;

9)输出数据按比特取反功能;

10)FFT功能和FFT的最大值及归一化因子输出功能;

11)频域软纠正功能;

12)PSS,SSS序列产生功能;

13)滑动相关功能;

14)SSS序列的分段相关功能;

15)PSS,SSS序列的冲激响应产生功能;

16)最大值查找功能;

17)M0值估计功能;

18)M1值估计功能。

2.4 模块级分层验证平台搭建

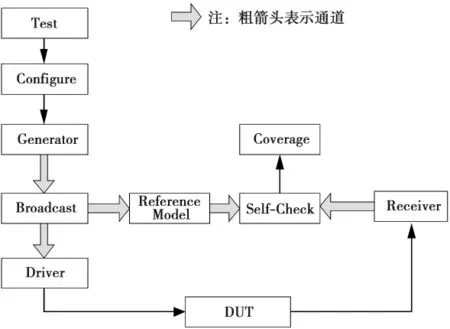

根据对LTE小区搜索模块的功能、接口时序和协议的分析理解,整理了本模块所需验证的功能点,采用了VMM验证方法学,搭建了小区搜索模块的验证平台,验证平台的结构如图2所示。

1)验证环境(environment):VMM验证方法学提供了运行验证环境的基本类vmm_env,其采用了9步顺序执行的机制:gen_cfg(随机化配置参数)、build(建立并且连接环境组件)、reset_dut(DUT硬件复位)、cfg_dut(配置 DUT的寄存器)、start(开始运行所用环境组件)、wait_for_end(等待仿真结束条件)、stop(停止运行所用环境变量)、cleanup(检查记录状态,清除剩余数据)、report(报告仿真结果)。小区搜索模块验证平台所用的事务都通过继承的vmm_env类生成例化,并将验证组件按照验证平台结构图连接起来,在vmm_env的框架中运行。

图2 小区搜索验证平台结构Fig.2 Structure of cell search verification platform

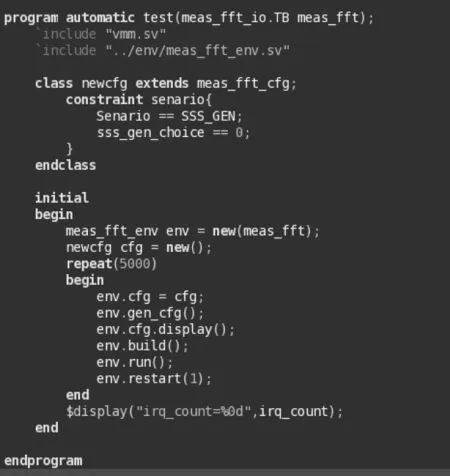

2)配置(configure):利用配置组件对小区搜索模块的工作模式进行了随机配置,并且对各个寄存器在不同的工作模式下进行了约束随机配置,以达到对相应功能进行验证的目的。小区搜索模块的工作模式分为只进行FFT/快速傅里叶逆变换(inverse fast fourier transform,IFFT)、只进行频域软纠正、FFT结合频域软纠正、PSS/SSS序列生成、滑动相关、FFT结合SSS分段相关、FFT结合PSS/SSS的冲激信号生成、主峰值查找、M0值估计、M1值估计等。配置组件的部分代码如图3所示。

3)数据包(packet):对DUT的输入输出数据进行定义,并约束输入数据的位宽、取值范围、长度等[6]。对小区搜索模块来说,输入数据是随机的16 bit的有符号数,这些数据需要进行FFT/IFFT处理。数据包能够通过传输通道(channel)传递给其他的验证组件。

4)数据包生成器(generator):用于生成带有约束的随机数据包。小区搜索模块的生成器通过调用VMM标准库中的宏vmm_atomic_gen自动产生,不需要验证人员手动创建,大大节省了搭建验证平台的时间。

5)广播器(broadcast):小区搜索模块的广播器用于将数据包生成器产生的同一个数据包分别发送给驱动器和参考模型,实现数据包的重复利用,并保证DUT和参考模型输入数据的一致性。

图3 配置类代码Fig.3 Part of code for configure class

6)驱动器(driver):小区搜索模块的驱动器从广播器中得到数据包,根据配置组件中的配置信息对DUT进行驱动,并且Driver将模拟ARM对DUT进行配置。

7)接收器(receiver):小区搜索模块的接收器将判断中断是否来临,并且及时清除中断。在中断到来后,接收器从存储器中读出DUT的结果数据,结合总线的数据位宽和数据包的数据类型对数据格式进行处理,并通过传输通道将处理后的数据传送给记分板。

8)参考模型(reference model):针对小区搜索模块,参考模型实现了与DUT一样的功能,但采用不同于设计的描述语言。参考模型的主要功能是根据输入的数据包进行相应的运算,并产生正确的结果数据后传送给记分板,便于与DUT的输出结果进行对比,确认DUT的代码中是否存在的错误。

9)记分板(scoreboard):小区搜索模块的记分板从通道中分别取得接收器和参考模型的输出数据,并调用packet中的对比函数,完成对数据的自动对比。对比时,首先对比数据的长度,然后根据索引,对各个数据分别进行对比。在对比过程中,任意一个数据对比错误都会终止仿真,并打印错误信息,便于找到错误的根源。

10)覆盖(coverage):对小区搜索模块的工作模式、数据的有效位宽、时钟频率等各功能点的覆盖情况进行统计,达到覆盖率快速收敛的目的 。当功能覆盖率收敛到一定值以后,便可自动停止仿真。

11)测试例(testcase):根据小区搜索模块的不同应用场景,编写不同的测试例[8]。在每一个测试例下,对各组件进行继承,对随机变量进行新的约束,使DUT工作在特定的某项功能下。以产生本地SSS序列的测试例为例,测试例代码如图4所示。首先,由于在配置组件中,对每种功能场景下每个寄存器的配置值进行了约束,所以在测试例中,只须继承验证环境的配置类,并添加一个新的约束,将该测试例运行的功能场景约束为只运行本地SSS产生在这个功能即可。接着,对验证环境和新的配置类进行创建(new方法),并将新的配置类对象赋给验证环境的配置类对象。最后,调用run()任务,对9个机制进行顺序执行,其中已经调用过的gen_cfg和build不会执行。

图4 SSS产生功能测试例Fig.4 Testcase of SSS generate function

从图4中可以看出,采用VMM验证方法学搭建的验证平台,测试例部分的代码是十分简洁的,用少量的代码就能对目标功能进行验证。对于不同场景下的测试例,只须修改约束中场景的约束,节省了编写测试例的时间。

3 验证结果

本验证工作采用系统环境为UNIX操作系统的Solrais9,使用Synopsys公司的VCS仿真器,对小区搜索模块进行了全面的功能验证。

以产生本地SSS序列的功能为例,仿真波形如图5所示。

从图5中可以看出,小区搜索模块的SSS序列产生功能结束后,能正常产生中断信号(fft_irq信号线拉高),并保持32个ZSP时钟周期。中断产生后,从存储器中能够读取模块运算的结果数据。经过与参考模型产生的正确输出数据对比,证明在不同的扇区ID和小区组ID情况下,小区搜索模块产生的本地SSS信号是正确的,该功能能达到预期的目标。

图5 SSS产生功能波形Fig.5 Undee figure of SSS generate function

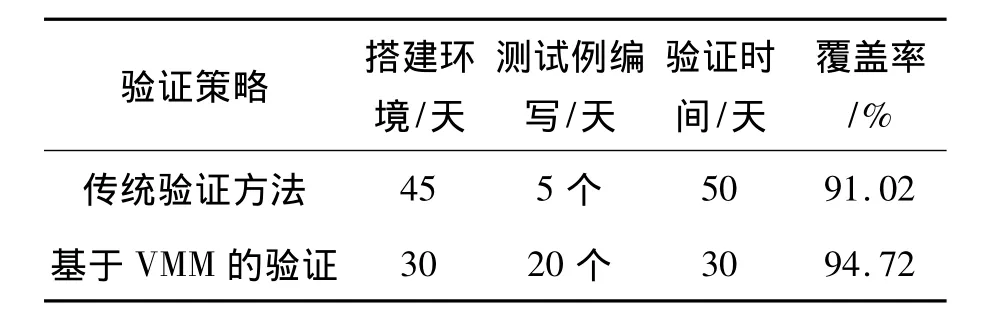

验证工作完成后(即验证过程中发现的BUG都已经解决且所需验证的功能点均验证通过),将所有的测试例重新运行一遍,对代码的覆盖率进行统计。最终的覆盖率统计结果如图6所示。

图6 覆盖率统计Fig.6 Statistics figure of coverage

从图6中我们可以看出断言覆盖率和功能覆盖率均达到了100%,而行覆盖率、条件覆盖率、翻转覆盖率和状态机覆盖率都没有达到100%。经过分析,行覆盖率没有达到100%的原因是设计代码中存在一些冗余代码,模块运行中不会涉及到这些代码,这些冗余代码是应该被删除掉的。条件覆盖率为95.37%,原因是存在正常情况下不会出现的条件。翻转覆盖率没有达到100%的原因是一些变量定义的位宽比实际使用的位宽大,实际运行中多余的位宽的数据始终为0,不会翻转到1。状态机覆盖率只有79.91%,是所有覆盖率中最低的,造成这个结果的原因是设计代码中考虑了中途断电的问题,设计了许多正常工作状态会跳往空闲状态,而在正常工作中是不会出现这样的跳转。经过对覆盖率的分析,此验证工作达到了预期的目标,所有的功能点都覆盖到了,没有遗漏。

在LTE小区搜索模块验证完成后,模块的质量评估(quality assurance,QA)统计数据与以前相同规模和难度的模块的统计数据比较如表1所示。由于本次验证采用了VMM验证方法学搭建验证平台,搭建验证平台的时间减少了1/3。层次化的验证平台结构,降低了编写测试例的时间,提高了测试例的执行速度。对于功能覆盖率和断言的引入比较方便,测试例也比较灵活,覆盖率得到了提高。因此,整个模块验证所用时间缩短了1个多月,并且验证效率和验证的完备性都得到了提高。

表1 验证时间对比Tab.1 Verification time comparison

4 结论

本文以SystemVerilog语言和VMM验证方法学为基础构建的验证平台,利用带约束的随机激励、断言、覆盖率驱动等先进的验证技术,完成了对小区搜索模块的功能点的验证,并且得到了覆盖率统计结果,使验证工作更加完备。VMM验证架构具有良好的代码重用性,可以缩短搭建验证平台所用的时间,能够高效地完成复杂设计的验证,并且极大地提高了可靠性。

[1]CHRIS Spear.SystemVerilog for Verification[M].New York:Springer,2006:1-18.

[2]JANICK Bergeron,EDUARD Cemy,ALAN Hunter.Verification Methodology Manual for System Verilog[M].New York:Springer,2005:10-16.

[3]钟文枫.SystemVerilog与功能验证[M].北京:机械工业出版社,2010:5-9.ZHONG Wenfeng.SystemVerilog and functional verification[M].Beijing:China Machine Press,2010:5-9.

[4]Accellera Organizationtion.SystemVerilog3.1 a Language Reference Manual Accellera’s Extensions to Verilog[M].California:Accellera,2004:30-45.

[5]BERGERON Janick.Writing Testbenches using System Verilog[M].New York:Springer,2006:5-8.

[6]杨鑫,徐伟俊,陈先勇.SystemVerilog中的随机化激励[J].中国集成电路,2007,23(1):58-62.YANG Xin,XU Weijun,CHEN Xianyong.Random excitation in SystemVerilog [J].China integrated circuit,2007,23(1):58-62.

[7]ANDREW Piziali. FunctionalVerification Coverage Measurement and Analysis[M].New York:Kluwer Academic Publisher,2004:13-15

[8]方颖立.基于VMM的寄存器抽象层验证[J].电子设计技术,2007,35(4):103-104.FANG Yingli.The register abstraction layer verification based on VMM[J].Electronic design technology,2007,35(4):103-104.