高压开关机械特性测试仪校验装置的研制

2013-10-25余晓曦

肖 鹏,王 林,余晓曦

(中国测试技术研究院电子研究所,四川 成都 610021)

0 引 言

为保证高压开关安全运行,必须用高压开关机械特性测试仪对其机械特性进行测试,了解高压开关的各种参数是否正常,从而进行相应的维护检修。高压开关机械特性测试仪能够对高压开关的合、分闸时间、弹跳时间、速度、行程等参数进行测量[1]。由于行程便于校验,速度则是根据行程和时间参数来确定的,所以测试仪最主要的技术指标就是时间参数的准确度。目前,测试仪没有专用标准器,各生产厂家所用的校验方法也不尽相同[2-3]。

针对这种现状研制了高压开关机械特性测试仪的校验装置,可对高压开关机械特性测试仪的各时间参数进行校准。本装置应用CPLD和MCU联合控制机制,通过MCU控制高速切换开关来模拟高压开关合闸、分闸以及弹跳动作,同时利用CPLD高速计时的特点,对整个合、分闸及弹跳时间等进行校准。

1 原理及功能概述

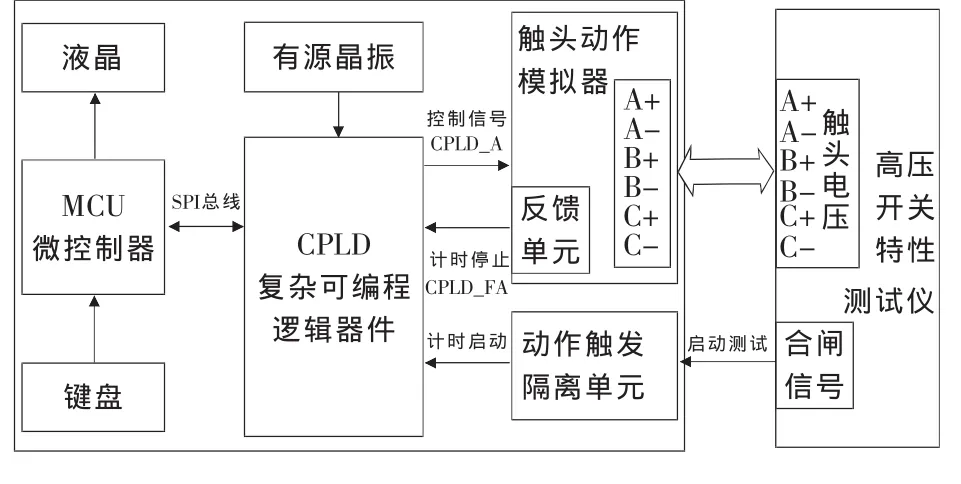

本装置由AVR微控制器、CPLD控制电路、人机接口电路(键盘和液晶)、触头动作模拟器电路和动作触发隔离电路等组成。其系统结构如图1所示。AVR微控制器将设定好的动作方式与时间通过SPI总线方式传递给CPLD,由CPLD内部的逻辑来控制触头动作模拟器进行动作。当高压开关机械特性测试仪启动测试信号后,通过隔离单元触发CPLD依据设定时间控制触头动作模拟器做预定动作,然后CPLD依据反馈信号开始计时,同时高压开关特性测试仪检测触头电压信号从而进行校准。下面以合、分闸时间和弹跳时间分析装置的工作过程。

图1 系统结构图

1.1 合、分闸时间校验

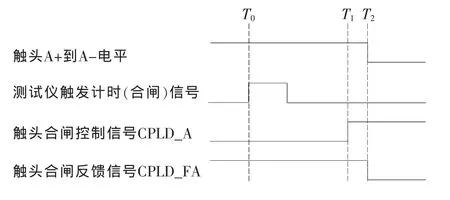

当校验装置模拟合闸动作时,具体工作时序如图2所示。触头初始状态处于开路状态,即两触头(A+、A-)间为高电平;当测试仪发出合闸信号时,测试仪产生一个正脉冲,从脉冲的上升沿T0时刻开始计时,当设置的合闸时间T1时刻到来时,由CPLD发出控制信号CPLD_A,控制触头模拟器两触头(A+、A-)导通,使得两触头间电平处于逻辑低电平,从而触发测试仪完成合闸时间测试。由于触头模拟器电路有一定的延时,实际合闸时间不是T1-T0而是T2-T0,所以必须利用触头合闸反馈信号CPLD_FA对合闸时间进行回测,利用CPLD门电路的特点,依据时序在CPLD中设计计数逻辑,对高精度的有源晶振进行计数,从而得到标准合闸时间。分闸时间校准过程与上述原理一样。

图2 合闸时间的工作时序

1.2 弹跳时间校验

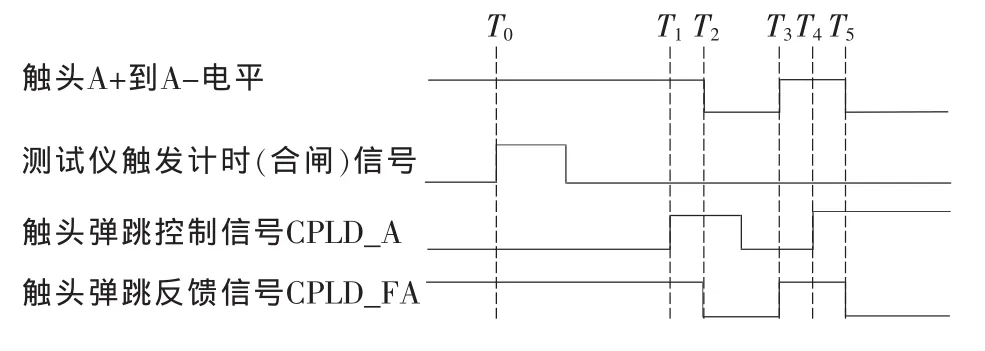

校验装置模拟弹跳动作时,具体工作时序如图3所示。触头间初始状态处于开路状态,即两触头(A+、A-)间为高电平;当测试仪发出合闸信号,从脉冲的上升沿T0时刻开始计时,当设置的合闸时间T1时刻到来时,由CPLD发出控制信号CPLD_A产生一个脉冲抖动信号,控制触头模拟器两触头(A+、A-)先导通,再闭合,最后再导通,使得两触头(A+、A-)间电平从T2时刻的高电平变为低电平,T3时刻又变为高电平,T5时刻又变为逻辑低电平,从而触发测试仪完成合闸时间测试。由于触头模拟器电路有一定的延时,实际弹跳时间不是T5-T2而是T4-T1,所以必须利用触头合闸反馈信号CPLD_FA对合闸时间进行回测。装置模拟了从校准正脉冲上沿出现时开始的开关触头闭合的接触振荡,至正脉冲下沿出现时刻的触头最后一次分离后的重新接触,符合有关标准对合闸弹跳时间的定义。

图3 弹跳时间的工作时序

测试仪可对被测开关的合、分闸时间、三相不同期时间、弹跳时间等参数进行测量,基本量是合闸分闸时间和弹跳时间,其他量可通过基本量运算后得出。因此该校验装置设计了A、B、C三路触头模拟电路和相应的时间测量电路,根据设置三路不同的合闸时间,便可以得到三相不同期的时间参数。

2 关键单元电路的设计分析

2.1 触头动作模拟器和隔离单元

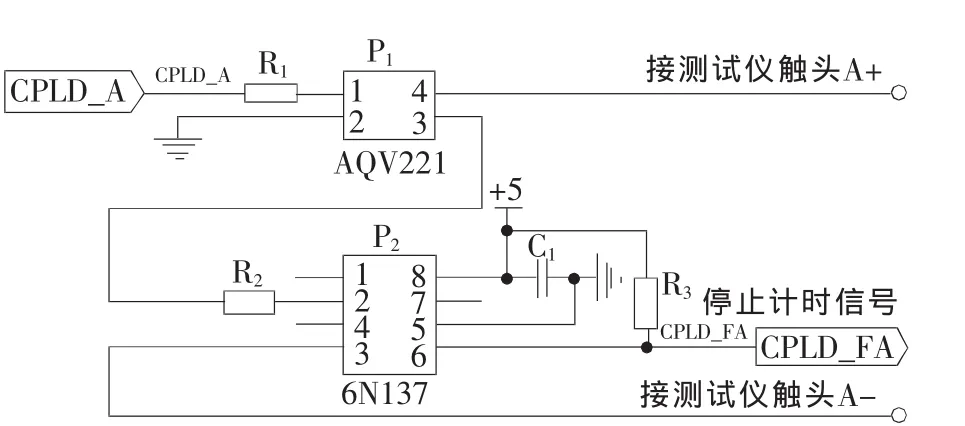

合、分闸和弹跳时间都是根据高压开关触头电平变化得到的,触头电压是由测试仪提供的(一般为12VDC),本装置的触头动作模拟器通过控制光继电器AQV221的通断来模拟高压开关触头电平的变化,从而模拟高压开关的合、分闸及弹跳的动作,具体电路如图4所示。AQV221具有动作迅速(0.1ms)、导通电阻小(0.1Ω)、隔离度高(1000MΩ)而且没有机械振动等特点,特别适合模拟高压开关触头电压的变化。

当CPLD_A为低电平时,AQV221输出端子(3、4管脚)间开路,测试仪两触头(A+、A-)间为高电平;当CPLD_A为高电平时,AQV221输出端子(3、4管脚)间短路,同时触发高速光耦6N137导通,测试仪两触头(A+、A-)间为低电平。图4中的6N137用来实测模拟触头电平变化的反馈信号。

图4 触头动作模拟器电路

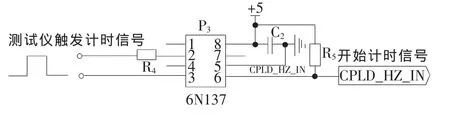

测试仪触发计时信号采用高速光耦6N137进行隔离,由于采用高速光耦6N137,该光耦导通时间是纳秒级,所以对于0.01ms的校准可以忽略不计。这样不仅不会影响测量的精度,同时还实现了校准装置与测试仪的电气隔离。具体电路如图5所示。

图5 触发隔离电路

2.2 CPLD逻辑设计

CPLD的逻辑设计主要包括两部分,一是CPLD与MCU控制器的逻辑设计,二是CPLD对触头模拟器以及合、分闸时间与弹跳时间等的计时控制逻辑。

2.2.1 CPLD与MCU的逻辑设计

MCU和CPLD采用SPI总线方式进行通信,其中AVR单片机作为主设备,CPLD作为从设备,当MCU主动去向CPLD写命令参数时,CPLD采用移位寄存器将串行数据转变为并行数据,然后经过D触发器将MCU的命令传递给CPLD;当MCU主动去读取CPLD的计时参数时,在CPLD内部的逻辑其实是先将并行数据转换为串行数据然后通过SPI总线传递给MCU[4-5]。

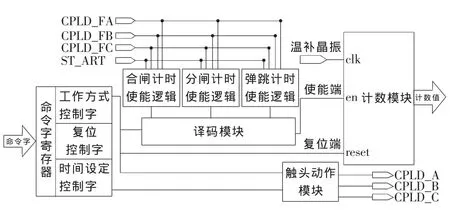

2.2.2 CPLD控制和计时逻辑

CPLD控制和计时逻辑的逻辑电路框图如图6所示。从MCU传递来的命令控制字存入命令寄存器,命令寄存器中的工作方式控制字与时间设定控制字一方面通过译码控制触头模拟器电路按照设定时间动作;另一方面对3种使能逻辑(合闸、分闸及弹跳的计时使能逻辑)进行译码,最终得到计数的使能信号;命令寄存器的复位控制字在每次计数前对计数模块清零。计数模块时钟输入端采用带温度补偿的高精度晶振,计数使能信号的上升沿锁存最终的计数值,然后输出到时间寄存器中供MCU读取显示。

图6 计时逻辑电路框图

3 测试结果及不确定度评定

3.1 测试结果

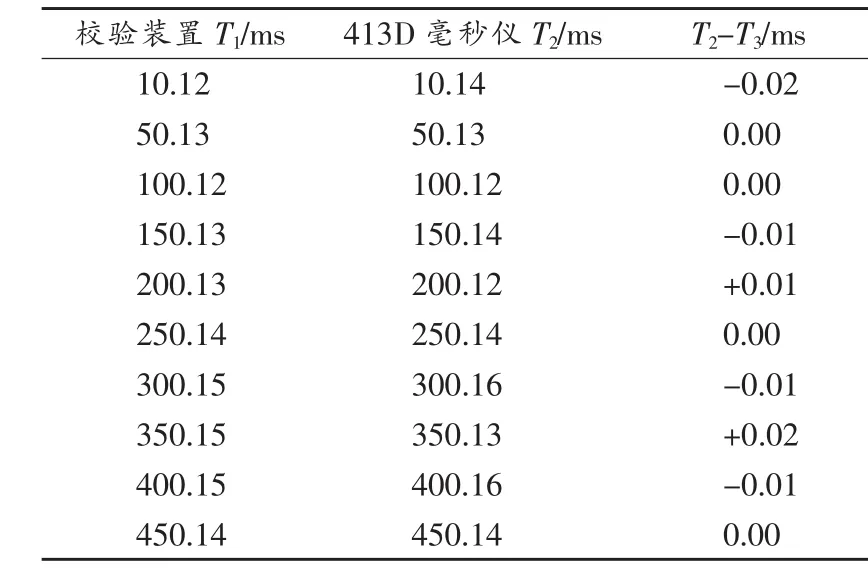

用一台413D型毫秒仪对高压开关机械特性测试仪校验装置合闸时间进行校验,测试数据如表1所示,测试绝对误差≤±0.02ms。

表1 测试数据

3.2 不确定度评定

因篇幅所限,本文仅对合闸时间校准的测量不确定度作评定。开关特性测试仪合闸时间校准的测量不确定度来源主要有:测量值不重复引入的不确定度;标准装置引入的不确定度;开关特性测试仪分辨率引入的不确定度[6-9]。合闸时间的数学模型为

式中:EX——校验装置的示值;

ES——毫秒仪示值;

δ1——测量重复性引入的误差;

δ2——校验装置分辨率引入的误差。

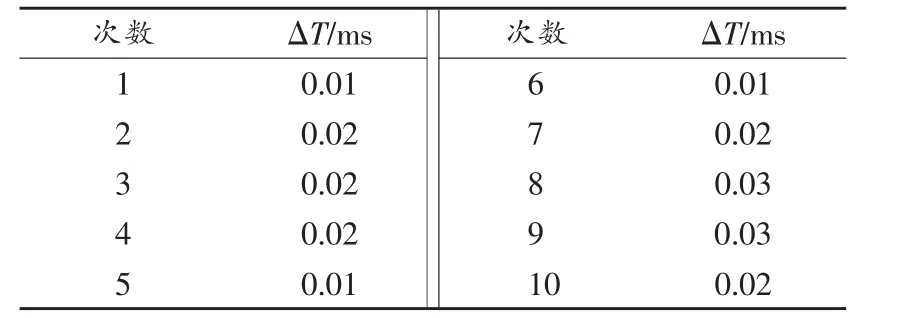

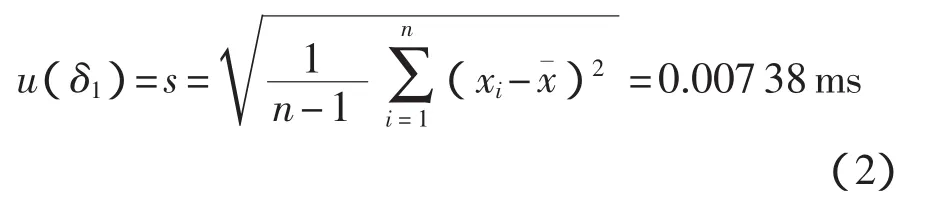

重复性引入的不确定度分析:在相同条件下,对毫秒仪100 ms进行10次稳定性合闸时间测量,所得的数据如表2所示。

表2 重复性测试数据

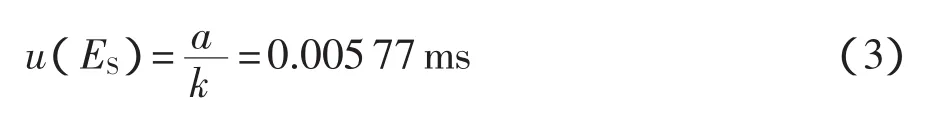

毫秒仪引入的不确定度分析:毫秒仪在误差限在100ms时为±0.01ms,即a=0.01ms,属于均匀分布,覆盖因子k=,其不确定度为

所得标准差为

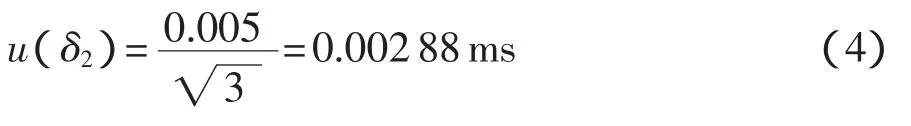

校验装置分辨率引入的不确定度:校验装置分辨率为0.01ms,因属于均匀分布,覆盖因子k=,按半宽0.005ms计算,其不确定度为

合成标准不确定度的计算:由于各个不确定度分量不相关,各灵敏度系数为1,所以合成标准不确定度为

4 结束语

本装置已对多种型号高压开关机械特性测试仪进行校准,长期使用证明,其完全满足测试仪合、分闸时间及弹跳时间的校准要求,可以开展高压开关机械特性测试仪的校准工作。本装置采用光继电器代替传统的电磁继电器,不仅实现了系统的自动化控制,而且大大提高了测试校验精度,具有操作简单、方便等优点。

[1]郭璐,李中健,雷浩.高压开关机械特性测试系统的设计[J].计算机测量与控制,2010,18(10):232-233.

[2]宋庆环,高志,才卫国.高压开关电磁操动机构动态仿真研究[J].煤炭工程,2008,32(5):101-103.

[3]李建基.高压开关设备实用技术[M].北京:中国电力出版社,2005:213-221.

[4]黄任.AVR单片机与CPLDFPGA综合应用入门[M].北京航天航空大学出版社,2004:130-138.

[5]肖鹏,肖文,孙茂一.基于FPGA+MCU的数字电桥的研制[J].电测与仪表,2009,46(526):63-66.

[6]贾祺.高压开关动特性测试仪合、分闸时间测量准确度校准方法探讨[J].计量技术,2008,29(1):55-56.

[7]刘智敏.不确定度及其实践[M].中国标准出版社,2000:186-192.

[8]张志滨.高压开关特性测试仪时间参数的校准方法[J].计量技术,2007,28(1):54-56.

[9]邓伦兵,谢华,付在明.一种矩形脉冲信号沿控制电路设计[J].中国测试,2010,36(1):48-51.