基于FPGA的计算机故障诊断系统设计

2013-08-20李卫兵王洪国史传宝

李卫兵 , 王洪国 , 胡 波 , 史传宝

(1.滨州学院 物理与电子科学系,山东 滨州 256600;2.滨州学院 飞行学院,山东 滨州 256600;3.滨州学院 航空信息技术研发中心,山东 滨州 256600)

计算机在当今社会作为一个重要的工具使用已经很普遍,但是人们也为其故障影响工作而烦恼,而计算机都是板卡设计,非专业人员若是能借助计算机故障诊断系统诊断出故障所在,自己维修也是可行的。利用计算机的加电自检[1](POST——Power-on self Test英文缩写),在计算机启动的时候写入在BIOS芯片中的自检程序就会自动启动[2]。启动后它首先对 CPU、内存、显卡、硬盘、光驱/软驱等硬件部位进行检查,并分析对比系统的原始配置情况,以及对基本输入/输出(I/O)端口和对其它的外部设备进行初始化,检测出无异常,将引导并加载操作系统,检测出异常,将会使加电自检程序挂起。若能根据计算机加电自检原理,设计一故障诊断系统,以文字的形式给出故障原因,则可以提高维修效率。目前,市场上有一些主板检测卡,但经常出现走码、跳码现象,使得一些错误代码不能准确的检测出来。本文给出一种基于FPGA和PCI总线的计算机故障智能诊断系统。以Altera公司的Cyclone II系列EP2C5T144C8N为信号处理模块电路,以PCI总线接口电路作为与电脑主板的通信的接口。采用VHDL硬件描述语言在FPGA上设计硬件电路实现数据存储,分析,提取等一系列处理,以汉字的形式在液晶上显示出电脑硬件故障,检测速度快,系统性能可靠,准确率高,显示直观。

1 系统的总体方案设计

设计中采用的是Altera公司的CyClone II(飓风)系列的低成本FPGA——EP2C5T144C8N,其触发器模块的最大延迟时间在800 ps以下,支持最高50 MHz的工作频率,足够满足33M SPS采样速率的PCI数据采集,而且该型号的FPGA还可嵌入51内核,这一特性对于时序的设计是很方便的。

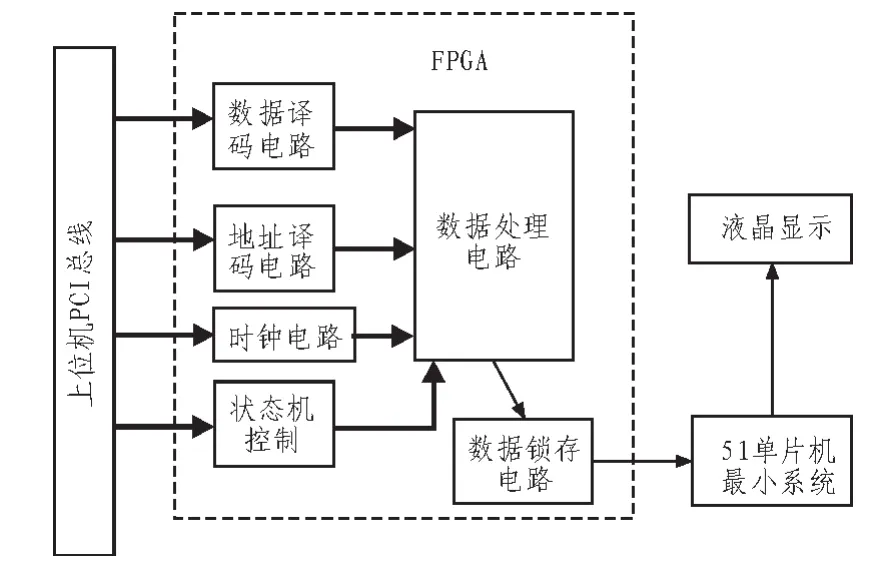

系统硬件电路包括地址、数据译码电路、时钟电路、数据处理电路、数据锁存电路、状态机控制电路、单片机系统设计等,总体结构框图如图1所示。

图1 总体结构框图Fig.1 Overall structure diagram

2 PCI总线操作时序

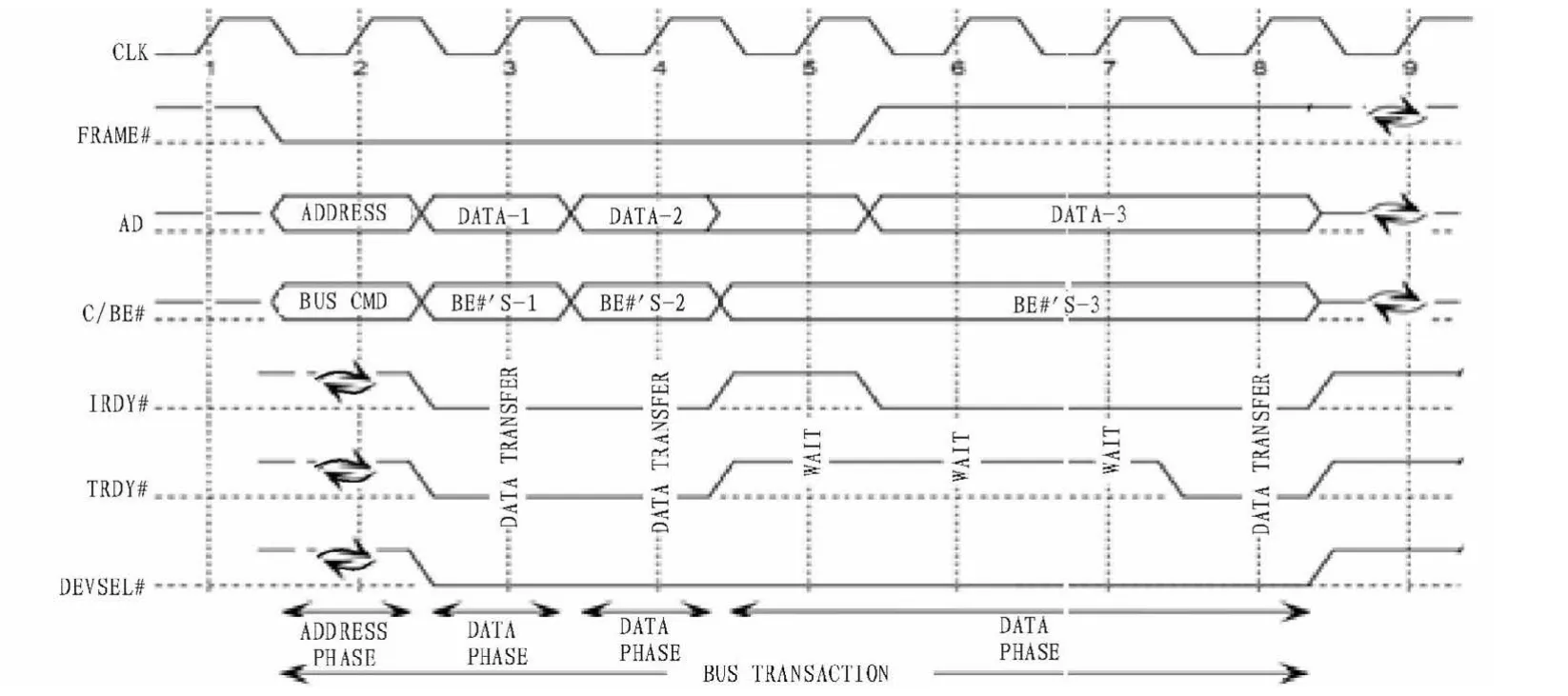

根据PCI总线协议,PCI总线上所有的数据基本上是FRMAE#,IRDY#,TRDY#3条信号线控制的[3-4]。 本设计中用到的主要是写操作,重点分析写操作的时序关系。PCI基本写操作时序如图2所示,在FRAME#有效后的第一个时钟周期内,AD上传输的是要写入目标PCI设备的地址信息,C/BE#上传输的是命令类型(I/O写命令为0011),DEVSEL#信号有效后,表明目标PCI设备已经被选择到,IRDY#和TRDY#同时有效后,主PCI设备向目标PCI设备中传输要写入的数据,在第5个时钟周期时,IRDY#和TRDY#同时变为无效状态,AD总线上被插入一个等待周期,第6和第7个时钟周期时,IRDY#有效,但是TRDY#无效,传输仍然不能有效进行,总线上被继续插入两个等待周期,第8个时钟周期时,IRDY#和TRDY#都有效,数据传输继续。

3 FPGA信号处理电路设计

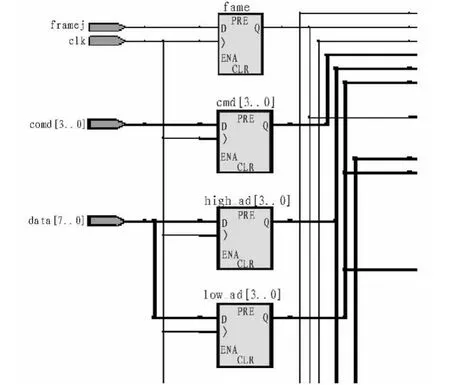

3.1 地址、数据译码电路

地址数据译码器电路的FPGA设计如图3所示,其工作为译出80H的地址,在下一个时钟上升沿时读出数据,并将其引出至数据处理电路的片选信号端进行数据处理。由于PCI总线是地址数据复用的总线,为获取80H端口的信息需要把地址数据分开。本设计中用到的主要是写操作,写操作时序如下。

图2 PCI写操作时序图Fig.2 Diagram of PCI write operation sequence

图3 地址数据译码电路Fig.3 Address data decoding circuit

当framej(j或#表示低电平有效)有效时,总线传输开始,在 data[7::0]上保持有效的地址信号,同时 comd[3 ::0]上保持一个总线命令。如果总线命令为0011b(存储器写命令),同时data[7::0]上的地址又在目标设备的地址范围内,该设备将置devselj信号有效,由于地址和数据都是由主设备提供,不存在data[7::0]切换驱动问题,所以第一个数据节拍产生于第二个时期周期。在这个数据内,comd[3::0]信号是字节允许,表示数据总线的data[7::0]字节有效。主设备在接下来的每个时钟周期的上升沿检查trdyj信号,如果trdyj为高电平,表示从设备没有准备好,主设备自动插入等待周期,反之,将传送数据,完成一个数据节拍。当主设备是framej从有效变为无效,表示当前是最后一个数据节拍。在写周期里,只要framej有效,则下一个周期即可以接收数据,利用这一点,可以为检码带来方便。

3.2 数据处理单元

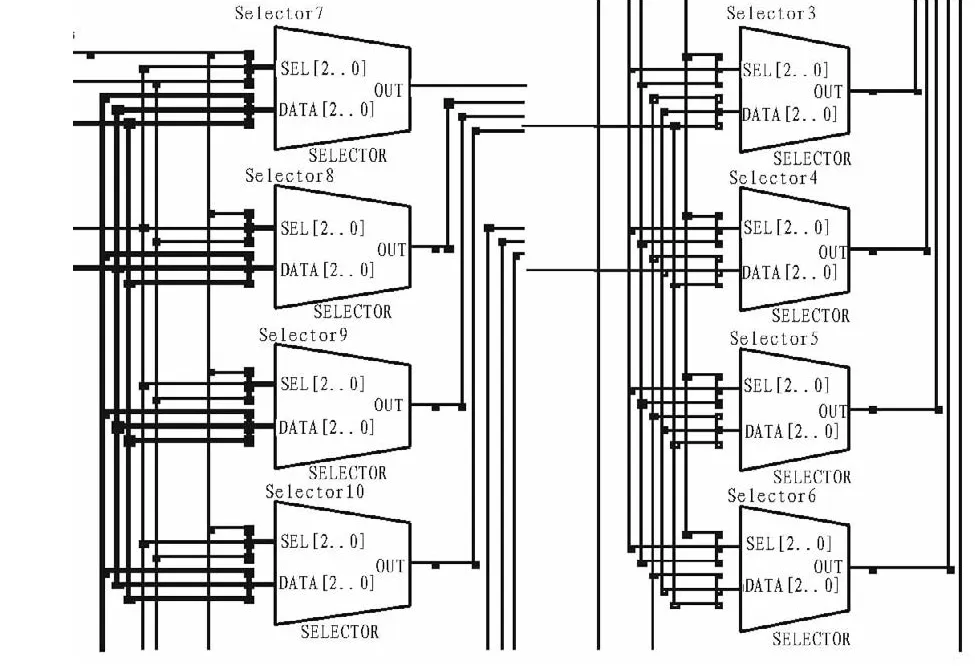

数据处理单元的功能是根据状态的转换对实时锁存的信息进行选择,数据处理电路的设计主要的就是设计数据选择器。由锁存器将不同的检测信息锁存住,然后后续的数据进行对比,通过这些选择器,将没用的数据代码筛选掉,然后传递给51单片机处理,并将其显示在液晶屏上。数据处理电路[5]如图4所示。

图4 数据处理电路Fig.4 Data processing circuit

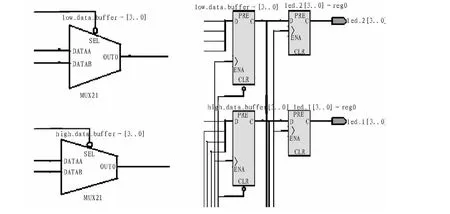

3.3 锁存电路

锁存电路如图5,其中左边的电路是对地址、数据电路检测的POST原代码锁存,右边所示的锁存器是对处理过后的代码信息的锁存,其输出直接连接单片机,与单片机系统的始终匹配。

以上设计中使用的信号:

clk:总线时钟输入。

cmd[3::0]:命令/字节使能,即总线中的 cbej。

framej:由总线主控驱动,指明传输的起始时间和终止时间。

resetj:重新启动(重新分配地址)信号。

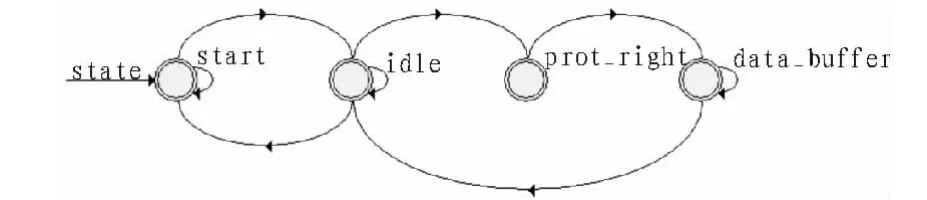

3.4 状态控制电路

根据以上的分析,整个系统有4个状态,用圆圈表示,如图6所示,分别记为:

start:系统为开始工作的状态;

idle:总线资源被CPU或其他设备占用的状态,此时的标志是 framej=1;

图5 锁存电路Fig.5 Latch circuit

port right:系统刚检测到计算机准备往80H端口写信息的状态;

data2buffer:所需要的数据已经写入缓冲区的状态。

另外,还有一个执行动作,即把数据写入缓冲区动作,是在时钟周期的间隙完成的。

图6 状态转换图Fig.6 State transition diagram

4 单片机控制电路

单片机控制电路采用AT89S52单片机,由复位电路、时钟电路、程序下载电路组成。SPI(Serial Peripheral Interface)总线系统是一种同步串行外设接口[6],它可以使MCU与各种外围设备以串行方式进行通信以交换信息。SPI总线系统可直接与各个厂家生产的多种标准外围器件直接接口,该接口一般使用4条线:串行时钟线(SCK)、主机输入/从机输出数据线MISO、主机输出/从机输入数据线MOSI和低电平有效的从机选择线SS。本系统利用单片机自带的SPI总线下载程序,可实现在线编程。

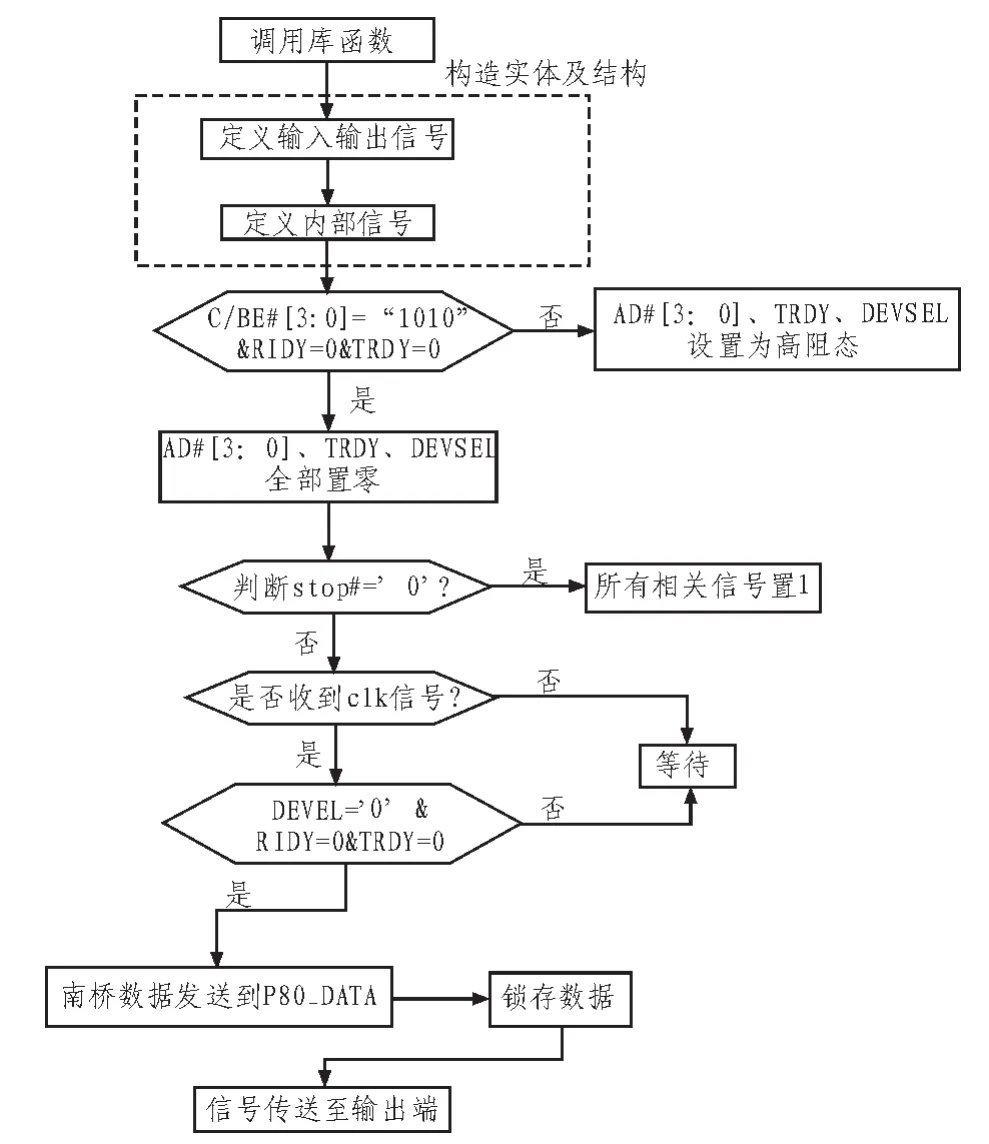

5 软件设计及实现

实现数据的采集、转换、存储、处理和I/O等功能,它把从通过PCI总线获得的计算机主板数据经过接收、锁存(分频、选择)、译码,最终送至51单片机。然后经过51单片机处理后送至液晶显示。其程序流程图[2]如图7所示。

6 结 论

本设计给出一种基于FPGA和PCI总线的计算机故障智能诊断系统。该系统以Altera公司的Cyclone II系列EP2C5T144C8N控制核心为,以PCI总线接口电路作为与电脑主板的通信的接口。根据计算机自身的加电自检原理,采用VHDL硬件描述语言在FPGA上设计硬件电路实现数据存储,分析,提取等一系列处理,以汉字的形式在液晶上显示出电脑硬件故障。为了提高系统的可靠性和准确度,实行模块化电路设计,单元电路包括:地址译码单元、数据译码单元、数据处理单元、状态及控制单元、电源诊断电路单元、液晶显示单元,系统性能可靠,准确率高,显示直观。

图7 程序流程图Fig.7 Program flow chart

[1]刘福胜.计算机加电自检与故障诊断卡的使用[J].电子世界,2003(11):15-16.

LIU Fu-sheng.Using of card in computers electricity selfinspection and fault diagnosis[J].The Electronic World,2003(11):15-16.

[2]李晓莉,甘明.基于PCI总线的主板诊断卡设计[J].电子技术,2007(3):156-158.

LI Xiao-li,GAN Ming.Post card design based on PCI Bus[J].Electronic Technology,2007(3):156-158.

[3]赵敏.基于FPGA实现的PCI数据采集卡的研究[D].太原:华北工学院,2002.

[4]潘松,黄继业.EDA技术与VHDL[M].3版.北京:清华大学出版社,2009.

[5]李卫兵,王洪国.一种基于FPGA的计算机硬件诊断装置:中国,ZL 201120450587.8[P],2012.

[6]何志宏,丁楚平,吴俊.基于PicoBlaze的SPI核设计与实现[J].微处理机,2010(2):86-89.

HE Zhi-hong,DING Chu-ping,WU Jun.The SPll pcore design and realization based on PicoBlaze[J].Microprocessors,2010(2):86-89.