AVS编码器中帧内预测模块的硬件设计

2013-01-31黄圣勋王法翔钟昌标

黄圣勋,王法翔,钟昌标

(福州大学 物理与信息工程学院 福建省集成电路设计中心,福建 福州350002)

AVS是我国自主研发的数字音视频编解码标准,并于2006年获批成为国家标准实施,2012年11月起被强制执行,所有在中国大陆上市的地面数字电视接收机(包括机顶盒、一体机)需内置AVS解码功能,否则将无法销售。作为我国具有自主知识产权的第二代信源编解码标准,其发展对我国的数字音视频业务具有极其重要的意义。

与H.264相比,AVS视频标准解码复杂度只相当于H.264的30%,编码复杂度相当于H.264的70%。其核心技术主要包括:特殊的帧间预测运动补偿、1/4精度像素插值、帧内预测、去块效应滤波、二维熵编码和8×8整数变换等[1]。由此可见,作为AVS编码器的重要组成部分,研究帧内预测的硬件设计与实现意义重大。

在现有的帧内预测硬件实现方案中,由于基于可重构硬件电路只能逐个计算各预测模式的预测值,处理速度较慢,难以满足高清实时编码的需求,因此在高清视频编码器帧内预测部分的硬件设计中,通常采用将具有相同预测值求解算法的预测模式共用一个预测器的设计方案,文献[2-3]都采用这样的设计。文献[2]提出了一种基于并行流水的帧内预测硬件架构,实现6种预测模式的并行处理,取得了很好效果,但其并没有充分利用6种预测模式算法上的相似性进行运算单元的进一步共享,资源利用率不够。而文献[3]虽然相对于文献[2]进一步实现了运算单元的资源复用,但参考数据输入控制机制复杂,资源消耗大,并且一个时钟只能预测各模式的一个像素点,难以满足高清实时编码的要求。

本文在采用并行流水处理结构的基础上,将亮度和色度多种预测模式共用一个预测单元。同时根据各模式算法的相似性,结合移位寄存器操作设计了一种新的预测值计算架构,简化了参考数据输入控制机制,进一步提高了预测值计算单元的硬件复用,减少资源消耗。

1 帧内预测算法原理

AVS帧内预测算法采用了代表空间域纹理方向的多种预测模式,利用当前块相邻的左边和上边块重建数据作为参考样本,实现对当前块数据的预测,有效地去除了相邻块的相关性,很大程度上提高了帧内预测效率[4]。

AVS视频编解码标准中,帧内预测分为亮度预测和色度预测,亮度预测有5种预测模式(如图1所示):Vertical模式(模式值0),Horizontal模式(模式值1),DC模式(模式值2),Down_Left模式(模式值3),Down_Right模式(模式值4);色度预测模式有4种预测模式:DC模式(模式值0),Horizontal模式(模式值1),Vertical模式(模式值2),Plane模式(模式值3)。其中亮度和色度预测有3种预测模式的算法是相同的,因此在帧内预测中共有6种不同的预测模式。

图1 8×8亮度块帧内预测模式

由图1可知,帧内预测各模式的预测方向不同,需要选取的周边块参考数据也不同,因此在预测值计算之前需要提前判断当前块的左边块和上边块是否存在,根据周边块可用性确定预测块可用预测模式及参考数据。帧内预测结束后,需要计算预测块和原始块之间的残差数据用于代价计算。模式判决模块通过比较,选取代价值最小的模式作为最终的预测模式,并将相应模式的残差和预测数据输出,经过重建后作为后边块的参考数据。

在实际应用中一般有三种代价值计算方式,分别为SSD,SATD和SAD[5]。其 中采用SSD的率失真优化(RDO)模式选择算法性能最佳,但运算复杂度高,不利于硬件实现。SAD运算复杂度低,硬件消耗小,但性能一般,而SATD性能较好,介于SSD和SAD之间,同时硬件复杂度不大,资源消耗适中,因此在本设计中采用SATD作为模式代价值计算算法。

2 帧内预测的硬件设计

2.1 模块整体硬件结构

AVS编码器帧内预测主要分为预测值计算和模式判别两部分,而运算中所需的参考像素值和图像原始数据则存储在相应的RAM中,图2给出了帧内预测模块硬件结构框图。由图可知,计算预测值之前需要先判定当前块周边块的可用性(包括左下、左边、左上、上边和右上边快),根据判定结果确定可用预测模式及其对应的参考样本数据。预测单元从RAM中取得参考像素值C0~C17和R0~R17后进行预测值计算,其中亮度和色度共用一个计算单元,同时每种预测模式对应一个预测器,实现各模式的并行计算。预测值计算结束后将预测结果mpr_data输出,进行残差计算以及SATD计算,从而判定最优预测模式best_mode作为最终预测模式,并将相应的残差数据送入变换量化、反变换反量化单元进行处理,然后与存储在预测结果RAM中的预测值进行数据重建,用于后边块的预测。

图2 帧内预测硬件结构框图

需要说明的是,色度预测的代价计算需要综合考虑2个色度块中相应代价之和作为该模式代价值,因此在第1个色度块预测结束后需要将相应的代价值及预测数据进行缓存,直到2个色度块都完成预测后才能得到最终的色度预测模式。

2.2 预测值计算单元设计

通过分析帧内预测算法可知,AVS虽然具有多种帧内预测模式,但除了色度Plane模式外,各模式预测值计算框架都是类似的,每种模式都是以(a+2×b+c+2)>>2的3抽头滤波结构为核心[6]。在本文的设计中也采用该3抽头滤波结构作为帧内预测运算的最小单元,应用于DC模式、Down_Right模式和Down_Left模式中。图3中给出了针对此最小单元设计的硬件电路。对于Vertical模式和Horizontal模式,由于其预测值可由参考样本直接获得,因此只需要进行数据赋值。

为满足高清实时编码要求,提高帧内预测的速度,本设计采用6路并行流水的硬件架构,预测一个8×8块只需要8个时钟周期。由于采用多种模式并行预测,如果每种预测模式都分别采用专用预测电路,同时考虑到DC模式和Down_Left模式预测一个像素需要2个最小运算单元,因此总共需要40个最小运算单元。另外,由于帧内预测可能用到的参考数据最多有35个,则输入控制单元需要从35个参考样本值中选取120个数据作为40个最小单元的预测输入,控制逻辑复杂,硬件资源消耗大。

对此本文通过分析帧内预测算法,结合流水线技术实现各模式相同运算单元的资源共享,将所需最小预测单元缩减至19个,同时采用移位寄存器操作简化参考样本输入控制机制,减少资源消耗,具体硬件电路结构如图3所示,该电路能够满足除Plane模式以外所有预测模式的预测值计算。

图3 预测值计算单元硬件结构

由图3可知,该电路将最小单元的输入初始化为r0~r9和c0~c9,同时通过对输入参考数据的移位操作,实现输出结果outr0~outr9和outc0~outc9的移位,从而达到1个时钟周期预测8×8块、1行8个数据的目的。

预测开始后,各预测模式在控制单元的控制下进行预测值的并行计算。Vertical和Horizontal模式在周边块判别为可用后,预测值分别由输入参考像素值r1~r8和c1~c8直接得到,因此并不需要通过图3电路的运算。对于DC模式,电路在第一个时钟到来时将outr1~outr8的值寄存,如果左边和上边块都可用,则将寄存器reg0~reg7的值分别与outc1求均值后输出,作为当前块第1行预测数据。接着通过c0~c16的移位操作实现outc2~outc8值的移位,并分别与寄存器reg0~reg7的值作均值运算后得到后续7行预测数据;如果仅有上边块可用,则输出寄存器reg0~reg7的值作为每一行的预测结果;如果仅有左边块可用,则输出outc1的值作为一行预测值,否则直接输出常数128作为预测值,在8个时钟内完成一个块预测。对于Down_Left模式,将outr2~outr9和outc2~outc9分别两两顺序求均值作为一行预测结果,通过r0~r16以及c0~c16移位操作在8个时钟周期内实现一个块8行数据预测。对于Down_Right模式,电路在第一个时钟到来时将outr0-outr7的值寄存为s0~s7作为第1行预测结果,然后将outc1和s0~s7进行顺序移位操作并输出s0~s7的值作为后续7行的预测值。

2.3 色度Plane模式硬件设计

色度Plane模式为帧内预测中最为复杂,所需时钟数最多的预测模式,需要通过独立的硬件模块进行运算。图4所示为Plane模式的硬件电路,其中A0=ia+(-3)×ib+(-4)×ic+16,在输入参考数据确定的前提下,ia,ib以及ic的值在当前宏块的计算中都是固定的,因此A0的值也是固定的。根据Plane模式算法,当该预测模式被挂起时,A0以及A0与ib各乘积项之和分别构成预测块第1行的8个预测数据。在第1行预测结束后将预测值进行寄存,并在其后每个时钟周期中将寄存器中的值与ic进行累加,经过限幅运算后输出,作为Plane模式后续7行的预测数据。电路中A0,ic,ib及其各乘积项均采用移位和加法实现,完成一个8×8块的预测需要12个时钟周期。

图4 色度Plane模式预测电路

3 仿真综合结果

本设计采用verilog HDL硬件语言实现,并通过Modelsim SE 6.2b对设计进行仿真,结果与参考C代码rm52j生成的测试向量进行对比,对比结果表明该设计符合AVS编码器中帧内预测模块功能要求。采用Xinlinx公司Virtex4系列FPGA进行综合,综合结果表明频率达到140.1 MHz。本文通过合理的流水线设计,只需406个时钟就能够完成一个宏块的预测,完全符合1 920×1 080,4∶2∶0,30 f/s(帧/秒)视频格式编码器工作在140.1 MHz频率下所要求的576个最大时钟数,并留有30%的时钟裕度。

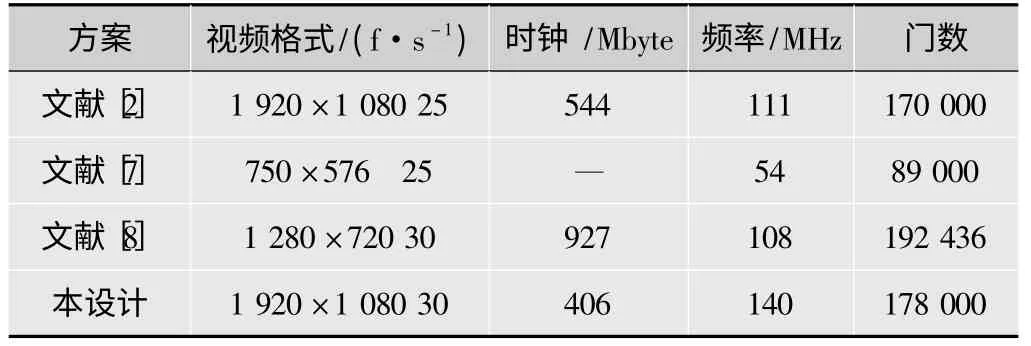

由于采用多路并行流水设计以及更为复杂的SATD算法作为代价值计算方式,因此该电路结构硬件资源消耗相对较大。表1给出了本设计和其他相关文献的设计参数,通过对比可知,本设计在工作频率和预测所需时钟数上具有一定优势,相对于文献[2]在增加少量面积的基础上将频率提高了21%,所需时钟数减少了25%,不失为一个可取的硬件实现方案。

表1 本文与其他文献参数对比

4 结论

本文在分析AVS编码器中帧内预测算法的基础上,采用并行流水结构实现多路预测数据的并行计算,同时通过移位寄存器操作,简化了参考数据选择机制,很大程度上减少了预测所需最小运算单元的数量,提高了资源利用率。仿真综合结果表明,本设计完全能够满足1 920×1 080,4∶2∶0,30 f/s高清视频图像实时编码要求。

[1]GB/T 20090.2—2006,信息技术先进音视频编码第2部分[S].2006.

[2]付华丰,李凤亭.并行结构的AVS帧内预测编码器[J].计算机工程与设计,2009,30(5):1140-1143.

[3]向红莉,张刚.基于FPGA的AVS编码器帧内预测实现[J].软件,2012,33(2):105-107.

[4]ZHANG Nan,YIN Baocai,KONG Dehui,et al.Sptial prediction based intra-coding.[C]//Proc.2004 IEEE International Conference on Multimedia and Expo(ICME'2004).Taibei,China:IEEE Press,2004:97-100.

[5]尹文蕾.基于率失真优化的模式选择快速算法研究[D].武汉:华中科技大学,2008.

[6]黄有文,陈咏恩.AVS解码器帧内预测模块硬件优化设计[J].小型微型计算机系统,2010,31(1):183-185.

[7]ZHANG Ke,YU Lu.An area-efficient VLSI architecture of a Reed-Solomon decoder/encoder for digital VCRs[J].IEEE Trans.Consumer Electronics,1997,43(4):1019-1027.

[8]KIBUM S,SEONGMO P,HANJIN C.An efficient hardware architecture of intra prediction and TQ/IQIT module for H.264 encoder[J].ETRI Journal,2005,27(5):511-524.