基于SOPC的多函数发生器设计

2012-11-05姜为

姜 为

(兰州交通大学电子与信息工程学院, 甘肃兰州 730070)

0 引言

信号发生器作为一种重要的信号源,广泛应用于电子电路、通讯、检测、导航等领域。作为一种为电子测量和计量计算提供数据依据的设备,它同电压表、示波器、频率计等仪器一样,是最普通、最基本的,同时也是应用最广泛的电子仪器之一[1]。直接数字频率合成(Direct Digital Frequency Synthesis,简称 DDS)具有频率分辨率高、频率切换速度快、切换相位连续、全数字化实现、可产生任意波形等特点。本文结合基于SOPC和DDS技术设计可产生不同频率、不同幅度的正弦波、矩形波、三角波、锯齿波信号等多种波形信号。

1 系统的硬件设计

1.1 SOPC系统

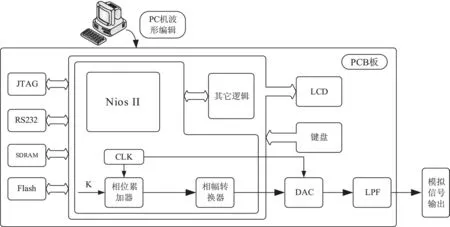

SOPC是在Altera公司生产的Cyclone II系列的EP2C35F672C6N上实现的,在其FPGA上搭建了一个基于NIOS II软核处理器的SOPC系统,系统的原理框图如图1所示。从而完成DDS的数据量输出和系统控制,通过按键对信号的种类、频率以及幅度进行选择,Nios系统控制DDS产生波形信号和各种调制,经过高速的DAC进行转换,而后经过低通滤波,滤除高次谐波和噪声[2],从而得到用户所需的频率相对纯净的波形。

图1 系统原理框图

1.2 DDS模块

直接数字频率合成技术的工作原理是基于幅度和相位之间的对应关系,本文DDS系统是由相位累加器、相幅转换器、数模转换器、低通滤波器组成的[3]。DDS模块的原理图如图2所示,该结构有两个输入,分别是频率控制字K、参考时钟,其工作过程是,在参考时钟作用下,相位累加器对频率控制字K进行线性累加,当相位累加器累积满量时就会产生一次溢出[4],累加器的溢出频率就是DDS的输出信号频率(F):

函数发生器中包含了以相位为地址的波形数字幅度信息表,以相位寄存器的输出作为波形查表地址,改变频率控制字K即可改变输出波形的频率。由DDS输出的量化波形幅度数字量,经过DAC转换成模拟量,经选择滤波、放大后输出所需要的频率和幅值信号。

图2 基于SOPC的DDS模块

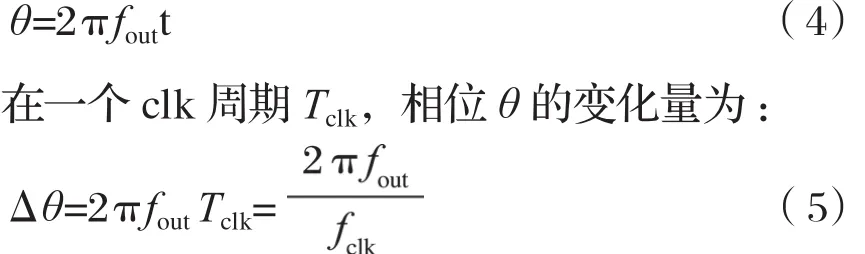

对于正弦函数发生器,它的输出可以用下式来描述[5]:

其中SOUT是指该函数发生器的输出信号波形,fout是指输出信号对应的频率。上式的表达对于时间t是连续的,为了用数字逻辑式实现该表达式,必须进行离散化处理,用基准时钟clk进行抽样,令正弦信号的相位:

其中fclk是指clk的频率对于2π可以理解为“满”相位,为了对Δθ进行数字量化,把2π切割成2N份,由此每个clk周期的相位增量Δθ用与式(5)联立。可得:

显然,函数发生器的输出可能为:

其中θk-1指前一个clk周期的相位值,同样得出

由上面的推导,可以看出,只要对相位的量化增量进行简单的累加运算,就可以得到正弦信号的当前值,而用于累加的相位增量量化值BΔθ决定了信号的输出频率fout,并呈现简单的线形关系[5-6]。

2 函数发生器的后级电路设计

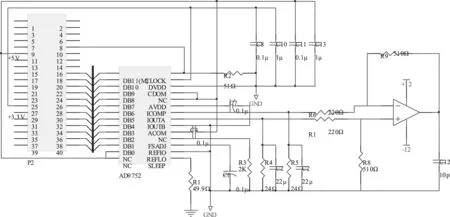

2.1 DAC电路设计

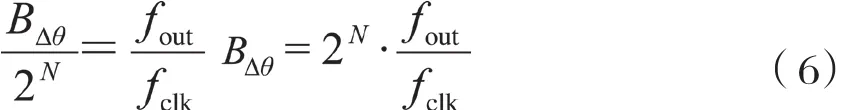

DAC转换电路如图3所示。为了得到用户所需的波形信号,从RAM输出的数据需要经过DAC和幅度控制以及LPF。为了满足设计的需要这里采用的数模转换芯片是AD公司生产的AD9752[7]。RAM输出的数字信号被送到AD9752芯片,数据的采样频率为100。分别送+3.3 V电源和+5 V电源到DVDD(数字电源)和AVDD(模拟电源)。为了得到高质量的电源信号还需在+3.3 V电源和+5 V电源的输入端加0.1 μF和1 μF的抗干扰电容。要使满刻度电流输出在20 mA,FSADJ引脚(满刻度电流输出调节端)需接2 Ω的电阻后接地。CLOCK引脚输入来自EP2C35F672C6N上的时钟脉冲。因低功耗模式在本设计中不适用,故SLEEP引脚(低功耗控制输入端)接49.9 Ω电阻后接地。DCOM引脚直接接地。IOUTA与IOUTB引脚分别接24 Ω电阻后接地,同时为了降低噪声干扰,需在两个引脚和地之间分别接入22 μF电容。为了降低干扰对信号的影响,实现双极性输出以及提高电压输出精度,输出端可以增加由一个运算放大器构成的差分输出电路作为DCA电路的输出。

图3 DAC转换电路

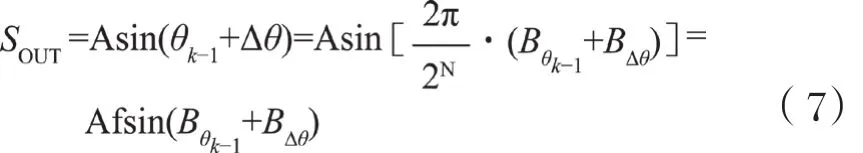

2.2 滤波及放大电路设计

数据经AD9752芯片输出,就由原来的数字信号转换成了我们需要的模拟信号,为了滤除一些高次谐波和噪声以及对波形幅度进一步控制得到用户所需要的波形,还需要对所输出的模拟信号进行调理。

图4 滤波及放大电路

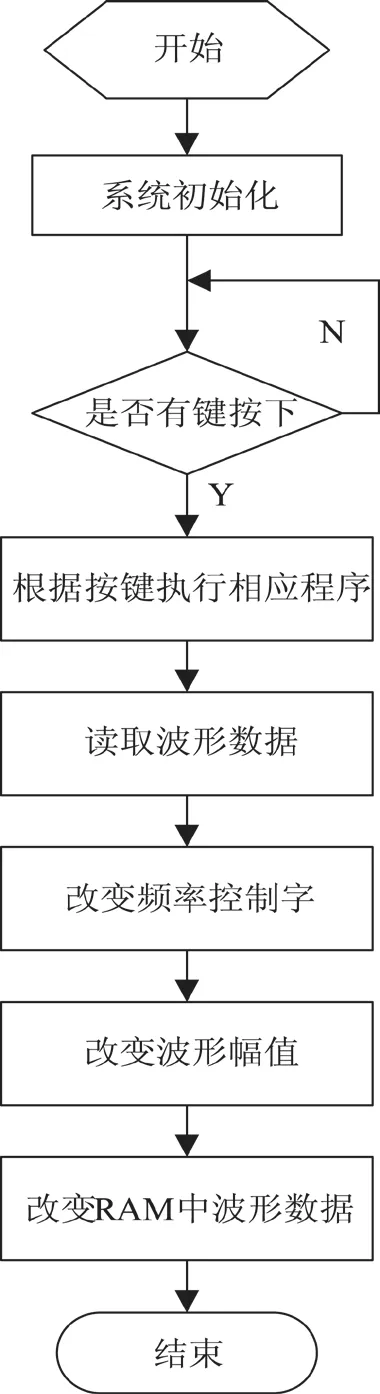

3 系统的软件设计

本系统的软件设计是在NIOS II集成开发环境(IDE)中通过C语言编译完成的。IDE是NIOS II系列嵌入式处理器的主要软件开发工具,它可以完成,如工程管理,编辑和编译,调试,以及闪存器件的编程等[8]。当系统启动后,首先对各个模块进行初始化,然后扫描键盘状态,检查到有键按下就运行键值处理程序,NIOS II接收到数据后,先对数据进行处理,分别计算出频率控制字,幅度控制字以及波形表数据,然后送到DDS模块,经过DDS处理后的数据发送给DA转换器,这样用户设置的参数指标就得到了反馈。NIOS II程序流程图如图5所示。

图5 NIOS II程序流程图

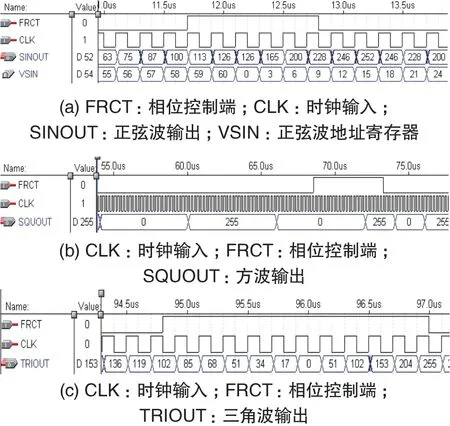

4 仿真结果

仿真结果如图6所示。

图6 仿真结果

5 结论

基于SOPC的DDS函数发生器在一定范围内可输出幅度和频率均可调节的正弦波、矩形波、三角波、锯齿波信号等多种波形信号。将外部信号处理电路板和DE2实验板连接,检查完毕后上电运行程序,把编译完成的.sof格式文件下载到DE2实验板上,通过DE2上的开关,给片上系统输入不同的命令字,观察显示屏上显示的波形数据是否和输出的波形信号特征相同。通过测量液晶屏显示数据和电压输出数据的参数,计算出它们变化时的比例系数,根据此系数对显示程序进行修改。经过反复测试,最终实现了输入控制字发生变化时输出波形数据和显示屏显示的波形数据同步变化,更好的,更直观的反映了输出的信号名称、幅度、频率和相位的变化情况。本设计涉及硬件描述语言逻辑电路设计、硬件电路设计以及C语言编程等知识的运用。系统的灵活性和实用性远超过了传统的函数发生器,所以本系统具有较高的推广和使用价值。

[1] 解澎.基于SOPC技术的任意波形发设备的设计与实现[D].长春:吉林大学,2006.

[2] 周立功.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2007.

[3] 潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2006:317-401.

[4] 史有建.基于DDS技术和FPGA的任意波形发生器的设计[J].河南理工大学学报,2008(12):629-633.

[5] 李雪梅,张宏财,王雪伟.基于DDS技术的信号源设计[J].电测与仪表,2010,47(529):55-56.

[6] 候锡立,靳鹏云.基于SOPC的任意波形发生器的设计[J].计算机测量与控制,2008,16(12):1989-1990.

[7] 崔联飞,欧阳.125MSPS高性能通信DAC芯片AD9752[J].国外电子元器件,2001(9):61-63.

[8] 吕矿生,周杏鹏.基于FPGA和NIOS II的任意信号发生器的设计[J].仪器仪表与分析监测,2008(3):28-31.