一种高速开关电容动态锁存比较器分析与设计

2012-09-05范晓捷张凯虹

范晓捷,黄 峰,魏 斌,李 静,张凯虹

(1.中国电子科技集团公司第58研究所,江苏 无锡 214035;2.黄山旅游发展股份有限公司云谷索道分公司,安徽 黄山,242709)

1 引言

无线通信、高速测量仪器、数字雷达等对应用系统和模/数转换器(ADC)提出了高速度、高精度、大动态范围、宽输入信号带宽、低功耗等指标要求,使得系统对高性能ADC产品的需求日益突出。由于流水线结构可以在较低的功耗条件下实现速度从数十兆到数百兆、精度从10位到16位的模数转换器(ADC),因此成为上述应用场合的ADC实现方式的主要选择[1]。高速比较器作为高速高精度流水线ADC的核心器件,其精度和速度对ADC的性能起着至关重要的作用,比较器较大的失调电压会造成流水线ADC的失码,造成转换错误;比较器速度不够,则不能在要求的时间内完成正确的比较输出,出现亚稳态(metastability)输出。因此,要实现高速高精度流水线ADC,其所用比较器的精度和速度是关键。

由于使用了数字纠错技术,流水线ADC对比较器的精度要求大为降低,因此通常选择低功耗快速的动态锁存比较器。本文基于0.18μm 1.8V CMOS工艺设计了一种可应用于高速高精度模数转换器的动态锁存比较器。论文对该比较器的电路结构和设计原理进行了深入分析,并且详细说明了比较器的版图实现。

2 比较器电路结构

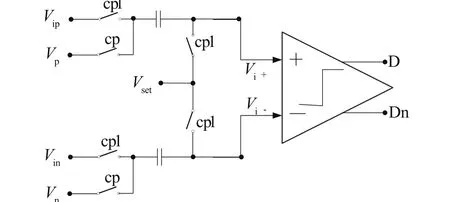

本文所设计比较器为全差分开关电容结构输入的比较器,其总体电路框图如图1所示[2]。其中单管开关为PMOS开关,互补开关上端为NMOS管,下端为PMOS管。其工作过程可以分为两相:采样相和建立相。在采样相,cp1变低,cp为高时,阈值电压Vp和Vn与比较器共模偏置Vset接到电容底极板和顶极板进行采样;在建立相,电容底极板接输入信号Vip和Vin,这样输入信号与阈值信号的差值就出现在电压比较器的两个输入端,然后电压比较器开始进行放大。

图1 开关电容比较器电路结构

比较信号建立过程如下:在采样相两个电容上的电荷分别是C×(Vset-Vip)和C×(Vset-Vin);在建立相,由于电荷守恒,比较器两输入端的电压将分别是Vset-Vip+Vp和Vset-Vin+Vn,相当于将输入电压和比较阈值电压作了比较,即:

3 电压比较器设计

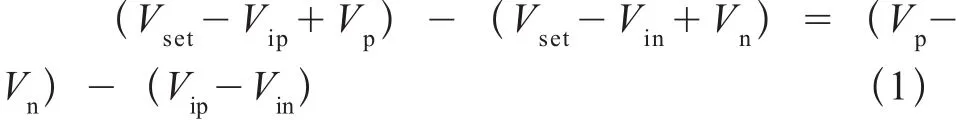

本文所设计的全差分电压比较器电路结构如图2所示[3]。比较器的工作受时钟Ct控制。Ct为低电平时,比较器输出为高电平的复位信号;当Ct为高电平时,比较器输出比较结果。图中M0~M3被偏置在线性区,可看作是阻值由电压控制的电阻,M4~M11构成一个锁存器。该电压比较器工作原理如下:当锁存/置位信号为低时,MOS管M9、M10导通,M4、M5截止,这就使得电源和地之间的通路被截断,因此电源和地之间没有电流流过。同时两个输出端都被充电至电源电压,M10、M9截止,M7、M6导通,所以M6、M7上的压降等于电源电压。锁存置位信号由低到高的瞬间,比较器开始它的比较锁存过程。此时M5、M6的栅极电位仍然是电源电压,而它们的漏极电位立刻升高,所以它们的源端电位差被放大。如果M4~M11都是理想匹配的管子,左右两个支路输入管(M0~M3)的阻值决定了锁存器的稳定状态,即比较器的输出。

图2 电压比较器电路结构

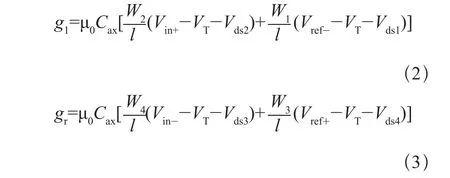

M0~M3分别与输入信号或参考信号相连,由于工作在线性区,左右两个支路的电导可以表示为:

其中VT是阈值电压,Vds是管Mn的源漏电阻。如果没有失配,比较器的输出在gl=gr处改变。设计中取M0=M2、M1=M3,根据gl=gr可 得:

通过改变W1(W3)和W0(W2)之间的比例关系,可以调节比较器的阈值电压。

式(4)表明比较器的失调取决于M0~M3管的失配,但前提是M4~M11都是理想匹配的。由于M0~M3管工作在线性区,它们的电导直接取决于各自的源漏电压Vdsn(n=0,1,2,3),而M6、M7可认为工作在饱和区。在比较器刚进入比较阶段时,Vdsn几乎为0(n=0,1,2,3),所以M6、M7管起主导作用,因为通常管子尺寸较小,很容易就能产生上百毫伏的失调。M0~M3管的失调电压直接影响比较器的失调电压。

为减小失调电压,版图设计应该特别注意,需要匹配的管子尽量邻近放置,并且几何图形保持一致。另外,锁存器负载电容的失配也会导致较大的比较器失调,这个问题可以通过在锁存器的输出端串连缓冲器来解决。

4 比较器的版图实现及仿真结果

从比较器的原理图可以看出电路所使用的元器件众多,包括采样开关、采样电容、差分输入锁存比较器等,因此其版图实现必须特别考虑。模拟电路由于对噪声和工艺比较敏感,因而版图设计时需要特别小心。主要原因是制造工艺可能存在偏差,主要包括:晶圆本身掺杂浓度的不均匀,光刻时方向的不一致,温度和各种噪声的影响。元件这些非理想因素的影响,会导致电路的各种特性产生偏移。而所有这些工艺造成的非理想特性在设计上是无法消除的,只能通过版图设计的各种技巧加以减弱。

4.1 版图实现

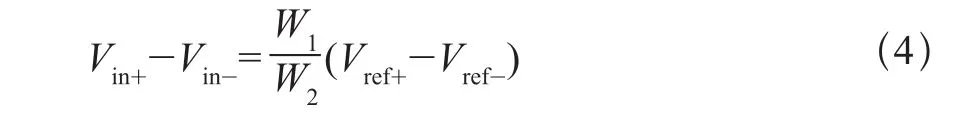

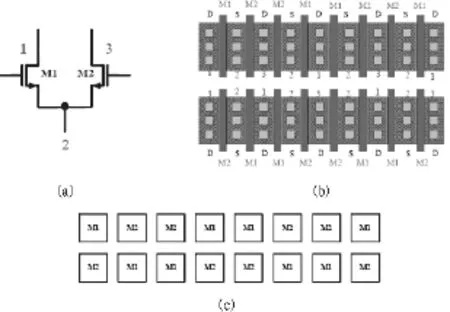

比较器差分输入对管的版图设计主要考虑的是对称性和方向的一致性,差分对两个晶体管的方向一致性可以使用交错排列方式达到。对于对称性来说,由于使用全差分结构,因此全差分的两部分应该完全对称。PMOS和NMOS电流镜中的晶体管应由相同大小的PMOS和相同大小的NMOS小晶体管并列而成。差分对的设计采用中心对称方法(Common Centroid)可以得到最佳的匹配度[4]。图3(a)为两个尺寸相同的差分对输入管,将MOS管等比例拆分成相等的8个小晶体管,再将这些晶体管以交错方式并联,如图3(b)所示,交错方法如图3(c)所示。这样就可以得到对于X轴和Y轴同时对称即中心对称的差分对。

图3 差分对晶体管的中心对称布局

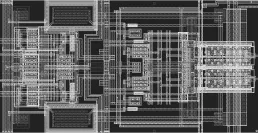

整个比较器电路采用在SMIC 0.18μm CMOS工艺实现的版图如图4所示,比较器版图中从左向右依次是采样开关、采样电容、动态锁存比较器和输出缓冲器,整个模块电路的版图面积为20μm×35μm。为了在版图设计中尽量减小失调电压,版图设计采用全差分结构,电阻采用多电阻并联结构,前置放大器和锁存比较器的输入MOS管和正反馈MOS管采用多插指结构。

图4 比较器的版图实现

4.2 比较器后仿真结果

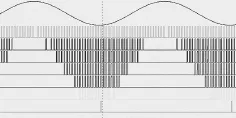

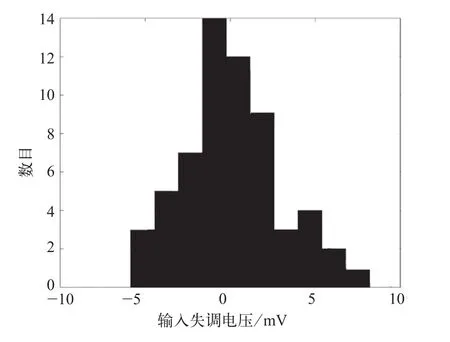

首先对比较器进行功能性验证。图5所示为该比较器运用于3-bit Flash电路中仿真得到的输入和输出量化结果。仿真条件为工作时钟200MHz,输入信号幅度100mV;仿真结果中,第一栏为验证信号差分输入波形,后七栏为3-bit Flash电路中采用温度计码格式的七个比较器输出结果,可以看出比较器正常工作。另外,根据SMIC 0.18μm CMOS工艺给出的阈值电压失配因子和电流失调因子,对比较器的输入失调电压进行Monte Carlo仿真,得到失调电压分布如图6所示。通过Monte Carlo仿真,发现失调电压分布范围完全落于-5mV~+7mV之内,集中分布区域为-3mV~+3mV以内。

图5 比较器的输入输出波形

图6 比较器失调电压分布范围

5 结论

本文设计了一种可应用于高速高精度模数转换器的比较器,对其正反馈预放大器和锁存器进行了分析和优化设计。仿真结果表明,该比较器达到了较高的锁存速度和较小的可分辨电压,可以满足200MSPS高精度流水线ADC的需求。

[1]Mikael Gustavsson,Jacob Wikner J,Nianxiong Nick Tan.CMOS Data Converters for Communications [M]. Boston:Kluwer Academic,2000.189.

[2]潘小敏,范晓捷,陈玉皎. 一种应用于高速高精度模数转换器的比较器[J]. 电子与封装,2010.

[3]T. Cho and P. Gray,. A 10 b, 20 Msample/s 35 mW pipeline A/D converter[J]. IEEE J. Solid-State Circuits, 1995,30(3):166-172.

[4]Alan Hasting. The Art of Analog Layout(影印版)[M]. 北京:清华大学出版社,2004.