通信测试卡中HDLC协议控制器的设计与实现

2012-07-26刘延飞杨铁阡

刘延飞 李 琪 杨铁阡 倪 亮

(第二炮兵工程大学专业基础实验中心,陕西 西安 710025)

0 引言

在航空航天领域中,大型地面测试设备测试数据具有传输量大、实时性要求高的特点。为了解测试设备与上位机的通信状况,需采用一种面向比特级的同步通信协议,实现数据传输过程的完全透明。高级数据链路控制(high level data link control,HDLC)协议具有上述优点,同时,它能保证传递到下一层的数据在传输过程中能够被准确接收,且一旦接收端接收到数据,就能立即传输下一帧数据[1]。

HDLC的一般实现方法是采用专用集成电路(application specific integrated circuit,ASIC)器件和软件编程等。采用ASIC器件设计比较简单,但灵活性较差;软件编程方法灵活,但占用处理器资源多、执行速度慢、实时性不易预测。现场可编程门阵列(FPGA)采用硬件描述语言处理信号,可以通过软件反复编程使用,能够兼顾速度和灵活性,还能并行处理多路信号,便于实时预测和仿真,所以在FPGA中实现HDLC协议的功能是一种较为合适的选择[2]。

根据课题具体要求,发送端和接收端的数据内容是固化的,只需检测测试设备能否与上位机进行正常通信,所以在数据传输过程中可以不加CRC校验[3],本文将介绍一种简化HDLC协议控制器的方法。

1 HDLC协议简介

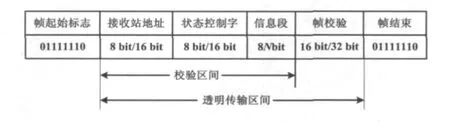

HDLC协议是通信领域中应用最广泛的协议之一,其面向比特的高级数据链路控制规程,具有差错检测功能强大、效率高和传输同步的特点[4]。在HDLC通信方式中,所有信息都是以帧的形式传送的。HDLC帧格式如图1所示。

图1 HDLC帧格式Fig.1 Frame format of HDLC protocol

1.1 标志字

根据HDLC协议规定,所有信息传输必须以一个标志字“01111110”开始,且以同一个标志字结束。由开始标志到结束标志之间构成一个完整的信息单位,称为一帧。接收方可以通过搜索“01111110”来探知帧的开始和结束,从而建立帧同步。在帧与帧之间的空载期,可连续发送标志字来作填充。

1.2 “0”比特插入技术

HDLC帧的信息长度是可变的,可传送除标志字以外的任意二进制信息。为确保标志字独一无二,发送方在发送信息时采用“0”比特插入技术,即发送方在发送除标志字符外的所有信息时(包括校验位),只要遇到连续的5个“1”,就自动插入一个“0”;反之,接收方在接收数据时,只要遇到连续的5个“1”,就自动将其后的“0”删掉。“0”比特插入和删除技术使得HDLC具有良好的传输透明性,可传输任何比特代码。

1.3 地址段及控制段

地址字段为8位,也可采用8的倍数进行扩展,用于标志接收该帧的栈地址。控制字段为8位或16位,发送方的控制字段用来表示命令和响应的类别与功能。

2 HDLC协议控制器的FPGA实现

基于FPGA实现的HDLC协议控制器主要包括发送和接收两个模块[5]。

2.1 发送模块的设计

发送端先将待发送的并行数据进行并串转换,然后由系统自动完成编码、“0”比特和标志字“7E”插入,最后将处理后的数据序列传递到发送端口。根据前文所述,由于每一帧的数据内容固定,因此,可将CRC结果视为固定值“E2、99”,直接将其添加到发送端数据序列即可。

2.1.1 发送模块工作原理

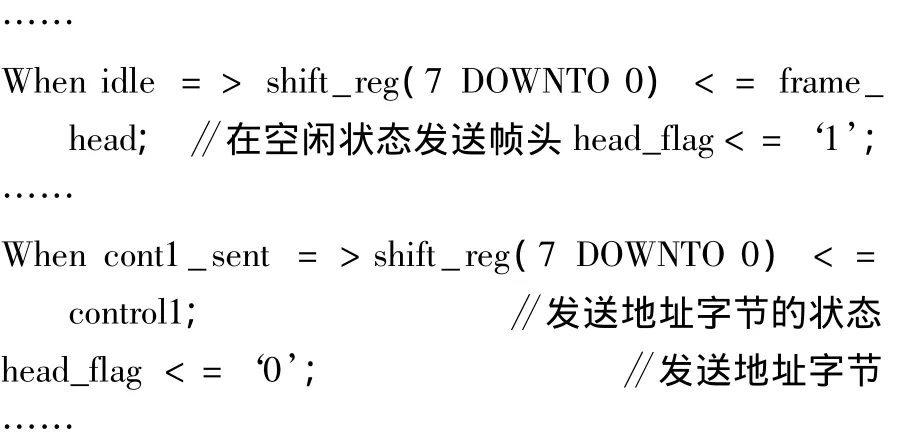

设计的代码主要由以下进程组成:① HDLC数据发送状态机状态转移进程,完成HDLC数据发送状态机各个状态对应的信号输出,包括标志信号和控制信号;②移位寄存器进程,通过移位实现数据并串转换,并按添零要求对串行数据序列做相应处理;③添零进程,当遇到连续的5个“1”时,自动进行添零处理,最后产生正确的、经过添零处理的HDLC数据序列。其部分源代码如下[6]。

在空闲状态,发送HDLC的帧头(7E);在地址发送状态,发送地址字节内容(5A 4A);然后转入控制字节发送状态,发送控制字节(54);进入HDLC帧尾发送状态,将帧尾(7E)发送出去,发送完帧尾,转入到空闲状态,等待新数据的到来。

2.1.2 试验结果和分析

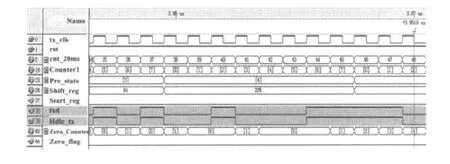

发送模块的试验仿真结果如图2所示。

图2 发送模块仿真结果Fig.2 Simulation result for transmitting module

当发送数据帧头“01111110”后,起始标志位start_flag置高,开始发送接收地址和控制字等数据内容。数据并串转换计数器counter1和添零计数器zero_counter开始计数,发送的数据依次存入移位寄存器shift_reg。数据发送信号txd,按照预定格式向串行数据序列hdlc_tx依次赋值,实现数据的正确发送。

2.2 接收模块的设计

接收端首先接收同步串行数据,然后由系统自动完成标志字的检测、去“0”,再将同步串行数据转换成1位并行方式输出。整个系统收发端使用同一个全局时钟。下面分别对接收模块各个部分进行介绍。

2.2.1 帧头检测模块

本进程用来检测帧头“7E”是否出现,如果检测到“7E”,则表明接收到一个完整的数据;反之,则继续接收数据[7]。

2.2.2 去“0”模块

本进程用来检测接收的数据是否包含插入的“0”比特,当检测到插入的“0”比特后,对其进行删除,并进行数据串并转换。

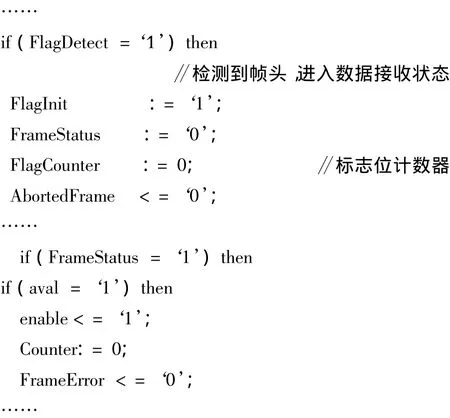

2.2.3 接收控制模块

本进程用于接收过程的控制,主要包括通过检测是否出现帧头来判断接收的数据是否为有效帧,以及产生接收使能信号。其部分VHDL代码如下。

2.2.4 试验结果和分析

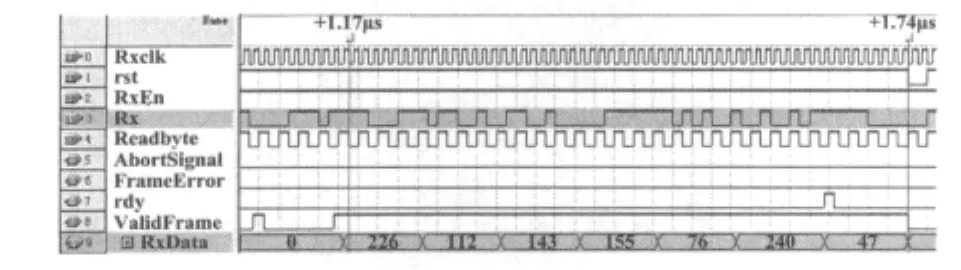

整个接收模块的试验仿真结果如图3所示。

图3 接收模块仿真结果Fig.3 Simulation result for receiving module

当接收的串行数据出现帧头“01111110”时,帧有效信号被拉高,开始进行串并转换,并将接收数据放入到接收缓存中,实现数据的存储。

3 结束语

针对某型地面测试设备通信测试卡的技术要求,文中提出了一种利用FPGA简化HDLC协议控制器的设计方案,并利用Altera公司的EP2C70F67218芯片来实现。

与传统的HDLC协议的实现方法相比,该控制器更加简单可靠;且由于数据帧传输过程中没有采用标准的CRC校验,使得数据传输速度更快。软件仿真和代码调试证明,本控制器能够应用于通信测试卡的测试,具有一定推广价值。

[1]黄国强.HDLC协议的FPGA实现及其在通信系统的应用[J].五邑大学学报,2008(22):40-44.

[2]徐涛.基于PCI的HDLC协议处理器的设计与优化[D].南京:东南大学,2005.

[3]刘岩俊,闫海霞.HDLC通讯协议中CRC的应用[J].电子测量技术,2010(3):21-23.

[4]李晓娟.基于FPGA的HDLC设计实现[J].现代电子技术,2007(6):35-37.

[5]应三丛.基于FPGA的HDLC协议控制器[J].四川大学学报:自然科学版,2008(40):116-120.

[6]潘松,王国栋.VHDL实用教程[M].成都:电子科技大学出版社,1999:158-169.

[7]徐欣,于红旗,易凡,等.基于FPGA的嵌入式系统设计[M].北京:机械工业出版社,2005:79-102.