基于FPGA的电容数据采集系统的设计

2012-07-03张印强孙冬梅程明霄

张印强,孙冬梅,程明霄

(南京工业大学 自动化与电气工程学院,南京 210009)

0 引言

电容式传感器广泛地应用于航空航天、军事、工业、医疗等领域, 在很多场合下电容量只有几pF到几百pF,传感器的输出信号微弱,如何提高测量灵敏度和信噪比成为微弱电容检测的关键[1]。

本文介绍了一种以FPGA为核心的电容数据采集系统,它利用基于载波调制的电荷放大电路完成电容/电压转换,抗干扰性较好。与传统的模拟检测系统相比,系统的载波生成和信号解调都在FPGA内部实现,载波稳定度更高, 解调误差更小,高分辨率A/D转换芯片的选用进一步保证了精度。

1 系统组成

系统以FPGA为核心集成了差动电容传感器、电源电路、信号调理电路、A/D 转换电路、D/A 转换电路等功能模块。系统整体结构如图1 所示。

图1 系统结构简图

信号调理电路主要用于对差动电容的变化进行载波调制、交流放大、滤波等预处理, 保证系统有较宽的测量范围, 为AD转换提供高质量的信号;AD转换电路负责把信号调理电路的输出信号转化为数字量,送FPGA进行处理;FPGA模块用于外设控制、载波生成、数字解调以及数据传输。

2 系统硬件设计

2.1 信号调理电路

2.1.1 电容/电压转换电路

为抑制共模噪声,增强抗干扰性能,系统采用连续积分型电容检测电路将差分电容的变化调制到正弦载波的幅度上[2,3],再利用相干解调的方法得到电容变化量,电路如图2所示。

C6和C8构成差分电容;R2与R3为反馈电阻,阻值相等,C4和C9为反馈电容,电容值相同;R1为标准电阻,用于设置放大器U1的增益;它们与U1、U2构成电荷放大器,将差分电容的变化量调制到载波幅度上。Vs为正弦载波信号,可表示为Vsinωct。一般反馈电阻R2很大,R2>>1/ωcC4,设U1的放大倍数为A,当差分电容变化时,可得到输出电压Vo的表达式如式(1)所示:

图2 电容/电压转换电路

电容/电压转换电路的输出正比于差分电容的变化量,电容的变化被调制到输出信号Vo的振幅之中。为保证测量精度以及小型化需求,U1选择AD8221,U2选择双通道精密运算放大器OP2177。AD8221是美国模拟公司推出的仪表放大器,其增益误差典型值小于20ppm且10KHz条件下的共模抑制比高达80dB。

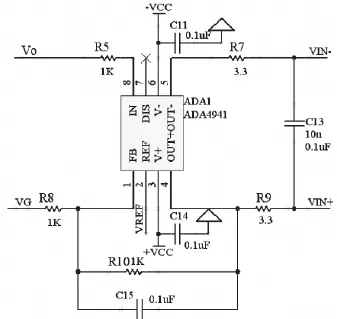

2.1.2 差分信号调理电路

由于A/D转换器必须采用全差分驱动输入,且差分输入的共模电压以及对差分输入的限制与基准电压有关,系统采用差分运算放大器ADA4941将电荷放大电路的输出转换为全差分信号后再与AD转换器的差分输入接口连接,差分信号调理电路如图3所示。

ADA4941采用正负10伏的电源进行供电,选用0.1μF的旁路电容降低干扰,通过调整R8和R10这两个电阻的阻值可调整运算放大器的增益。8脚为输入电压引脚,与电容/电压转换电路的输出引脚相连;2脚VRef设定差分信号的共模电压,这里为2.5V,5脚和4脚为差分输出信号,其输出电压如式(2)所示,差模输出电压如式(3)所示。

图3 差分放大电路

2.2 电源电路

系统所用到的电源主要有5V、3.3V、2.5V、1.8V、1.2V,选用SPX1117提供5V、2.5V、1.8V电压信号,选用AMS1117提供1.2V电压信号,利用开关型稳压电源芯片LM2576提供3.3V信号。3.3V电源电路如图4所示。

图4 3.3V电源电路

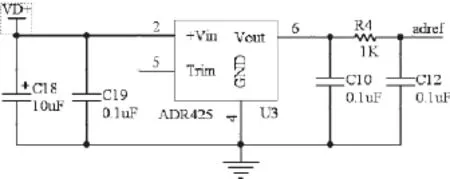

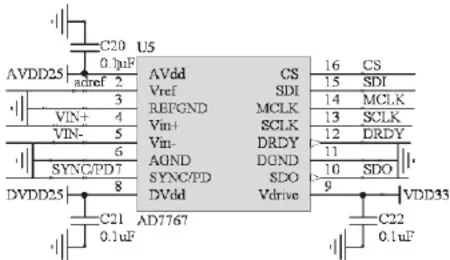

2.3 A/D转换电路

为保证数字解调的精度,选用高精度24位A/D 转换芯片AD7767对信号调理电路输出的差分驱动信号进行采样。AD7767为高性能24位过采样SAR型模数转换器,片内集成数字滤波器(包括线性相位响应),通过过采样输入来消除带外噪声,具有较宽的动态范围和输入带宽,适用于超低功耗数据采集应用。

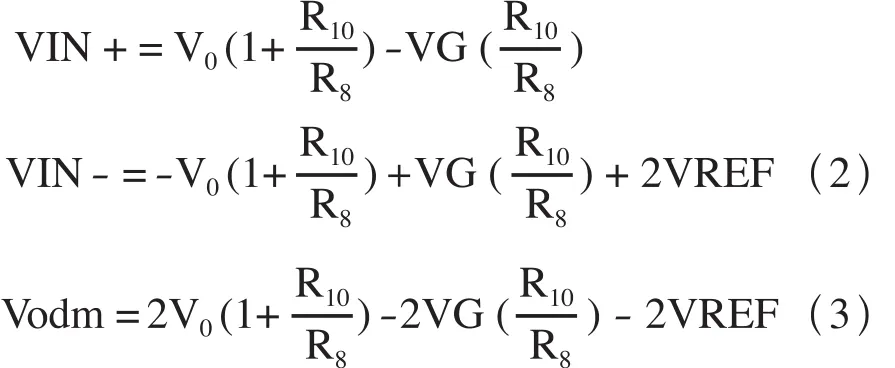

AD7767的工作电压为2.5V,标准基准电压为5V,为了保证A/D转换的精度,选用ADI公司的高精度电压参考源芯片ADR425提供基准电压,它具有低噪声、高精度和出色的长期稳定特性,输出电压5V。基准电压产生电路如图5所示,输入电压引脚和输出电源引脚均由去耦电容与地连接。

图5 基准电压电路

AD7767的外围电路如图6所示,参考电压由adref提供;其模拟工作电压和数字供电电压均为2.5V,I/O口电压为3.3V,均通过去耦电容与地连接。CS引脚为片选输入引脚,并充当SDO引脚的使能信号。数据输出采用串行接口方式,输出数据的协议为SPI协议。串行接口用到SCLK、MCLK、DRDY、SDI、SDO等信号,其中SCLK为串行时钟输入,MCLK为主时钟输入;DRDY为数据就绪信号,低电平有效;转换后的数据通过引脚SDO移位输出。SDI为串行输入引脚,主要用于多个器件的菊花链连接。时钟信号、片选信号、串行输出控制信号都由FPGA进行控制。

图6 AD7767的外围电路

2.4 D/A转换电路

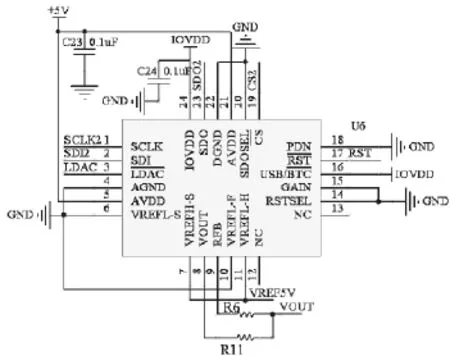

选用TI公司的DAC9881将FPGA内产生的数字载波信号转换成模拟信号,其电路如图7所示。

图7 D/A转换电路

TI 公司的DAC9881是高精确度的D/A转换芯片,分辨率为18 位,典型功耗为4mW[4]。

2.5 FPGA模块

FPGA芯片选用Altera公司生产的Cyclone系列的EP3C25E144C8, 其芯片模拟工作电压为1.2V和2.5V,分别为模拟锁相环PLL和模拟电压端供电;数字工作电压为3.3V和1.2V。控制程序存储在配置芯片EPCS16中。

3 系统软件设计

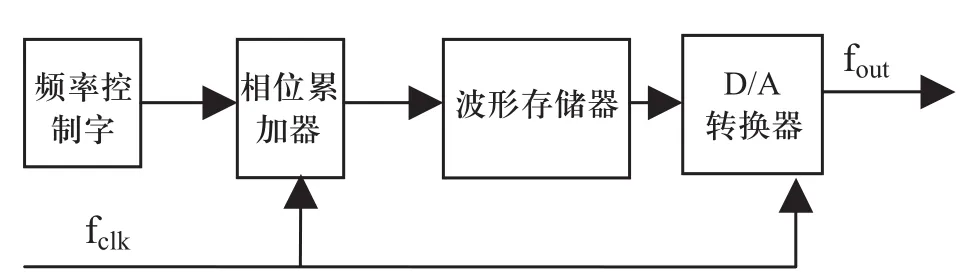

3.1 DDS算法

直接数字频率合成(DDS)技术[5]是一种从相位概念出发直接合成所需波形的一种新的全数字频率合成技术,其结构如图8所示。

图8 DDS的结构框图

DDS系统主要由相位累加器、波形存储器和数模转换电路等部分组成。相位累加器由加法器和累加寄存器级联构成,在时钟脉冲的控制下将频率控制字与累加相位相加,得到信号的新相位。相位累加器的输出作为波形存储器的相位地址,通过查找表得到对应的正弦值或余弦值,经数模转换器将数字量形式的波形幅值转换为模拟量。

DDS算法实现的部分代码如下:

always @ (posedge clk or posedge rst)

begin

if (rst)

ADD_1<=0;

Else if(we) //ADD_1为频率控制字

ADD_1<= data;

end

always @ (posedge clk or posedge rst)

begin

if (rst)

ADD_2<=0;

Else if(en)

ADD_2<=ADD_2+ADD_1; //相位累加器

end

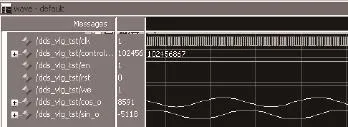

DDS载波生成信号的modelsim仿真结果如图9所示,sin_o和cos_o代表正弦值和余弦值。

图9 DDS模块的modelsim仿真图

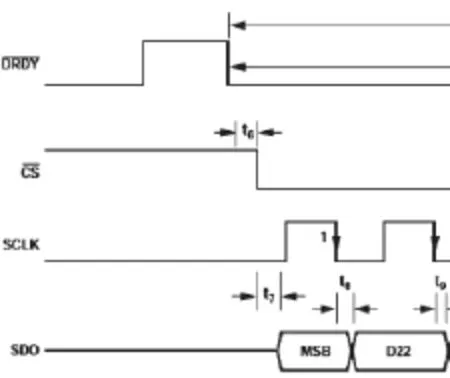

3.2 AD7767的采样控制

AD7767通过串行数据输出引脚(SDO)输出其数据转换结果。SCLK是该器件的串行时钟输入;DRDY线用作状态信号;CS信号是SDO引脚的选通信号。数据读出的工作时序如图10所示。

有效的数据准备好时,DRDY被置为低电平。CS引脚变为低电平后开始启动串行数据传输,数据在时钟信号控制下串行输出,FPGA 提供AD7767工作所需的时钟信号和控制信号。在QUARTUS中设计的A/D控制模块如图11所示。

图10 ADS1278的串行时序图

图11 AD控制模块图

4 结束语

基于FPGA的电容数据采集系统运用数字技术生产载波和实现解调,结构简单,精度高,具有一定的实用价值。

[1] 刘俊, 徐佩, 石云波. 微弱电容信号的离散频率测试方法及其硬件电路的实现[J]. 兵工学报, 2005, 26(4): 500-503.

[2] 周晓奇, 郑阳明, 金仲和, 等. 基于FPGA的数字式电容检测系统[J]. 传感技术学报, 2008, 21( 4): 698-699.

[3] 庞士信, 王超, 匡石. 基于FPGA的硅电容传感器调理模块设计[J]. 仪表技术与传感器, 2010, (10): 1-2.

[4] 魏永旺, 罗海波, 邹彦. 18位数/模转换芯DAC9881的原理与应用[J]. 现代电子技术, 2009, (14): 167-169.

[5] 汤文亮. 基于CORDIC算法的高速高精度DDS研究与实现[J]. 制造业自动化, 2011, 33(3): 104-106.