基于ΣΔ调制的Tetra基带前端设计

2012-01-14李文龙聂紫晨许金勇聂景楠

李文龙,聂紫晨,许金勇,聂景楠

(1.解放军理工大学,江苏南京210007;2.西安电子科技大学,陕西西安710126;3.总参谋部第63研究所,江苏南京210007)

0 引言

Tetra是欧洲电信标准协会(ETSI)提出用于应急场景无线通信调度的数字集群通信系统[1,2]。在开发基于软件无线电架构Tetra数字接收机的过程中,π/4 DQPSK数字调解器、各类卷积编解码算法实现一直是研究重点,而这些研究的默认前提是接收信号已经被数字化了,但数字化过程是否优化却并未被充分关注。通常在模数转换之前需要用模拟抗混叠滤波器来保证采样后信号频谱不会由于混叠而失真。A/D转换分辨率越高,信号/量化噪声比也越高,但对抗混叠滤波器阻带衰减要求也越高,因为它对混叠噪声更敏感。为降低抗混叠滤波器复杂性(比如用RC滤波电路实现),只能放松对其阻带衰减要求,相应地也要减少A/D转换位数。

1 ΣΔ调制的降噪设计分析

1.1 过采样与转换器分辨率的转化

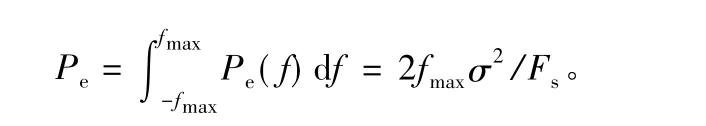

假设基带输入信号最高频率为fmax,采样速率为Fs,A/D转换过程中引入固有量化噪声功率为:σ2=q2/12=2-2(B-1)/12(归一化)。其中,q为量化步长,B为A/D位数。对于随机模拟输入信号,量化噪声能量均匀地分布在有效带宽(0,Fs/2)内,量化噪声功率谱密度为:Pe(f)=σ2/Fs。在基带内的噪声功率为:

如果提高采样速率(采用过采样),就可以使量化噪声能量分布在更宽的频带内,这样便降低了感兴趣的信号频带内量化噪声功率,降低了同样信号/量化噪声比情况下所需A/D转换器位数。以奈奎斯特采样率(Fs=2*fmax)下所需A/D分辨率为基础,当采用过采样比为256的采样率(Fs=256*2*fmax)时,功率谱密度变为原来的1/256,原来信号带宽内的噪声功率也为原来的1/256,信号/噪声比提高至原来的256倍(约24 dB)。对于峰值刚好充满A/D范围的正弦波输入而言,每增加一位所提高的信号/噪声比为[7]:SQNR=6.02*B+1.7 dB,相当于增加了将近4 bit,即,在256倍奈奎斯特采样率下,如要求A/D输出相同的信号/量化噪声比,分辨率可以减少4位。

然而,仅靠过采样降低A/D转换分辨率代价太大,效果也不够明显。在过采样基础上进行噪声整形,即可将低频段噪声移到信号频带之外的高频段,以便后续将其滤除,即为ΣΔ调制。

1.2 ΣΔ调制的噪声整形

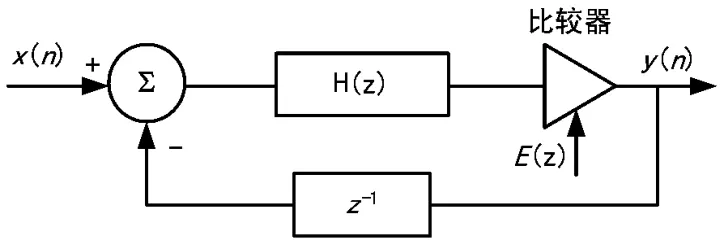

对于过采样后的离散信号,其相邻样点之间相关性得到增加,可以用较少比特位数来表示而并不降低信号的保真度,这是传统Δ调制器的实现原理。如果在传统Δ调制器中增加反馈环路和积分部件,即可获得具有噪声整形功能的ΣΔ调制器。图1所示为典型的ΣΔ调制器结构。

图1 典型ΣΔ调制器结构

图中,x(n)为过采样后的离散信号,y(n)为一比特数字输出,E(z)为量化噪声的z变换,H(z)为噪声传递函数,实际上可以看成是一个噪声调制滤波器,它能够将低频段量化噪声调制到高频段,改变噪声功率在频带中的分布,使得信号通过抽取滤波器后即可有效地滤除噪声。

ΣΔ调制器可以用噪声传递函数来描述。输入信号经过采样处理和ΣΔ调制器噪声滤波,输出信号可表示为:

Y(z)=X(z)+E(z)H(z),

式中,X(z)为输入信号的z变换,Y(z)为输出信号的z变换。噪声传递函数实质上是在直流处有一零点的高通滤波器,其作用是将量化噪声能量移向高频。噪声传递函数的选择涉及到噪声整形效果,也关系到相位特性、实现复杂度等问题,对比了2类噪声传递函数:H1(z)=(1-z-1)n和H2(z)=z-1(1-z-1)n/(1-(1-z-1)n)(n为阶数),最后选定3阶H2(z)=z-1(1-z-1)3/(1-(1-z-1)3)为本方案所用。

2 降速抽取滤波设计

输入信号经过过采样和ΣΔ调制之后,其输出含有较小的带内噪声以及很大的带外量化噪声,通过低通数字滤波器可将其滤除。但此时采样速率较高,需要通过抽取的方法对输出信号进行降速,然后完成低通滤波。降速抽取滤波器包括一个数字抗混叠滤波器g(k)以及一个抽取器,抽取因子为M。抽取器的功能是将采样频率从Fs降到Fs/M。为了避免输出低频段信号发生频谱混叠,在输出信号前面加一个带限滤波器,使频率不超过Fs/2M。

当抽取速率变化较大时,可采用二级或多级抽取滤波器进行采样速率转换,它能够渐进地降低采样速率。多级抽取系统抽取因子可表示为:M=M1*M2*M3…MI,其中MI代表各级抽取因子,它是一个整数。对于M>>1,采用多级结构抽取滤波器能够大大降低总的计算量和存储要求,减轻滤波器的设计难度。总的数字滤波器指标可表述为:

通带:0≤f≤fp;阻带:Fs/2M;通带波纹:δp;阻带波纹:δs;其中 fp<Fs/2M,Fs是原始采样频率,fp是原始信号中感兴趣的最高频率。

对于一个多级抽取滤波器,为保证总的滤波效果,各级滤波器指标分别为:

通带:0≤f≤fp;阻带:(Fi-Fs/2M)<f<Fi-1/2,i=1,2,…I;通带波纹:δp/I;阻带波纹:δs。

3 Tetra系统基带模数转换的优化设计

3.1 设计要求

Tetra系统定义了如下的无线传输参数,调制方式:π/4 DQPSK;调制符号传输速率:18 ksps;信道间隔:25 kHz。考虑基带收发信机的整体数字设计,取每个调制符号以8个样点表示,即基带信号的采样率为18 ksps*8=144 ksps。综合考虑过采样比和系统实现复杂度,取过采样速率为Fs=2.304 Msps,ΣΔ调制器噪声传递函数 H(z)=z-1(1-z-1)3/(1-(1-z-1)3)。过采样输出后需要进行1/16速率的抽取滤波器处理,将采样速率降为144 ksps,按照分级抽取方法分别设计实现比值为整数因子M1=8和M2=2的滤波器,形成一个2级的抽取因子为M=M1*M2=16的FIR滤波器。

2级抽取滤波器的总体指标为:fp=23 kHz;fs=27 kHz;δp=0.01 dB;δs=74 dB。设计中可以分别计算出第1级和第2级低通滤波器的设计指标。

3.2 设计过程及结果

对于ΣΔ调制器,根据给定的噪声传递函数H(z)=z-1(1-z-1)3/(1-(1-z-1)3),可以得到其离散冲激响应,进而完成设计。

对于抽取滤波器第1级,M1=8;输出采样频率F1=Fs/M1=2 304/8=288 ksps;阻带频率fs1=F1-Fs/2*M=288-2 304/(2*16)=216 kHz;Δf1=(fs1-fp)/Fs=(216-23)/2304=0.083 77;δp1=δp/2=0.005 dB;δs=74 dB。这样可以用最优 FIR滤波器设计方法设计出通带频率fp=23 kHz、阻带频率fs1=216 kHz、采样频率 Fs=2.304 Msps的第1级低通滤波器。

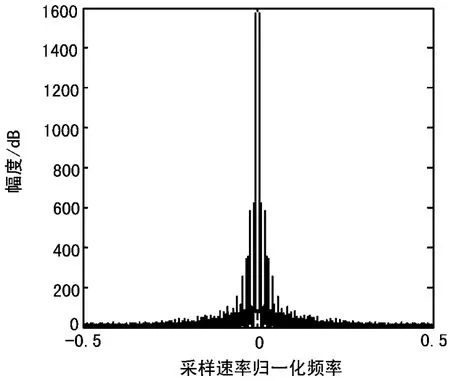

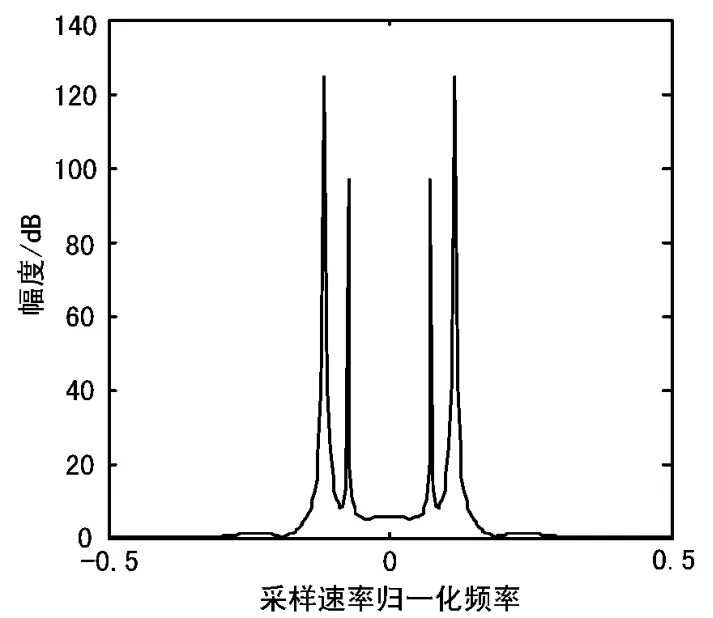

第2级抽取滤波器,M2=2;输出采样频率F2=F1/M2=288/2=144 ksps;阻带频率 fs2=F2-Fs/2*M=144-2 304/(2*16)=72 kHz;Δf2=(fs2-fp)/F1=(72-23)/288=0.170 14;δp1=δp/2=0.005 dB;δs=74 dB。可以用最优FIR滤波器设计方法设计出通带频率fp=23 kHz、阻带频率fs1=72 kHz、采样频率Fs=288 ksps的第2级低通滤波器。2级抽取滤波器设计结果分别如图2和图3所示。可以看到,阻带衰减大于74 dB意味着达到了12 bit分辨率对应的信号/噪声比水平,而由于使用了ΣΔ调制器的噪声整形手段,大大降低了对模拟抗混叠滤波器的要求。

图2 第1级抽取滤波器幅度谱

图3 第2级抽取滤波器幅度谱

为直观展示ΣΔ调制器的噪声整形效果,随意构造一个基带信号:x(t)=0.8sin(2πf1t)+1.5sin(2πf2t),其 中,f1=10.598 4 kHz,f2=16.588 8 kHz。考察其模数转换过程中各阶段的频谱,取奈奎斯特采样率 Fsn=72 ksps,过采样速率Fso=2 304 ksps,(过采样比为32),仿真得到归一化频谱如图4、图5和图6所示。

图4 过采样量化后信号频谱

图5 ΣΔ调制噪声整形后信号频谱

图6 抽取滤波后输出信号频谱

图4和图5采样率为2 304 ksps,图6采样率为288 ksps。结果表明,原始输入信号经历过采样ΣΔ调制之后,噪声功率被扩展至更宽的频率域,经过降速抽取滤波器,大部分噪声功率被去除。

4 结束语

基带数字接收机前端模数转换设计直接影响到接收机的成本和性能,采用过采样ΣΔ调制噪声整形和降速抽取滤波的方法,对Tetra系统基带接收机进行了优化的模数转换设计,设计结果大大降低了接收机对模拟抗混叠滤波器要求,同时显著减小了量化噪声功率。通过MATLAB仿真验证了设计的正确性和有效性,对Tetra数字集群系统设计实现具有重要参考意义。

[1] 郑祖辉,鲍智良,经明,等.数字集群移动通信系统[M].北京:电子工业出版社,2002.

[2] ETSI:ETS 300 392-2 Radio Equipment and Systems(RES),Trans-European Trunked Radio(TETRA)Voice plus Data,Part 2:Air Interface(AI)[S],1996.

[3] AZIZ P M,SORENSEN H V,SPIEGEL J V D.An Overview of Sigma-delta Converters [J].IEEE Signal Processing Magazine,1996,13(1):61-84.

[4] LADDOMADA M.Generalized Comb Decimation Filters for ΣΔA/D Converters:Analysis and Design [J].IEEE Transactions on Circuits Systems I,2007,54(5):994-1005.

[5] 李冬梅,高文焕,张鸿远,等.过采样Sigma delta调制器的研究与仿真[J].清华大学学报(自然科学版),2000,40(7):89-92.

[6] 郝志刚,杨海钢,张翀,等.一种改进的适用于 Sigma-Delta ADC的数字抽取滤波器[J].电子与信息学报,2010,32(4):1012-1016.

[7] IFEACHOR E C,JERVIS B W.数字信号处理实践与方法(第2版)[M].罗鹏飞,杨世海,朱国富,等译.北京:电子工业出版社,2004.

[8] 楼顺天,于卫,闫华梁.MATLAB程序设计语言[M].西安:西安电子科技大学出版社,1997.