一种2.4GHz全集成SiGe BiCMOS功率放大器

2011-09-19刘炎华赖宗声

阮 颖 刘炎华 陈 磊 赖宗声

①(华东师范大学微电子电路与系统研究所 上海 200062)

②(上海电力学院计算机与信息工程学院 上海 200090)

1 引言

目前,我国大力推进核心电子器件、高端通用芯片等自主创新研究。其中,应用于新一代宽带无线通信系统中的多频多模无线收发器关键模块受到各类研究机构的广泛重视。作为射频前端关键模块,功率放大器(PA)是无线发射机的核心。PA设计通常采用基于GaAs,InP等III-V族材料的高电流密度和高击穿电压器件,但它们热传导性差、成本较高且难于集成,尤其是射频前端与基带电路的集成。CMOS技术虽有利于PA的集成应用,但由于MOS的特征频率低、功率密度小和寄生大,RF CMOS PA在高频下难以获得高增益和高效率。近年来,新兴的 SiGe BiCMOS工艺技术由于结合了 SiGe HBT频率特性、功率密度、噪声的优势以及 RF CMOS成本和集成的优势,使基于SiGe BiCMOS工艺技术的 PA线性度和效率提升设计及片上集成设计成为了研究的热点[1-4]。从目前报道的PA的文献[4-9]来看,国内研究机构近年来基于 SiGe BiCMOS工艺技术进行了PA的设计尝试,但是基本采用国外工艺线进行片外集成设计,缺乏成熟的设计经验,与国外存在一定差距。本文设计了一种应用于2.4 GHz频段WLAN 802.11b/g的全集成PA,并在宏力半导体(GRACE)2010年建成的0.18 μm SiGe BiCMOS 工艺线上进行了试验流片。该PA采用了自适应的线性化偏置技术,同时实现了温度补偿功能。本文第2节将阐述SiGe BiCMOS PA电路结构和设计思路,第3节将介绍PA的偏置电路设计,重点阐述 PA线性化和温度稳定的设计技术。PA的测试结果将在第4节中介绍。

2 SiGe BiCMOS功率放大器电路设计

根据2.4 GHz 频段的WLAN 802.11b/g 协议的要求,PA的典型发射功率一般为10-20 dBm。此外,由于WLAN 802.11b/g 采用CCK和OFDM的调制方式,PA需要3-6 dB的功率回退来满足其频谱模板的要求,以避免码间干扰和信号失真。为了满足协议要求,同时兼顾功率效率、增益等主要性能,本文提出的 PA采用共射级两级单端级连拓扑结构,工作类型为Class AB,输出1 dB压缩点的功率为20 dBm,功率增益大于20 dB,效率大于20%。该PA包括功率放大、匹配和偏置电路。

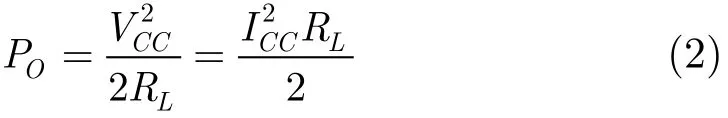

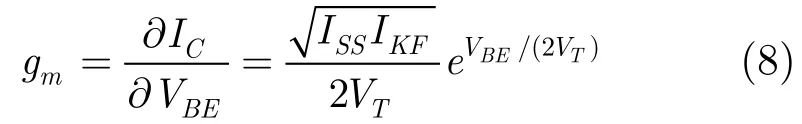

本文所给出的PA如图1所示。第1级为驱动级,主要为后级提供足够的驱动,设计时使第1级工作在Class A以提高整个功率放大器的线性度,功率增益为20 dB。第2级为功率放大级,主要获得足够的功率输出,功率增益为5 dB。由于PA的效率主要由第2级决定,因此使第2级工作在Class AB状态。

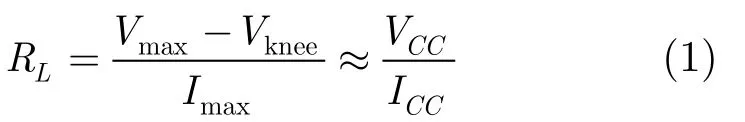

根据Cripp’s的负载线理论[3],优化的负载阻抗RL为

其中Vmax,Imax分别为HBT允许的最大电压和电流,Vknee为膝点电压。PA的输出功率PO为

图1 SiGe BiCMOS PA 电路结构示意图

根据式(1),式(2)计算ICC的取值,并与效率折中决定功率晶体管Q1,Q2的发射极尺寸分别为250 μm2和1140 μ m2。工艺提供了3种类型SiGe HBT,如表1所示。按照琼森极限(Johnson Limit)的约束,SiGe HBT 的特征频率fT和集-射极击穿电压BVCEO的乘积相对恒定。对于PA设计而言,需充分考虑SiGe HBT的抗电冲击能力,而对其速度性能要求不高。根据PA的集电极电压摆幅、工作频段范围以及输出功率要求,选取了射极功率密度达0.3 mW/μm2的HV型SiGe HBT。

表1 GRACE 0.18μmBiCMOS工艺中SiGe HBT的类型

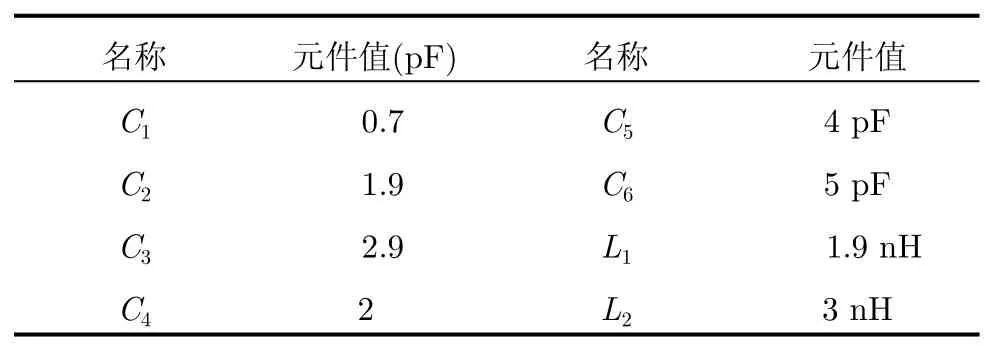

在匹配电路的设计中,分别由C1,C2,L1和C3,C4,L2构成两级的输入匹配,均采用高通的T型拓扑结构,以提高低频稳定性。由C5,C6,L3构成了π型输出匹配,相比简单的L型匹配,它通过中间阻抗降低阻抗转换比率对片上匹配元件尤其是电感Q值的要求,表2给出了匹配电路中主要元件的参数。此外,Rf和Cf串接Q1的基极与集电极之间形成反馈环路进一步减小低频增益,提高 PA的稳定性。传统单片集成 PA采用片外电感和电容作为输出匹配元件和集电极扼流圈以减小损耗[5,6],但片外元件使面积和成本显著增加。工艺所提供的片上螺旋电感在2.4 GHz工作频率Q值超过12,且直流阻抗较低。本设计中采用片上螺旋电感和MIM电容,以实现全集成的PA。

3 SiGe BiCMOS PA自适应偏置电路设计

目前已有多种 PA线性化技术报道,比较常见的有包络恢复和消除技术、包络跟踪[5]、自适应偏置技术[6,8]和预失真[9]等,本文基于自适应偏置技术设计了 PA线性化和温度稳定的偏置电路。电路具有结构简单,不增加芯片面积、直流功耗和插损的优点。

表2 匹配电路中主要元件参数

3.1 线性化设计

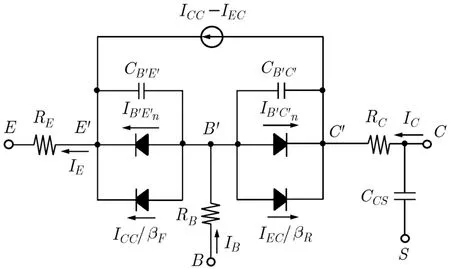

图2是SiGe HBT的Gummel-Poon大信号等效模型,SiGe HBT的失真主要由跨导gm和基-集极极间电容CB'C'引起[4]。大信号条件下,由于HBT基-射结二极管的箝位特性HBT的gm随着PA输入功率Pin的增加而减小,从而引起增益压缩(AM-AM)和相位失真(AM-PM)。尤其是在HBT效率相对较高的功率饱和区域,gm值的变化将导致PA的线性度恶化。

图2 SiGe HBT 的Gummel-Poon等效模型

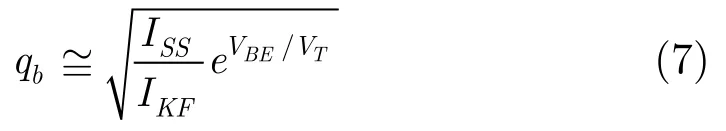

通过分析图2所示等效模型,可得

忽略二极管电流IEC/βR和IB'C'n,则IC可近似表示为

其中ICC和IEC分别为

而在基区高注入时,

因此

根据上述分析,本文从补偿大信号下HBT器件失真的角度提出结构简单的自适应偏置电路,使HBT的VBE随Pin增加而适当增大,从而提高大信号条件下HBT的gm,达到减小增益压缩和相位失真,提高PA线性度的目的。

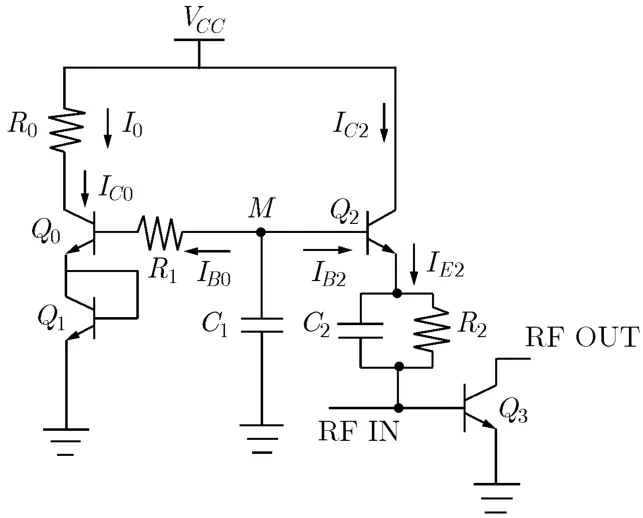

如图3所示,主要由旁路电容C1和晶体管Q2的基-射结二极管构成了简单的线性化结构。C1使从功率晶体管Q3基极看进去的输入阻抗减小,从而增加了进入线性化电路的射频功率[7]。在 2.4 GHz的工作频率,R0与Q0,Q1的并联阻抗值远大于C1的阻抗,使M点的绝大部分RF信号通过了C1,从而使M点的直流电位基本恒定。当输入的射频功率增加,Q3的基-射极电压VBE3下降,跨导gm减小。与此同时Q3集电极电流增大,基极电流IB3增大。C1使进入Q2基极节点的功率增加,Q2的基极电流IB2增大,使Q2的基-射极电压VBE2减小。这时,由于M点的直流电位固定,则VBE3增大。因此VBE2的减小补偿了VBE1的降低,使Q3的gm增加,从而使PA的线性度得以提高。

图3 具有线性化及温度不敏感功能的偏置电路

3.2 温度稳定性设计

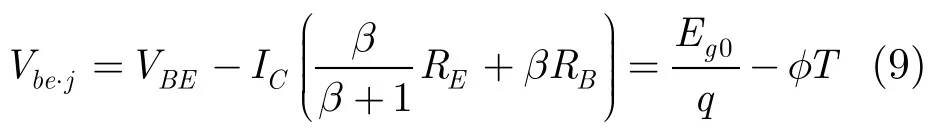

PA的温度稳定性是设计需考虑的另一个重要因素。根据HBT的集电极电流IC与结温T的关系,推导PA中功率HBT的基-射极电压VBE与IC的关系如式(7)

其中Vbe⋅j为基-射(B-E)结电压,Eg0为基区材料 0 K时的禁带宽度,φ为热电反馈系数,β为电流增益,T为结温。

当Pin增大时,B-E结功率耗散随着IC的增大而增加,从而结温上升,导致一定IC下所需的实际VBE值减小。当达到一定阈值时,HBT将发生热崩溃。

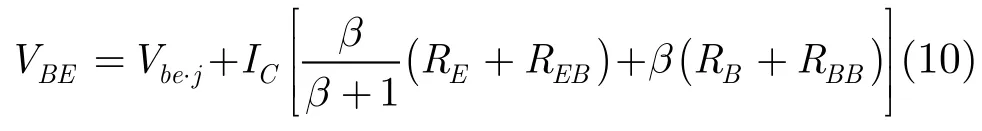

为了防止热崩溃,如式(10)所示,可采用增加基极镇流电阻RBB或射极镇流电阻REB来补偿VBE随结温升高而下降,提高HBT的热稳定性。

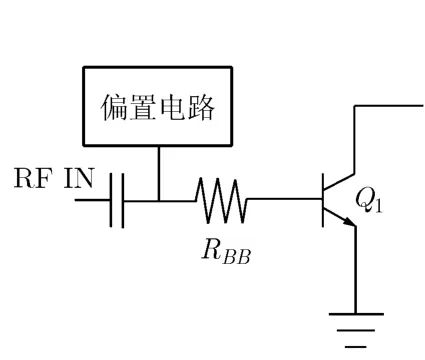

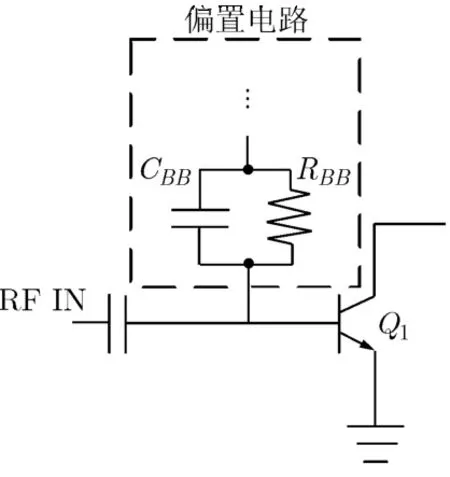

随着REB的增加,射极电阻消耗的功率(RE+REB)将使PA的功率效率显著下降,并且使得输出电压摆幅降低。由于基极电流IB远小于IE,可以选择阻值相对较大的基极镇流电阻而不会引起显著的直流功耗,如图4所示的传统的基极镇流电阻。然而该方法将镇流电阻RBB直接接在输入RF信号通路上,难以避免较大的射频损耗。如图5所示,为了克服此弊端,本文的设计中将基极镇流电阻RBB从RF通路上移开,而置于HBT的基极偏置电路的DC通路上,该电阻同时作为PA自适应线性化电路一部分。仿真表明RBB取16 Ω/finger,且两端并联上适当的旁路电容CBB(596 fF),能够降低基极镇流电阻对功率增益的影响,以较小的直流功耗和射频损耗而有效地防止热崩溃。

图4 传统的基极镇流电阻连接方式

图5 本设计的基极镇流电阻连接方式

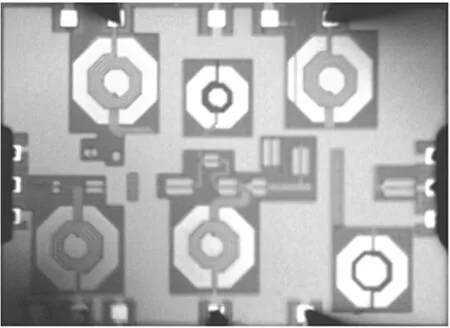

4 芯片设计与测试

采用GRACE 0.18 μm SiGe BiCMOS 工艺进行设计与流片,图6是PA芯片的显微照片,芯片内集成了全部的匹配电路、偏置电路和功率放大电路,面积为1.2 mm×1.3 mm。采用3.3 V直流电源供电,在Cascade S300探针台上进行了在片测试。

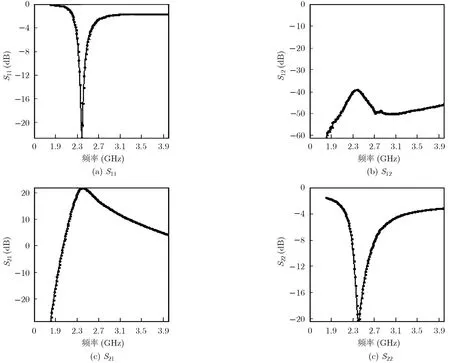

用Agilent E8363B 40 GHz 网络分析仪进行S参数测试,图7是S参数测试结果。在2.4-2.5 GHz的工作频段内,输出回波损耗S22低于-15 dB,输入回波损耗S11的最小值达-18.3 dB。反向传输系数S12低于-40 dB,正向传输系数S21高于21.5 dB ,峰值达23 dB。表明本文提出的PA采用全片上元件实现了优良的输入输出匹配。

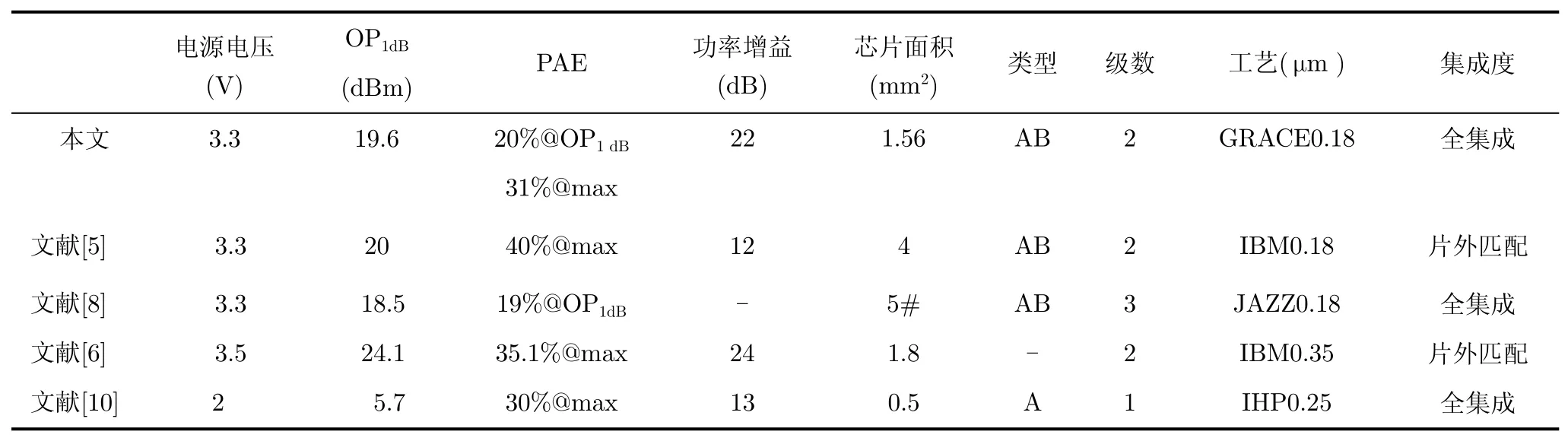

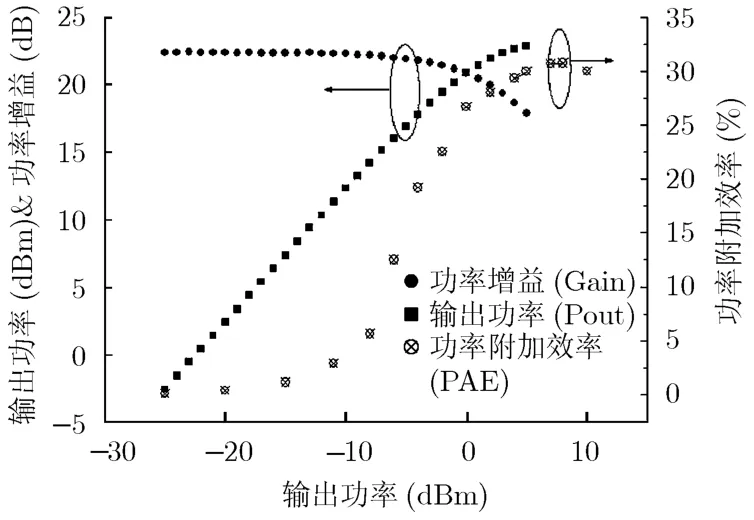

用Agilent E4438C信号发生器、E4419B功率计、34401电流表等测量装置进行了大信号测试。图8为功率扫描的测试结果,输出1 dB 压缩点的输出功率为19.6 dBm,功率附加效率为20%,功率增益为 22 dB。测试结果表明,本文提出的全集成Class AB PA具有良好的线性度和效率。与最近发表的2.4 GHz SiGe BiCMOS PA 设计对比如表3所示。

图6 单片全集成 SiGe BiCMOS PA芯片实物照片

图7 S参数的测试结果

5 结论

本文基于国内第1条0.18 μm SiGe BiCMOS工艺设计了一款单片全集成的 2.4 GHz功率放大器。采用了自适应的偏置技术和灵活的温度稳定设计,在不增加面积和插损的情况下,提高了功率放大器的线性度和温度的稳定性。芯片实现匹配电路、偏置电路和功率放大电路的片上全集成。测试结果表明:S21高于21.5 dB,S22低于-15 dB,S11低至-18.3 dB,S12低于-40 dB,输出1 dB 压缩点的输出功率为 19.6 dBm,功率附加效率为 20%,功率增益为22 dB。

表3 本文PA与最近发表的SiGe BiCMOS PA性能比较

图8 功率扫描的测试结果

[1]Huang C W,Doherty M,Antognetti P,et al..A highly integrated dual band sige BiCMOS power amplifier that simplifies dual-band WLAN and MIMO front-end circuit designs[C].Microwave Symposium Digest (MTT),Anaheim,CA,USA,May 23-28,2010:256-259.

[2]Eshghabadi F,Dousti M,Temcamani F,et al..A 2.4-GHz front-end system design for WLAN applications using 0.35 μm SiGe BiCMOS technology[C].3rd International Conference on Information and Communication Technologies:From Theory to Applications,Damascus,Syria,Apr.7-11,2008:1-5.

[3]Cripps S C.RF Power Amplifier for Wireless Communications[M].2nd edit,Norwood,MA,USA,Artech House,Inc,2006:21-27.

[4]Haitao Z,Huai G,Yintat M,et al..A novel high efficiency and linearity power amplifier with over-voltage protection[C].Microwave Symposium,Hawaii,USA,June 3-8,2007:147-150.

[5]Feipeng W,Kimball D F,Lie D Y,et al..A monolithic high-efficiency 2.4-GHz 20-dBm SiGe BiCMOS envelopetracking OFDM power amplifier[J].IEEE Journal of Solid-State Circuits,2007,42(6):1271-1279.

[6]Peng Yan-jun,Song Jia-you,Wang Zhi-gong,et al..A low-cost on-chip bias-current-control SiGe BiCMOS power amplifier at 2.4 GHz[C].Asia-Pacific Microwave Conference,Hong Kong,China,Dec.16-19,2008:1-4.

[7]Ruan Ying,Chen Lei,Liu Yan-hua,et al..A 2.4 GHz monolithic SiGe power amplifier for Wireless-LAN transceiver[C].Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics,Shanghai,China,Sep.22-24,2010:287-290.

[8]Liao Hsin-hsing,Jiang Hao,Shanjani P,et al..A fully integrated 2×2 power amplifier for dual band MIMO 802.11n WLAN application using SiGe HBT technology[J].IEEE Journal of Solid-State Circuits,2009,44(5):1361-1371.

[9]Lee Yong-sub,Lee Mun-woo,and Jeong Yoon-ha.A wideband analog predistortion power amplifier with multibranch nonlinear path for memory-effect compensation[J].IEEE Microwave and Wireless Components Letters,2009,19(7):476-478.

[10]Kaynak M,Tekin I,and Gurbuz Y.Fully integrated low-power sige power amplifier for biomedical applications[J].IETMicrowaves,Antennas&Propagation,2011,5(2):214-219.