基于FPGA的VME总线接口的设计与实现

2011-06-28邵文建

邵文建,李 超

(船舶重工集团公司 723所,扬州 225001)

0 引 言

许多新的雷达体制和雷达技术的出现,对雷达信号处理的运算速度和实时性提出了很高的要求,同时对接口总线的传输速度提出了更高的要求。因此,设计一种高速传输的接口总线对信号处理有着重要的现实意义。

虚拟机器环境(VME)总线具有高速异步传输、支持多种寻址方式、多种数据宽度、能够独立支持至少32位地址和32位数据总线、支持集中式和分布式中断的优点,最高传输速度可达 500 Mb/s。VME总线是目前应用最为广泛、获得各方支持最多的并行标准总线。由于VME具有总线众多的功能、强大的兼容性、并行性和高可靠性,因此在图像处理、军事通信、雷达信号处理等众多领域有广泛应用。本文采用Altera公司高密度的Stratix系列现场可编程门阵列(FPGA)来实现VME总线接口,对VME总线接口设计问题进行了深入研究。

1 VME总线

VME总线是由Motorola等几大公司在VERSA总线和欧式卡基础上提出的。VME的数据传输机制是异步的,有多个总线周期,地址宽度是16、24 、32、40 或 64 位,数据线路的宽度是 8、16、24 、32、64位,系统可以动态地选择地址和数据线的宽度。此外还有 UnalignedData传输能力、误差纠正能力和自我诊断能力,用户可以定义I/O端口。

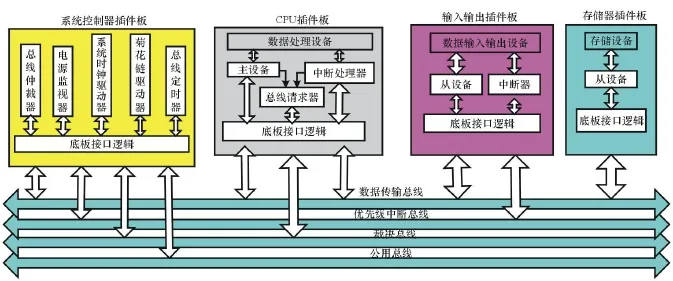

VME总线的功能构架如图1所示。各个功能模块虽然各有分工,但是要想集体配合,还需要总线的支持。主设备用于启动数据传输总线周期,以便和从设备之间传递数据。从设备用于检测主设备启动的数据传输总线周期,当数据传输总线周期指定由它参与时,就和主设备传递数据。

VME总线主要由数据传输总线、仲裁总线、优先级中断总线和公用总线组成。数据传输总线是一个高速异步平行数据传输总线,能传输数据和地址信号;仲裁总线是为确保在特定的时间内只有一个模块占用数据传输总线而设定的,工作在其上的请求模块和仲裁模块将负责协调各模块发出的指令;优先权中断总线是处理各模块中断请求的总线,各种中断请求在VME中被分成了7个等级,根据等级高低,依次对信号线进行中断工作;公用总线负责系统的一些基本工作,包括对时钟的控制、初始化、错误检测等任务。

图1 VME总线系统的功能结构图

数据传输总线分为3类:寻址信号线、数据信号线和控制信号线。

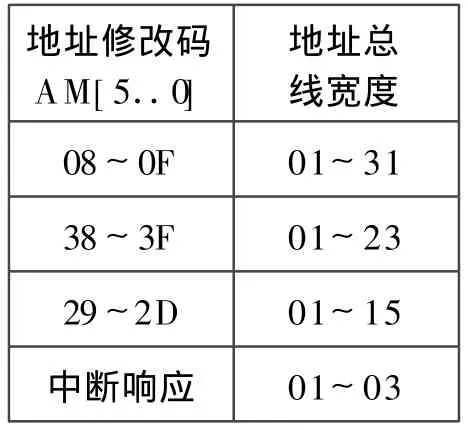

(1)地址信号线:A[31..1]、AM[5..0]、DS1、DS0、LWORD。AM0~AM5规定所用地址线的数目。地址线宽度选择真值表如表1所示。DS1、DS0数据选通信号由主设备驱动,用来选择数据传输的字节地址单元。

表1 地址线宽度选择真值表

(2)数据信号线:D[31..0]。由于VME总线的数据线宽度为32位,所以每4个字节单元组合可以在一个数据传输周期内被完全访问。主设备通过地址信号线A[31..2]指示哪4个字节单元组合被寻址,DS1、DS0、A1、LWORD 将指示该4个字节单元组合中的哪些字节被访问。

(3)控制信号线:AS、DS1、DS0、BERR、DTACK、WRITE。AS地址选通信号由主设备驱动,通知从设备地址稳定,可以启用。DTACK为从设备应答信号,在写周期从设备驱动DTACK为低表示它已经成功接收了写入的数据;在读周期从设备驱动DTACK为低表示它已经将数据放上了数据线。BRRR总线错误信号用于防止总线操作超时和死锁。WRITE读写信号由主设备驱动,指示数据传输方向。

优先级中断总线用于请求和响应中断的信号。监视中断请求线(IRQl~IRQ7),其中IRQ7优先权最高,IACK中断响应信号线。中断响应采用菊花链方式,IACKIN、IACKOUT为中断响应菊花链信号。中断响应信号IACK与第一槽的中断响应菊花链输入IACKIN连接在一起。当中断控制器拉低IACK信号时,将引起中断响应菊花链信号从第一槽逐级往下传递。没有发生中断请求槽的中断请求器将中断响应信号往下传递(菊花链驱动器驱动IACKOUT输出为低)。发生中断请求槽的中断请求器在收到中断响应信号后,将其捕获并停止往下传递(菊花链驱动器驱动IACKOUT的输出为高)。

2 FPGA接口程序的设计

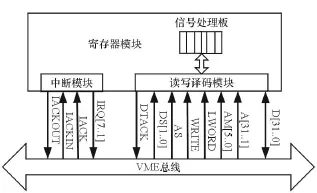

本设计采用Altera公司Stratix系列的FPGA器件EP1S10F672I7来实现VME总线接口电路的设计。该芯片具有10 570个逻辑单元,920 448位的随机存储器(RAM)存储空间和高性能I/O引脚。可见该FPGA的资源完全能够满足设计要求。FPGA中的VME总线接口逻辑主要有两大功能模块组成:一个是VME主机对寄存器读写访问模块,该模块的程序主要是寄存器读写信号和总线响应信号的设计;另一个是中断的请求响应模块,该模块主要完成中断信号的发送,并中断控制器在收到中断请求后,通过中断响应周期进行中断响应。VME总线接口逻辑框图如图2所示。

图2 VM E总线接口逻辑框图

VME从设备的寄存器单次读写通过地址译码、数据锁存来完成。要完成32位数据的写操作,首先设IACK为1指示非中断响应周期,WRITE信号设为0时指示写状态。等待上一从设备释放数据总线(即 DTACK、BERR信号线都为 1)时,主设备就可以将数据放到数据线上了,同时驱动DS0=0,DS1=0。从设备锁存数据,写入指定单元,并给出DTACK=0信号,指示数据已经写入成功。主设备检测到DTACK信号为0时,就释放数据线、地址线的控制权。程序采用VHDL语言状态机实现,整个过程分为6种状态:

状态1:驱动数据总线、地址总线,WRITE=0,IACK=1,LWORD=0,AM=0A。

状态2:驱动AS=0,使得数据总线上的数据有效。

状态3:驱动DS0=0,DS1=0。

状态4:等待回应信号DTACK,如果从设备应答,即DTACK=0,转入状态5,否则等待。

状态5:空等待1个周期。

状态6:驱动AS=1,DS0=1,DS1=1。

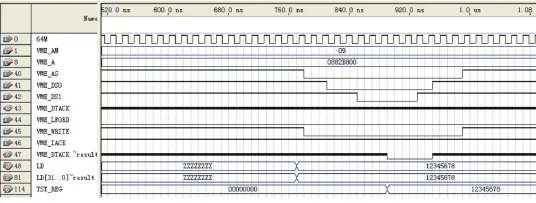

写寄存器仿真结果如图3所示。读取寄存器的值与写类似,只是根据读周期时序关系,各状态不再详细介绍。

图3 写寄存器仿真结果

中断请求模块发出中断请求后,中断控制器通过总线请求器获得数据传输总线使用权,拉低中断响应信号IACK,启动中断响应周期。中断功能使用VME中断IRQ3,中断时采用向量0×35进行应答。支持一个VME中断源对应多个局部中断源,局部中断源通过板内寄存器进行进一步判别。在中断响应周期中,监控输入信号IACKIN和A1~A3,等待VME主机中断管理模块发来的中断响应。当检测到IACKIN为低,说明中断控制器在进行中断响应。此时检测A1~A3上的值是否和中断发生器的中断请求级别一致,如果不一致可能中断发生器没有产生中断,或者当前响应的中断级别与中断发生器的中断请求级别不一致,那么就将驱动IACKOUT输出菊花链为低,如果一致就通知VME主机中断管理读取模块取走中断状态识别码,主机进入相应的中断服务程序(即完成了从模块VME总线中断的发送和响应过程)。根据VME总线中断响应时序关系,由程序采用状态机实现,分为 7个状态。

如果中断请求信号IRQ3有效,进入状态1。

状态1:驱动A[3∶1]=3(使中断请求级别与响应一致),IACK=0。

状态2:驱动AS=0,使得数据总线上的数据有效。

状态3:驱动DS0=0,DS1=0。

状态4:等待回应信号DTACK,如果从设备应答,即DTACK=0,转入状态 5,否则等待。

状态5:DTACK=0,表明从设备已将中断向量放在数据总线上。

状态6:空等待1个周期。

状态7:驱动DS0=1,DS1=1,AS=1。

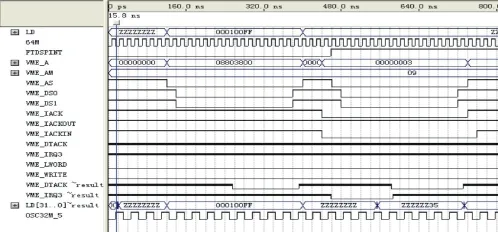

中断请求模块产生中断请求信号,请求级别为0x3,与中断响应级别一致,中断状态/识别字0x35在中断响应菊花链输入信号IACKIN有效后输出。中断响应菊花链信号没有继续往下传递,IACKOUT信号保持为高。仿真结果如图4所示。

图4 中断响应级别与请求级别一致情况的仿真结果

3 结束语

本文利用Altera公司的Stratix系列FPGA实现了一种VME总线接口电路,实际经验表明该设计可以实现高速的数据传输。这种设计具有兼容性强、并行性好、可靠性高和能高速传输的优点,为信号处理系统的设计提供了一种更好的方案选择。

[1]项碧波.使用FPGA实现VME总线接口.声学与电子工程[J],2000(3):40-44.

[2]刘显庆,刘仁普.微机总线规范——VESA PCI EISA VM E[M].北京:机械工业出版社,1995.

[3]崔葛瑾.基于FPGA的数字电路系统设计[M].西安:西安电子科技大学,2008.

[4]周平.利用PLD设计 VM E总线接口[J].计算机自动测量与控制,1996(2):47-49.