多种触发功能的可编程高速数据采集模块

2011-06-25田晓红张凯刘群

田晓红,张凯,刘群

(1.扬州大学 物理科学与技术学院,扬州 225002;2.扬州大学 生物科学与技术学院 )

田晓红(硕士研究生),研究方向为基于FPGA的高速数据采集;张凯(教授),研究方向为嵌入式系统;刘群(硕士研究生),研究方向为生物物理学。

引 言

在数据采集的过程中,为了不漏掉任何一个既定特征的信号,A/D转换器必须不断地采集数据。但是由于存储器容量的限制,不可能无限制地采集并存储数据[1-2]。如何使模块能自动检测、采集并存储有效数据呢?触发技术的引入可以解决这一问题。触发是为了有效地观测信号,当被测信号满足触发条件时,启动一次数据采集,使用户在屏幕上能观测到满足触发条件的波形[3-4]。

触发电路在以往的设计中,多采用电平比较器,其缺点是:采用的分立元件多,不利于模块移植和速度的提升,同时触发方式多样化配置也受到硬件限制,不具备智能化特点。本模块基于高速A/D转换器和FPGA,提出了一种全数字化的多种触发功能的高速数字采集设计方案。模块接口易于移植,采集频率高达50MHz,具有多种可编程触发功能,采用的触发窗技术[5]进一步保证了采样存储数据的正确性和有效性。

1 高速数据采集模块结构

高速数据采集模块由FPGA存储控制、传输电路和AD9057数据采集部分构成。其中FPGA为此次模块设计的重点。多种触发功能的高速数据采集模块结构框图如图1所示。采用Cyclone[6]系列EP1C6Q240C8型号的FPGA控制芯片,其Bank4I/O口与 AD9057相连,有源晶振提供了50MHz的时钟频率。

图1 多种触发功能的高速数据采集模块结构框图

此模块通过通信接口动态设置触发极性、触发模式、触发窗长度、触发点电平,触发极性可选上升沿触发rising_edge和下降沿触发falling_edge两种。触发模式可分为前触发pre_trigger、中间触发 mid_trigger、后触发post_trigger三种模式。触发窗长度设置为0~100的整数,触发点电平可设置为0~255的整数。

当连接通信接口的外部显示控制界面设置好触发极性、触发模式、触发窗长度、触发点电平时,开始启动采集命令,包装好的40位数据流将被发送到FPGA;FPGA接收到40位数据后,迅速分离成5个8位数据,即触发极性、触发模式、触发窗长度、触发点电平和采集启动信号,利用FIFO存储器先进先出的特性以及对AD9057的控制时序,配合触发信号存储A/D数据;当采样完成后,FIFO中的数据可以被发送到外部的显示控制界面直观地显示出来。

1.1 触发信号的产生

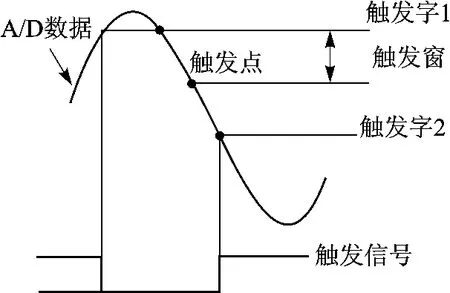

传感器探测和感知的模拟信号一般都带有一定干扰,如果仅凭一个触发点来决定触发的位置则很难控制,在本模块触发位置的设计中采用了三点触发窗技术,触发窗的设置可以有效地屏蔽模拟信号的抖动,使模块正常运行。

触发极性triggerpolar有上升沿触发rising_edge和下降沿触发falling_edge两种模式,在这两种触发极性下,触发信号上升沿表示模块开始存储A/D转换数据。模块设置了触发字1和触发字2,触发字1为触发点加上触发窗长度,如果结果小于255则触发字为两者相加结果,否则为255;触发字2为触发点减去触发窗长度,如果结果大于0则触发字为两者相减结果,否则为0。

图2是下降沿触发信号产生图。图中模块开始采样时,A/D转换数据与触发字1和触发字2不断地比较,当A/D数据大于触发字1时,触发信号输出为低电平;此后A/D数据与触发字2比较,当A/D数据小于触发字2,触发信号输出高电平。

图2 下降沿触发信号产生图

compare_standard1、compare_standard2分别是触发字1和触发字2。flag为标志变量,当A/D数据大于触发字1时,flag=1;当 A/D数据小于触发字2时,flag=0。具体实现的代码如下:

1.2 触发模式的选择

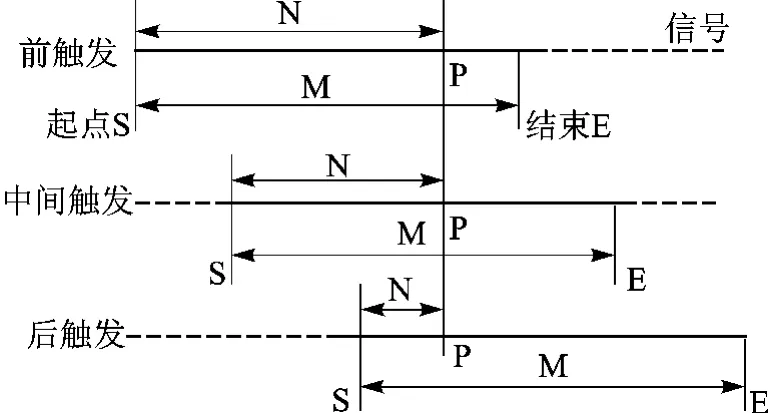

触发模式分为前触发、中间触发和后触发。触发模式的选择决定了触发的预触发深度N的不同。在一定的存储深度M下,捕捉的波形在触发点P附近被最大化地存储和显示。触发点前端波形的观察选择前触发模式,即预触发深度占存储深度的比例要大[7]。触发模式如图3所示。S代表起点,E代表结束点。触发点前后波形的观察选择中间触发模式,触发点后端波形的观察选择后触发模式。

图3 触发模式

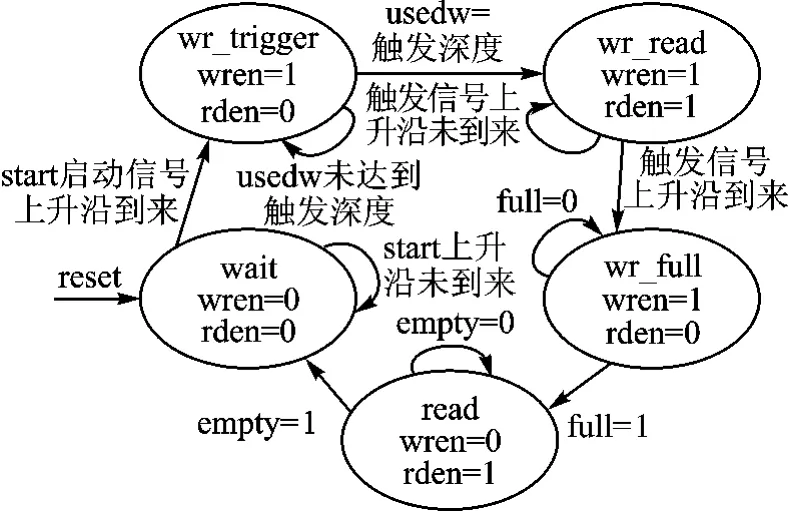

1.3 FIFO读写数据控制

FIFO存储器的读写[8]是用状态机来实现的。5个状态分别为 wait、wr_trigger、wr_read、wr_full、read。FIFO控制器流程如图4所示。模块开始进入wait状态等待启动信号start上升沿,如果start上升沿到来模块转到wr_trigger状态,否则将在wait状态一直等待;当模块进入wr_trigger状态时,FIFO开始写数据直到满足触发模式的预触发深度,此时的写时钟等于采样时钟;此后模块进入wr_read状态,FIFO开始一边读数据一边写数据,即一直保持FIFO中存储的数据是最新A/D转换数据,此时的读写时钟与采样时钟是同频的。直到触发信号上升沿的到来,否则FIFO存储器将一直读数据和写数据;当触发信号上升沿有效时,模块进入wr_full状态,FIFO存储器停止读数据,开始写数据,直到FIFO写满数据;当FIFO写满数据(full=1)以后,模块转到read状态,FIFO开始读数据并通过通信接口发送到显示控制界面进行直观的显示,直到FIFO为空empty=1,此时读时钟为显示时钟;FIFO读数据操作完毕,模块将一直停留在wait状态等待下一次采集启动信号的到来,如此反复执行。

图4 FIFO控制器流程

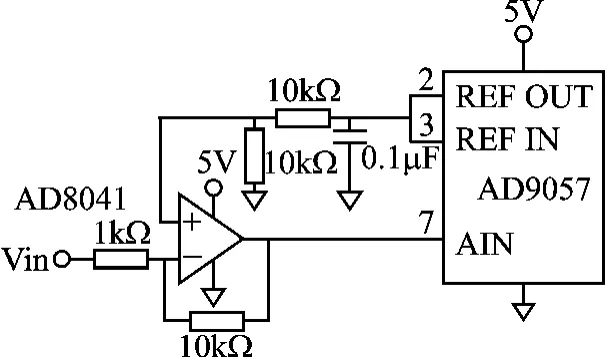

1.4 高速数据采集模块电路设计

AD9057是8位的模数转换器,可以达到60MHz的最大采样频率。设计中,模块采用50MHz的采样频率,AD9057带有2.5V的基准电压,可以对1V峰峰值输入模拟信号进行A/D转换[9]。通常采用高频、宽带运放对模拟信号进行缓冲,本设计中采用AD8041作为放大器,AD9057高速数据采集模块电路图电路图如图5所示。

图5 AD9057高速数据采集模块电路图

2 结 论

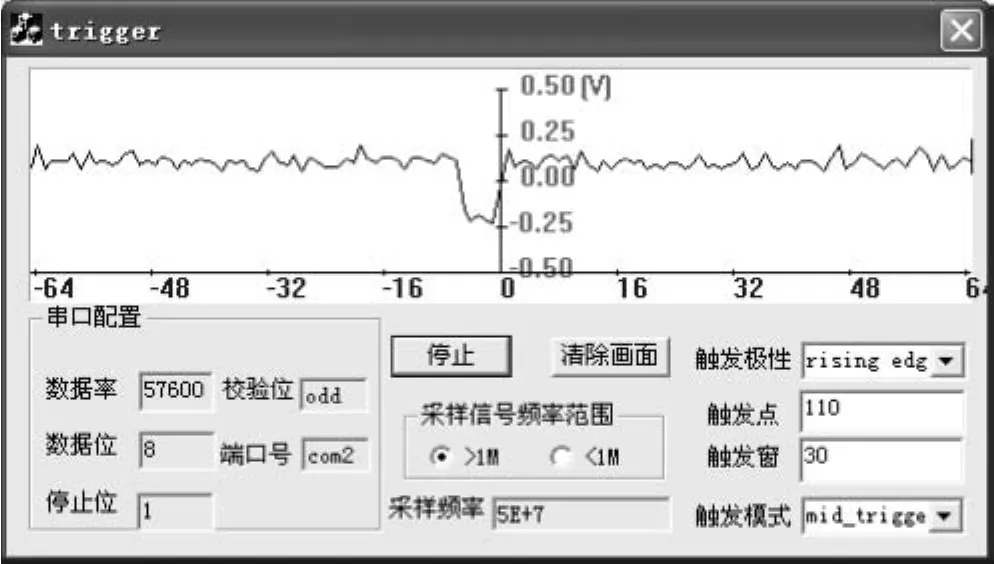

模块可以工作在50MHz的采样频率下,并且在模拟信号幅度偏小和有一定干扰的情况下也可以正常地工作。本次设计中采用了VC++6.0编写的显示控制界面进行模块验证[10]。图6是数据采集模块捕捉的频率为5MHz、300mVpp交替出现间隔为1ms的一个脉冲波形图。

其中,触发模式选用中间触发,触发极性为上升沿,采样频率为50MHz。由此可见,本模块的技术方案可行,具有灵活简洁的特点,可以应用在程控仪器和自适应信号采集与处理系统中。

图6 5MHz、300mVpp脉冲波形图

[1]倪浩然.各种触发模式在数据采集系统中的应用[J].电子产品世界,2005(21):53-55.

[2]翟立铭,张丕壮.随机脉冲信号数据采集触发电路设计[J].弹箭与制导学报,2008,28(5):252-254.

[3]宋永霞,张瑶,刘跃锋.波形仪器的触发与采集系统的设计[J].长春工业大学学报:自然科学版,2010(3):340-344.

[4]武云,乔纯捷,钟小鹏.数据采集系统中的触发设计[J].计算机测量与控制,2004,12(4):369-371.

[5]李毅,师奕兵,王厚军,等.数字存储示波器触发电路的数字化技术[J].仪器仪表学报,2004(3):385-387.

[6]Altera Corporation.Cyclone器件数据手册[EB/OL].[2011-06].http://www.altera.com.

[7]林敬涵.数据采集中的外部时钟及握手信号[J].电子产品世界,2005(5):123-124.

[8]王诚,吴继华,范丽珍,等.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2005:122-125.

[9]Analog Device Inc.AD9057 8-Bit 60MSPS A/D Converter[EB/OL].[2011-06].http://www.analog.com.

[10]李长林,高洁.Visual C++串口通信技术与典型实例[M].北京:清华大学出版社,2006:86-95.