高速宽带通信信号测向处理模块的设计与实现

2011-03-08巢捷频

巢捷频

(中国西南电子技术研究所,成都 610036)

1 引 言

电子侦察是现代战场侦察的一种重要手段,对辐射源目标的测向更是电子侦察的核心内容之一。随着各类通信装备的快速发展,电磁环境日趋复杂,对电子侦察装备的测向性能要求也越来越高。目前测向系统的带宽从十几兆赫量级往几十兆赫发展。同时,为了满足1000 hop/s的跳频信号处理的要求,测向速度要求也提高到百微秒量级。某测向系统中,由于平台的要求,结构非常紧凑,要求在有限的硬件资源条件下实现对通信信号60 MHz带宽内、分辨率在12.5 KHz的准实时快速测向,对测向的信号处理提出了很高的要求,信号处理模块的研制需要从高性能硬件设计、合理的流程设计、对算法进行优化几个方面来解决问题。

2 测向处理的性能需求

某侦察测向系统中,测向处理部分需要达到以下主要指标:

(1)瞬时带宽:60 MHz/2 MHz可选择;

(2)中频频率:140 MHz;

(3)频率分辨率:小于12.5 KHz;

(4)单信号测向处理时间:小于300μs;

(5)中频输入数量:5路;

(6)仪表测向精度:优于1°;

(7)具备跳频分析功能;

(8)尺寸:占用6U CPCI一个插槽。

从指标看,测向处理部分由1个处理模块实现,模块性能要求很高,首先需要处理的带宽(60 MHz)较大,其次需要很短的处理时间(300μs)且有限的硬件资源(1个CPCI插槽)。高带宽必然带来高的采样率,而高采样率引起的大数据量运算又与很短的处理时间和有限的硬件资源是相互矛盾的。此外,测向处理模块还兼顾跳频信号分选功能,测向处理能够利用的硬件资源受到进一步限制,使得测向模块的研制面临挑战。

3 侦察测向的总体设计

侦察测向从体制上来说有干涉仪测向、空间谱测向、比幅测向、波束合成测向等多种方法,其中干涉仪测向是一种传统的也是应用非常广泛的体制。干涉仪测向分为传统干涉仪和相关干涉仪两种体制。

传统干涉仪是建立在天线阵元获取入射波电场相位分布基础上的,当入射电波是平面波时,天线阵元相对位置就决定了各通道信号的相位分布。对各通道的相位进行测量,结合天线阵的几何构型,就可以推算出来波方向。但由于天线阵元间互耦、天线支架或天线阵载体等的影响、天线阵元本身的不一致性,往往会导致波阵面发生畸变,使入射波相位和幅度分布产生失真,最终造成测向结果误差偏大甚至错误。要降低或完全消除这些畸变和失真,工程上往往代价很大,很难做到。

相关干涉仪也是使用各天线阵元间的相位差来测向,与传统干涉仪相比区别在于计算出来的相位差并不直接用来推算来波方位,而是与预先准备好的相位差库进行相关比较。相位差库存储了不同频率、不同来波方向时各通道间的相位差数据。通过相关比较,找与相位差库中相关性最高的数据,该数据对应的来波方向就是测向结果。相关干涉仪体制具有高精度、高灵敏度和高抗扰度等突出优点,是工程上应用最广的一种测向体制[1]。

如图1如所示,某相关干涉仪测向系统由天线阵、开关、多通道接收机、标校源、测向处理机以及显控部分组成。

图1 测向系统功能框图Fig.1 Block diagram of direction finding system

测向处理模块的功能是对接收机输出的多路中频信号进行模数变换,得到数字信号后进行下变频、正交变化、滤波、预处理,再进行各通道的频谱计算,对结构进行信号检测,然后进行信号相位差的计算,通过与相位差库进行相关比较,最后得到信号来波方位。

测向处理模块在测向系统中需完成从模数变换到测向结果计算的所有功能,是影响整个系统测向处理速度的关键之处。

4 测向处理模块的具体实现

4.1 硬件设计

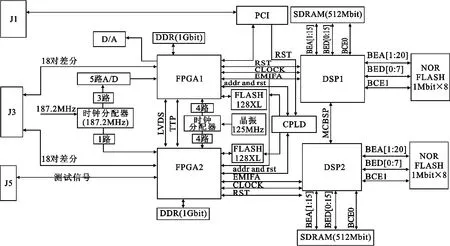

信号处理模块的硬件设计如图2和图3所示,处理模块由多路AD采集电路、FPGA/DSP及其外围电路、电源电路和接口电路等组成,运算与控制的核心由两块TI公司的TMS6414 DSP处理器、两块Xinlix公司的V5SX95T FPAG构成。TMS6414为定点处理DSP,运算能力可达8000 MIPS,具备丰富的接口,用作数据管理和基本的运算完全可以胜任。V5SX95T是目前应用广泛的主流信号处理FPGA,具备丰富的硬件乘加器和存储器资源,同时国内供货稳定,价格适中。

FPGA相对DSP处理能力要高得多,但算法编程实现相对困难。为了提高运算速度,硬件模块中测向部分使用一块DSP和两块FPGA来进行。

图2 电路原理框图Fig.2 Schematic diagram of circuit

图3 测向处理模块硬件图片Fig.3 Signal processing module

4.2 采样率的设计

输入的中频信号中心频率 f0为140MHz,带宽B为60 MHz或2 MHz。为降低后端处理运算量,适合采用欠采样的方法。中频输入有两种带宽,先对要求更高的60MHz带宽进行采样率设计。

根据带通采样定理[2]:

式中,fs为采样率,fh=f0+B/2=170 MHz,fl=f0-B/2=110 MHz。

根据公式计算,60 MHz带宽情况下,170 MHz≤fs≤220 MHz。在采样后的数据预处理中,需要对信号进行数字下变频及正交变换。下变频的基本原理如图4所示[3]。

图4 下变频器框图Fig.4 Block diagram of DDC

由图4可以看出,下变频的混频部分由DDS和两个乘法器组成的混频器以及后续的低通滤波器组成。此部分运算电路运行频率与采样率一致,属于整个处理流程运算速度要求最高的地方。如果选取下变频值 ω0=fs/4(即归一化频率 Ψ0=π/2),则DDS输出为[010-1]这样的序列,与输入信号相乘相当于简单符号变换、抽取和插零处理,可以大大减轻运算量,如图5所示。

图5 简化后的下变频器框图Fig.5 Block diagram of modified DDC

中频带宽有 2 MHz和 60 MHz两种,确定了60 MHz带宽下的大致采样率后,再对2MHz带宽的采样率进行设计。由于2 MHz带宽比60MHz低得多,故其采样率可以使用60MHz带宽采样率的整数分频,从而降低硬件设计难度,即(N为自然数)。这样工程中可以直接对采样率为 fs的AD采样数据进行N倍抽取,等效于的采样。同时,应用带通采样定理,对进行推算,最后得出的采样率 fs=187.2MHz,这样的采样频率设计可以同时满足60 MHz、2MHz的带通采样需求,且可以应用简化的下变频结构。

4.3 处理算法的实现

根据图1,测向处理算法需要完成各路信号的预处理、频谱计算、信号搜索、相位计算、相位差库相关运算等,为保证处理速度,除跳频信号分选外,主要的运算都在FPGA内进行。测向处理中,主要算法分为预处理部分、频率描述字(FDW)计算部分、方向计算部分,如图6所示。

图6 测向处理流程框图Fig.6 Flow chart of signal processing

AD采样后首先进行的是下变频的处理。4.2节阐述了简化的下变频中的混频器,减少了运算量。除此之外,下变频的另外一个组成部分低通滤波器,也可以通过优化设计减少运行量。在本应用中,选取了2倍抽取半带滤波器,这种滤波器的特点是通带和阻带宽度相同,且比一般的2倍抽取FIR滤波器减少一半的运算量,非常适合在这里使用。但应用中应注意其过渡带的宽度,需要保证信号在抽取后不能混迭。针对本方案,半带滤波器的频率响应仿真如图7所示。其中采样率为187.2 MHz,通带为30MHz,滤波器为24阶[4,5]。

图7 半带滤波器的频率响应Fig.7 Frequency response of half-band filter

完成预处理后,对数据分帧,进行后续运算,帧长度即为FFT运算点数,FFT使用流水线运算结构。FFT运算产生的频谱数据为复数,对其利用CORDIC算法进行反正切运算,就可以得到各频率分量对应的相位。结合利用幅度信息完成的信号检测结果,对每个信号都形成频率描述字(FDW)。FDW包含了信号频率值、时标和各通道的相位信息。FDW计算中,采样率为fs,FFT点数为N,频率分辨率为R。由频率分辨率公式

通过预处理后 fs=93.6 MHz,要达到12.5 kHz以上的分辨率精度,N=8192。

方位计算部分接收到FDW后,进行相位校正和与方位库内的相位差数据进行相关比较,最后得到来波方位。

为得到更高的处理速度,预处理和FDW计算部分采用了流水线形式,对信号进行全实时的运算,仅会由于流水线长度带来一定输入输出的时延。因为在侦察过程中信号数量的不确定性,方位计算部分没有采取完全的流水线结构,采用时分复用的方法,让各个信号的方位计算分时在同一电路里进行,这样的设计能够实现在现有资源情况下得到优化的性能。

5 测向速度分析

从上节所述的处理过程可知,整个流程分为预处理部分、FDW计算部分、方向计算部分。预处理部分为完全基于单个数据的实时运算,这样的运算会带来延迟,但非常小,可以忽略不计。FDW计算部分也是实时进行,但计算是基于数据帧的,从数据输入到输出,延迟包括数据组帧的实际和计算时间。最后的方位计算是基于单个数据运算,运算时间可以理解为输入输出延迟。

设测向处理总延迟时间为T,则:

式中,ts为信号组帧时间,tfft为频谱计算时间,ta为相位计算时间,tc为相关运算、求解方位的时间,n为过门限的信号个数。这里分析假定被侦察信号是一直存在的,不考虑信号突发造成信号漏检带来的额外时间开销。在FPGA中,相位计算与预处理部分类似,为基于单个数据的流水线形式,所以数据延迟ta很小,可忽略不计。

采样率187.2MHz的实信号进入预处理部分后,被2倍抽取,采样率变为93.6MHz。系统需要高于12.5 kHz的频谱分辨率,根据频谱分辨率计算公式(1),N取8192时,分辨率 R=11.4 kHz,满足要求。

按照93.6MHz的采样率和8192点的数据量计算,ts=87.5 μs。在型号为XC5VSX95T的FPGA 实现N点的流水线型FFT运算,tfft1=87.5 μs,tfft2=131 μs,其中 tfft1为FFT运算模块从开赛计算到输出第一个频谱计算结果所需的延迟,tfft2为所有数据输出所需延迟。方位计算时间 tc=2.5 μs。所以实际上,测向处理总延迟是一个变量,与信号个数和信号频率有关系。对于单信号来说,测向处理177.5 μs≤T≤265 μs。假设有200个频率点需要测向,则延迟675 μs≤T ≤762.5 μs。

6 结束语

按照上述方法,进行合理的采样率选择,对处理算法和流程进行优化,把主要运算放在FPGA中进行,可以解决测向处理模块在频率分辨率、处理速度和硬件资源之间的矛盾。目前,该模块已经完成研制,并通过了系统级的验收测试,实测频率分辨率、测向速度等关键指标都满足设计要求。其中频谱计算部分还设计了分辨率可变功能,可以在适当降低分辨率要求的情况下,进一步提高测向速度。

[1]王磊,束坤.干涉仪测向中相关处理算法的研究[J].舰船电子对抗,2010,33(7):87-90.W ANG Lei,SU Kun.R esearch into The Correlation Processing Algorithm in Interferometer Direction Finding[J].Shipboard Electronic Countermeasure,2010,33(7):87-90.(in Chinese)

[2]曹志刚,钱亚生.现代通信原理[M].北京:清华大学出版社,1992.CAO Zhi-gang,QIAN Ya-shen.Modern communication theory[M].Beijing:Tsinghua University Press,1992.(in Chinese)

[3]冯振伟,武小冬,游思理,等.基于FPGA的雷达数字接收机设计与实现[J].现代雷达,2009,31(11):72-76.FENG Zhen-wei,WU Xiao-dong,YOU Si-li,et al.Design and Implementation of a Digital Radar Receiver Based onFPGA[J].Modern Radar,2009,31(11):72-76.(in Chinese)

[4]王静,杨梅,刘涛.半带抽取有限冲激响应滤波器的应用设计及仿真[J].大连海事大学学报,2004,30(2):57-60.WANG Jing,YANG Mei,LIU Tao.Application design and simulation of HB decimation FIR filters[J].Journal of Dalian Maritime University,2004,30(2):57-60.(in Chinese)

[5]韩利竹,王华.MATLAB电子仿真与应用[M].北京:国防工业出版社,2003.HAN Li-zhu,WANG Hua.Simulation and application of MATLAB[M].Beijing:National Defense Industry Press,2003.(in Chinese)