基于FPGA的正弦信号发生器设计

2010-08-08姚益武袁秋晨王筱萌张琬菁

姚益武,袁秋晨,王筱萌,张琬菁,江 丹

(北京工业大学 电子信息与控制工程学院,北京100124)

直接数字频率合成技术(DDS)具有频率分辨率高,切换速度快,可输出相位连续、任意的波形信号,能够实现全数字自动化控制等优点,使其成为雷达、通信等信号源的首选。本文提出了一种基于DDS的正弦信号发生器,该发生器利用FPGA技术设计实现[1],操作简单,可实现最高频率为10 MHz的正弦信号输出,具有广泛的应用前景。

1 系统硬件设计

正弦信号发生器由FPGA模块、稳压电源、键盘显示单元、后向通路(高速D/A、低通滤波器、功放电路)几部分组成。系统结构如图1所示。

1.1 FPGA模块

随着VLSI技术的进步,目前FPGA的性能和硬件资源已经可以构成一个系统。设计中FPGA采用Cyclone的EP1C3T100C8器件,该芯片拥有2910LEs,约7 KB RAM,1个PLL资源。在FPGA外接晶振频率为32 MHz时,通过PLL可倍频得到80 MHz全局时钟,并且丰富的逻辑模块与存储资源为DDS算法的设计提供了良好的硬件基础。由于FPGA门级延时仅数纳秒,因此有利于信号的快速建立及转换。

图1 系统整体结构

1.2 后向通路

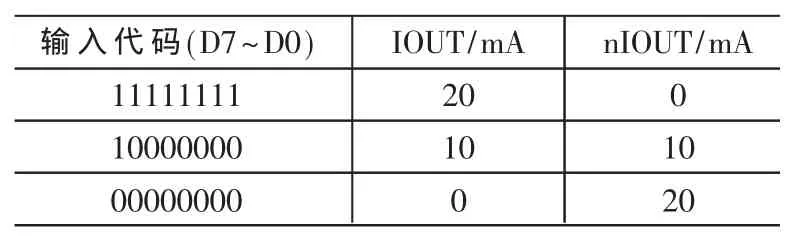

高速 D/A采用 TI的 8 bit、165 MS/s电流输出型数模转换器件DAC908,能满足FPGA输出数字信号更新速率的要求。DAC908输出电流与数字控制字间的关系见表1,DAC电路如图2所示。

表1 输出电流与代码关系

DAC908最大输出电流为20 mA,可在25 Ω负载电阻上产生0.5 V压降。同时DAC908的负载电阻作为基于高速运放OPA680的差分放大器[2]的并联电阻,放大器增益为2倍,因此输出信号幅度范围为±1 V。信号再经二阶巴特沃兹特性的LC低通滤波器平滑,由末级功放电路(采用 OPA656和 BUF634构成)输出,驱动 50 Ω负载。

2 系统软件设计

系统软件设计采用模块化思想,可移植性、可读性强。算法设计基于FPGA平台,包括键盘显示模块、时钟发生模块、DDS信号发生模块(PLL、DDS算法模块、ROM函数表)及DAC控制模块。FPGA系统设计如图3所示。

图3 FPGA系统设计

2.1 传统DDS算法设计

传统的DDS算法最先由 Tierney、Rader和Gold提出,如图4所示。它利用循环溢出的L位相位累加器产生正弦函数的相位变量。相位累加器每溢出一次,就代表正弦波形的一个周期。相位累加器输入的频率控制字Fin控制生成的正弦波形的频率,累加器的瞬时相位输出作为ROM表的地址。ROM表是存有正弦采样值的存储器。

图4 传统的DDS结构

基于传统 DDS算法,Fin=80 MHz时,为获得 10 MHz高频信号,则相位累加器字长为3,ROM表至少存有8个采样点;为获得10 Hz低频信号,相位累加器字长应满足 0.8×107=2L,ROM表的容量应为7 812 KB,远远超过了现有FPGA的存储资源,因此有必要改进传统算法。

2.2 改进的DDS算法

改进后的DDS结构[3]如图5所示,主要由循环相位累加器、地址信号发生器和ROM查找表组成。循环相位累加器的算法设计[4]如图6所示。

循环相位累加器的进位信号clkout作为地址发生器的计数时钟。而ROM表的设计,以降低存储容量为主。设计中ROM函数表中有8个采样数据,分别是正弦波在 0°、45°、90°、135°、180°、225°、270°、315°这 8 个相点处的值。根据奈式采样定理,8个样点的正弦波经过低通滤波器后可以完全还原。

图6 循环相位累加器的算法设计

3 系统验证与测试

FPGA整体工程遵循自顶向下的设计原则[5],经编译、综合分析、布局布线、时序分析后获得面向SRAM的配置文件,此文件经JTAG链下载到目标器件中,便可进行系统的在线调试。调试中借助QuartusII的Signal TapII逻辑分析器文件(采样时钟为全局时钟、采样深度为128 bit)对DDS算法进程作了时序的板级验证,如图7所示。而系统输出的正弦信号利用40 MHz带宽双踪模拟示波器进行观察,符合设计要求。

本文介绍了一种基于FPGA的DDS算法的正弦信号发生器,采用Altera的EP1C3T100C8及TI的DAC908高速数模转换器件实现,并进行了系统的在线板级验证与测试。输出信号频率范围为DC到10 MHz,信号频率分辨率为 0.1 Hz。

[1]刘进志,陈涤.基于 MPU/PLL和CPLD技术的数字正弦信号发生器的设计与分析[J].山东大学学报,2005,40(5):88-92.

[2]马场清太郎著.运算放大器应用电路设计[M].何希才,译.北京:科学出版社,2007.

[3]李晓芳,常春波,高文华.基于 FPGA的DDS算法的优化[J].仪器仪表学报,2006(z1):896-898.

[4]NOWLIN R W,SUNDARARAJAN R.A VHDL course for electronics engineering technology[D].1998(8):17-20.

[5]MAKHIJANI H,MEIER S.A high level design solution for FPGA′s.WESCON/94.Idea/Microelectronics.1994:596-603.