PLL频率合成器的杂散性能分析

2010-05-15陈叶民刘长明

陈叶民,刘长明

(国营第七一三厂设计所,江西 九江 332005)

0 引言

频率合成器作为无线通信设备的核心部件,其性能的好坏直接决定了无线系统的应用性能。PLL作为频率合成的一种手段,始终是高性能频率合成器设计的首选。PLL频率合成器的关键指标主要有相位噪声、杂散抑制和换频时间等。由于换频时间不具有普遍性,仅在频率捷变系统中有严格的要求,另外关于相位噪声性能分析的资料较多,因此本文仅对频谱杂散进行详细分析。

1 杂散性能分析

1.1 杂散概念

杂散是指和输出信号没有谐波关系的一些无用谱。在频谱上可能表现为若干对称边带,也可能表现为信号频率谱线旁存在的非谐波关系的离散单根谱线。这些谱线的幅度一般都高于噪声。通常用与载波频率成非谐波关系的离散频谱功率与载波功率之比来表征PLL的杂散性能,也就是常说的杂散抑制指标,以dBc表示。

1.2 杂散分析及工程解决方法

杂散其实也属于噪声的范畴,其传输特性与相位噪声的传输特性基本一致。从PLL的传输特性分析,任何一个环节都可能成为引入杂散的途径,这也使得因引入杂散的途径和起因的不一样导致杂散种类众多,对杂散的分析也更为复杂。因此,下面结合工程实际,对不同类型的杂散进行具体分析,并提出合理的改善手段。

1.2.1 鉴相泄漏引入的杂散

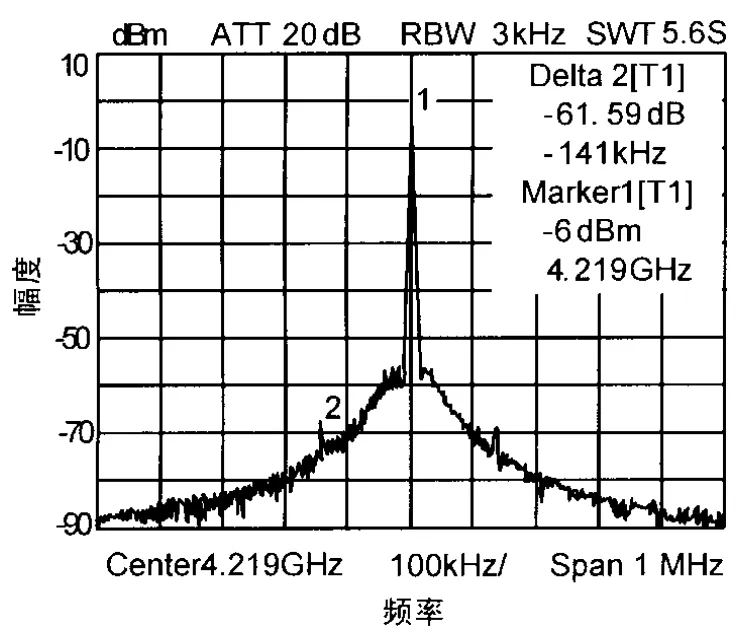

在PLL频率合成器的设计中,由鉴相泄漏引入的杂散是最常见的杂散,它出现在鉴相频率的整数倍上,如图1所示。

它主要是由于充电泵的电流泄漏效应以及电路失配所致,通常抑制该类杂散的手段主要通过环路滤波器的优化设计来实现。在工程上采用高阶环路滤波器能对该类杂散有着较好的抑制,一般的PLL采用三阶环路滤波器基本能够满足要求。

图1 由鉴相泄漏引入的杂散

1.2.2 小数分频引入的杂散

传统的整数频率合成器通常采用提高鉴相频率的方法来降低输出信号的相位噪声,这样便难以满足小频率步进的要求。小数分频技术的应用解决了这一突出的矛盾,但同时又导致严重的小数分频杂散。在工程上为了解决小数分频杂散问题,引入了Σ-Δ调制技术。Σ-Δ调制器的噪声成形技术可以有效地改变噪声的频谱特性,通过环路滤波抑制杂散,是单一锁相环路实现小步进、低相噪的最佳途径。目前CONEXANT公司的CX72301,ADI公司的ADF4153,MAXIM公司的MAX2150等,普遍都能将小数分频杂散抑制到一个可以接受的水平。

1.2.3 外部串扰引入的杂散

PLL频率合成器可能处于不同的电磁环境下工作,在屏蔽隔离不够的情况下,各种外部频率源都可能形成对PLL频率合成器的串扰,主要包括:显示器、各种电话、单元板中其他元件、闪烁灯光、交流电源和计算机等。一根长的信号走线可以等效成一根天线,从而引入干扰。因此,从工程上解决该类杂散的最好方法就是对敏感电路的屏蔽以及合理的PCB设计。

1.2.4 辅助PLL引入的杂散

该类杂散只产生于双PLL芯片的频率合成器中,在频谱上可以看到离载波频率的频偏为主PLL和辅助PLL(有时也可能是其高阶谐波)的输出频差。如果主PLL和辅助PLL的输出频率比较接近时,这种杂散最可能产生。其主要原因在于板上的寄生电容导致高频信号的线间串扰,以及芯片内部的相互串扰。PLL的充电泵电源对高频噪声极为敏感,在设计上一定要加强滤波隔离。同时辅助PLL不用的话,尽量在设计中关断其工作电源,以减少其对主PLL的干扰。

1.2.5 参考频率引入的杂散

该类杂散通常出现在偏离载波频率值为参考频率的整数倍的地方,其原因是参考频率的输入幅度太大,这将产生比较大的谐波分量,最终都可能调制在载波频率的两端。工程上的解决方法主要是对参考信号进行适当的滤波处理,以及保持一个合理的输入电平。

1.2.6 双PLL相互串扰引入的杂散

该类杂散通常出现在2个PLL电路靠的比较近且同时工作的场合。某些情况下,这类杂散将会比较大。其原因在于不合理的电源设计以及PCB布局设计。2个PLL的充电泵同时工作时,它们将在充电泵电源线上产生噪声,最终导致杂散的产生。因此,从工程上解决该类杂散的方法就是对不同PLL的充电泵电源进行隔离处理,并且尽可能地在充电泵电源线上放置更多的滤波电容,同时必须保证PCB设计的合理布局。在某些情况下,还可以考虑改变2个PLL的鉴相频率,以提高它们之间的频率差,这样一个较窄的环路滤波器也能对该类杂散起到较好的抑制。

1.2.7 环路滤波器元件引入的虚假杂散

该类杂散的特点是从频域上来看,并没有产生新的杂散,仅仅在频率切换后会导致鉴相泄露引入的杂散电平突然增大。当工作频率改变后,它需要很长时间才能减小到之前的状态,并稳定下来。这种现象在较低鉴相频率时更为普遍,其原因主要是环路滤波器的电容泄漏,有些理论也认为与环路滤波器电容的一些其他不理想效应有关,如介质吸收等。工程上的解决方法主要是使用高品质的电容。电容类型主要有钽电容、X7R、NPO等。另外,采用小数分频技术影响较小,主要是小数分频引入的杂散对充电泵泄漏和电容介质特性不敏感。

1.2.8 前置分频器计数错误引入的杂散

该类杂散通常出现在鉴相频率的1/2,也可能出现在1/3、2/3或其他一些小数倍数的鉴相频率上。该类杂散是由于前置分频器计数错误所引起的,通常导致前置分频器计数错误的原因包括高频输入脚的阻抗失配、PLL灵敏度的变化和VCO谐波等。即使PLL的灵敏度符合要求,阻抗失配也能使PLL灵敏度和VCO谐波发生变化;而且,PLL芯片的灵敏度还有一个上限范围。工程上的解决方法主要有:必须保证PLL芯片的输入信号电平在芯片标识特性的范围以内,同时尽可能在工作频率上实现阻抗匹配,并且使VCO的谐波抑制小于-20dBc,甚至更低,以减少前置分频器的计数错误。

1.2.9 前置分频器输出引入的杂散

该类杂散通常离载波频率比较远,偏移值为VCO输出频率除以分频比。在多数应用中,对该类杂散并不关心,因为它在带外。其原因主要是PLL芯片与VCO输出间隔离度不够,导致前置分频器输出信号反串到VCO输出端形成干扰。要解决此问题,必须提高PLL输入脚与VCO之间的隔离度,工程上的解决方法主要有:①在反馈路径上放一个有足够衰减量的衰减器,但衰减量的大小又受限于PLL的输入灵敏度;②在反馈路径上放一个放大器,以提高其反向隔离度;③使用一个对应工作频段的定向耦合器,但需要占用一定的PCB板空间。

1.2.10 开关电源引入的杂散

该类杂散离载波频率的偏移值为开关电源的工作频率。在大多数应用中,由于对开关电源的输出滤波隔离不够,直接应用到对噪声敏感的PLL电路中,开关电源噪声很容易调制到VCO的输出端,在工程上通过良好的滤波隔离基本能够解决此问题,如果在一些空间受限的场合无法做到很好的滤波隔离时,通常选用一个线性稳压器进行二次隔离,能够取得较好的抑制效果。

2 杂散问题的分析总结

总的来说,以上杂散并不是PLL杂散的全部,仅仅是在工程设计中碰到的相对常见的一些。要处理好PLL的各种杂散问题,必须在一些细节上加以注意,才有可能获得较为满意的杂散性能。具体表现在以下几个方面:

①合理的电源去耦设计。通常充电泵的电源易受到噪声的干扰。放置一个100pF,0.01μF,0.1μF能抑制较宽范围内的噪声。通常把较小的电容放置在离PLL芯片最近的地方,而把大电容放置在离PLL芯片稍远一点的地方,这样在小电容和大电容之间的走线将增加线上的电感,这种做法有助于抑制高频噪声。同时在电源线上增加一个小电阻有助于抑制低频噪声,这个电阻上的压降一般保持在0.1V左右,18Ω是一个典型值,但实际取值应根据工作电流而定;

②合理的PCB布局设计。必须确保充电泵的电源线和VCO的压控线远离噪声信号,尽量在芯片周围放置一些接地孔,以最小化信号的反馈路径,并且在顶层与地层之间放置一地层以减少相互间的串扰;

③合理的屏蔽设计。PLL电路属于噪声敏感电路,对其进行屏蔽设计有利于避免外部干扰影响PLL的输出信号质量,也避免了PLL输出信号对外部设备的干扰;

④合理的环路滤波器设计。通常环路滤波器阶数越高,带宽越窄对杂散的抑制效果越好。但如果杂散是来自VCO本身,那么更宽的环路带宽有助于改善杂散。当环路本身对某些带外杂散抑制效果不佳时,在环路滤波器的后端增加一辅助LC低通滤波器对杂散频率进行陷波,能起到很好的杂散抑制效果。

3 杂散性能优化的工程案例

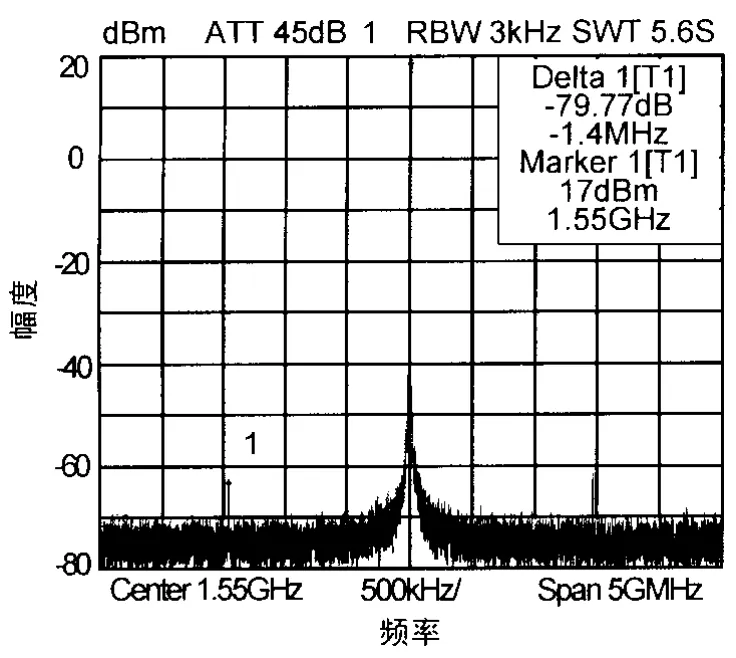

某型接收机PLL频率合成器的一本振输出频率为4219MHz,要求杂散电平小于-65dBc。在实际的工程设计中,PLL芯片选用的是ADF4106。由于是单环设计,电路较简单,用ADI公司的PLL仿真软件对该工程进行仿真,采用三阶无源低通滤波器,环路带宽设计为20kHz。

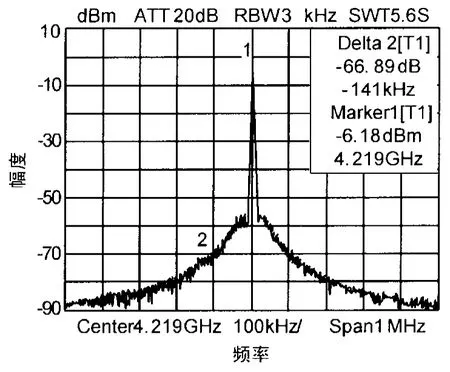

调试过程中,在RS公司FSU8频谱分析仪上输出的频谱如图2所示。从图上可以看到在载波频率的2端有对称的2个小峰,频偏在140kHz左右。通过分析知道,整机的电源单元全部采用开关电源设计,开关频率大概在140kHz左右,由于馈入PLL充电泵的电源隔离滤波不够,导致杂散的产生。虽然在电源滤波上采取了进一步的措施,但效果不明显。后来在充电泵的输入端增加了一个高性能线性稳压芯片,对输入电源进行二次稳压,达到了隔离开关噪声的效果。重新测试输出信号频谱,杂散消失,信号频谱如图3所示。

图2 有杂散的输出信号频谱图

图3 无杂散的输出信号频谱

4 结束语

通过上述对PLL频率合成器杂散的分析,使大家对PLL频率合成器杂散特性有了更为深刻的认识,也懂得了在PLL的工程设计中如何提高其性能及遇到上述问题该如何处理。工程上对于各种杂散电平大小的预测很难,必须对它们进行细致地分析,确认所属的杂散类型,并采取对应的解决方法,达到改善杂散性能的目的。应该说,本文对于正在进行PLL设计的射频工程师来说是一个很好的参考。

[1]李月.数字锁相倍频环的噪声分析及参数选择[J].长春邮电学院学报,1994,12(2):15-20.

[2]王福昌,鲁昆生.锁相技术[M].武汉:华中理工大学,1996:140-161.

[3]BEST R L.Phase Locked Loops:Design,Simulation and Applications[M].3rd Edition,USA:McGraw-Hill,1997.

[4]FOX ADRIAN.Ask the Applications Engineer about PLL Synthesizer[S].Analog Devices Application Note.

[5]ROHDE U L.Microwave and Wireless Synthsezers[M].New York:John Wiley&Sons,Inc,1997:79-135.