多晶硅薄膜晶体管的有效迁移率模型*

2010-03-16姚若河欧秀平

姚若河 欧秀平

(华南理工大学电子与信息学院,广东广州 510640)

近年来,多晶硅薄膜晶体管(P-Si TFT)在有源矩阵液晶显示(AMLCD)等领域得到了越来越广泛的应用[1].由于多晶硅薄膜是由许多小晶粒组成的,其晶粒间界中存在大量的悬挂键与缺陷态,这些陷阱会对P-Si TFT的性能产生很大影响[2-3].

在P-Si TFT中,沟道迁移率与晶粒间界陷阱态、表面散射效应等因素有关,因此用有效迁移率来表示.现有的P-Si TFT迁移率模型多为经验公式[4-5];文献[6]的有效迁移率模型考虑了沟道内晶粒间界的数目,并将晶粒与晶粒间界分开考虑,但忽略了高栅压所引起的迁移率退化效应,只适用于低栅压的线性区.

本研究基于P-Si TFT的物理过程,建立了一个适应于从小晶粒到大晶粒线性区的多晶硅薄膜晶体管有效迁移率模型.新模型考虑了高栅压所引起的迁移率退化效应,更符合P-Si TFT的实际工作情况.

1 理论模型

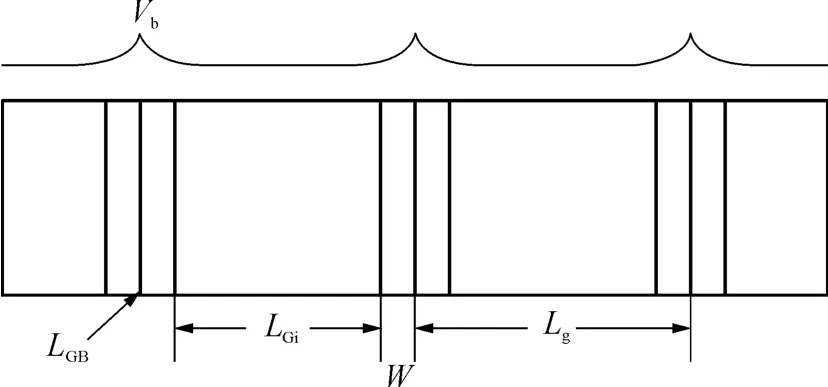

在实际的多晶硅薄膜中,晶粒间界可看作二维分布.对于小晶粒的P-Si TFT,可认为陷阱在整块薄膜内均匀分布;而大晶粒时,则需考虑沟道内晶粒间界的数目.本研究将晶粒与晶粒间界分开考虑,并假定沟道内的平均晶粒尺寸为 Lg.由于平行于电流方向的晶粒间界对开启区的电流影响较小,故只考虑沟道内与载流子运动方向垂直的晶粒间界[6].图 1为P-Si TFT沟道横截面图.图中,Vb为晶粒间界的垫垒高度,LGi为除去耗尽区宽度的晶粒尺寸,LGB为晶粒间界的厚度,W为沟道宽度.假设沟道长度方向内有n个晶粒与n个晶粒间界,与晶粒相比,晶粒间界的厚度LGB可以忽略(一般认为LGB=1~2nm).沟道电阻Rch可表示为

图1 P-Si TFT沟道横截面图Fig.1 Cross sectional view of the channel in P-Si TFT

式中:L为沟道长度;μeff0为低栅压下的有效迁移率; QinvG为晶粒内部的反型层电荷.

由于晶粒间界陷阱态的存在,晶粒间界两侧将形成耗尽区,产生势垒并阻碍载流子的运动.因此,沟道内存在载流子输运特性相异的两种区域[7-10].沟道电阻也可看成是晶粒内部电阻 RGi与晶粒间界(包括耗尽区)电阻RGB的串联:

式中:w为晶粒间界两侧耗尽层的宽度;QinvGB为晶粒间界(包括耗尽区)的反型层电荷;μGi为载流子在晶粒内部的平均迁移率;μGB为载流子在晶粒间界的平均迁移率.由图1可知:

式中:εSi为硅的介电常数;q为电子电量;Na为受主浓度[11].当栅压Vgs小于阈值电压 Vth时,陷入晶粒间界陷阱的电荷随着栅压的增大而增多,Vb逐渐增大并将达到一个极大值(此时晶粒间界陷阱态被全部填满);当栅压大于Vth后,Vb则随着Vgs的增大而减小.其表达式为

式中:Nt为晶粒间界陷阱态密度;tinv为反型层厚度,这里tinv=4nm;Cox为栅氧化层电容.

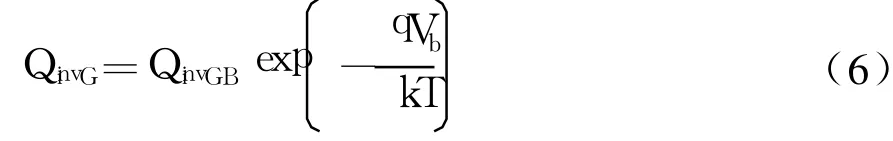

若载流子越过晶粒间界势垒的主要传输机制为电子的热发射,则 QinvG与 QinvGB之间存在如下关系[9]:

式中:k为波尔兹曼常数;T为绝对温度.

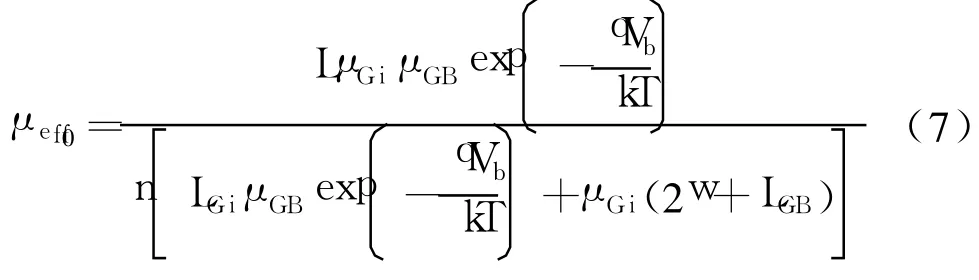

联立式(1)、(2)和(6),可得

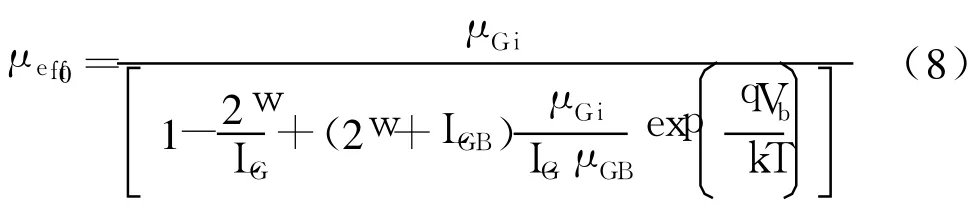

若平均晶粒尺寸远大于晶粒间界的厚度,则沟道内的平均晶粒间界数目式(7)又可变为

当栅压较高时,表面散射增强,还需考虑有效垂直电场引起的迁移率退化效应,此时的有效迁移率为

式中:Ecrit为引起迁移率退化的临界电场;而有效栅电场 Eeff可由反型层电荷以及体电荷求出[5].

2 结果与分析

应用Silvaco进行仿真的结果见图2-4.图2示出了低栅压时不同晶粒内部载流子迁移率μGi下的Lg-μeff曲线.从图2中可以看出,当Lg>0.4μm时,μGi对有效迁移率影响较大;而小晶粒(Lg<0.4μm)时则可认为有效迁移率不受 μGi变化的影响,主要由晶粒间界载流子迁移率 μGB控制.当晶粒尺寸非常小时,n变得很大,式(8)可表示为

但式(10)对大晶粒器件存在较大的误差.

图2 不同晶粒内部载流子迁移率下的Lg-μeff曲线Fig.2 Lg-μeff curves with different carriermobility in grains

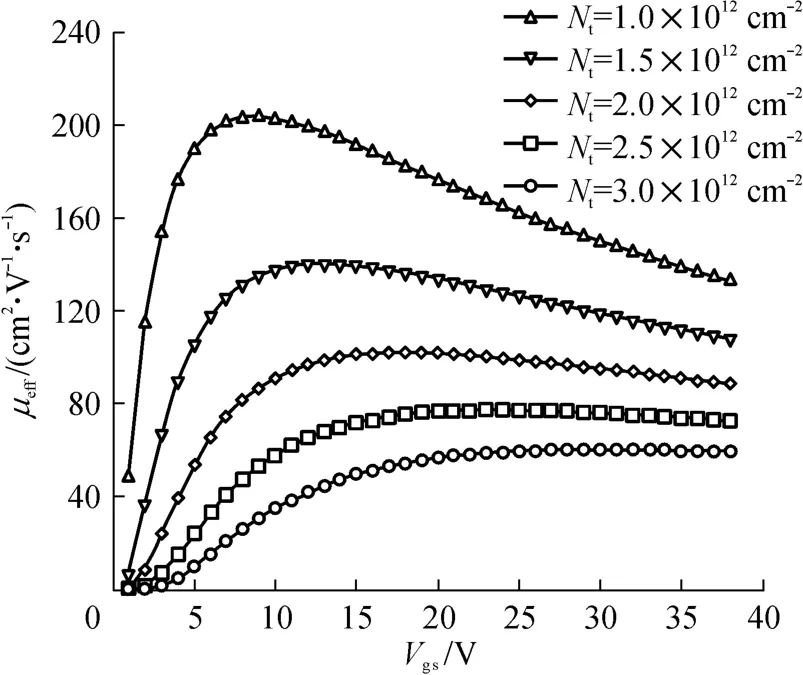

图3示出了不同晶粒间界陷阱态密度Nt下的Vgs-μeff曲线.从图3中可以看出,有效迁移率随着Nt的减小而增大,这是由晶粒间界势垒高度随着Nt的减小而降低所引起的.在高栅压时,由于表面散射增强导致有效迁移率下降,晶粒间界势垒效应开始减弱,该现象在Nt较低时更为明显.此外,当Nt较小时,最大有效迁移率所对应的栅压也较小,这是由于此时 Nt被完全填满所需的栅压变小,随后晶粒间界势垒随着栅压的增大而迅速降低所致.

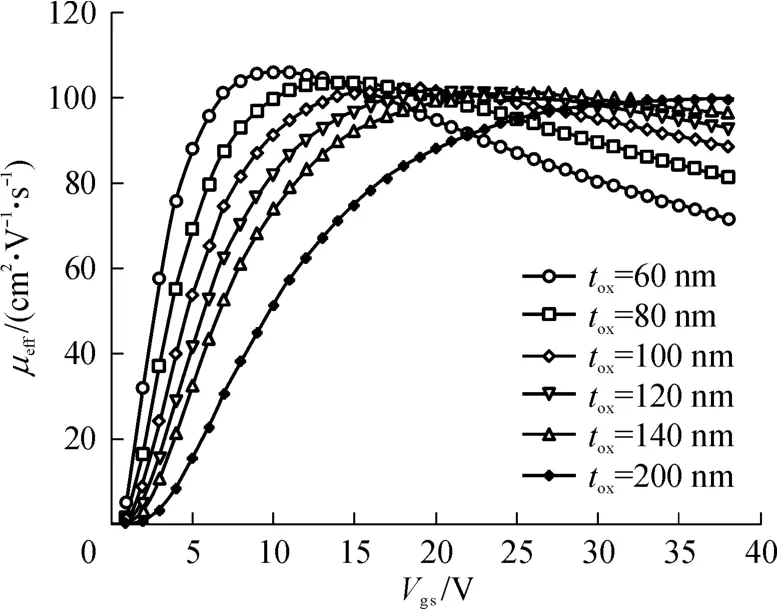

图4示出了不同栅氧化层厚度tox下的Vgs-μeff曲线.从图4中可以看出,当tox较小(tox<100nm)时,高栅压时所引起的有效迁移率退化现象更为明显.

图3 不同晶粒间界陷阱态密度下的Vgs-μeff曲线Fig.3 Vgs-μeff curves with different trap density in grain boundaries

图4 不同栅氧化层厚度下的Vgs-μeff曲线Fig.4 Vgs-μeff curveswith differentgate oxide thicknesses

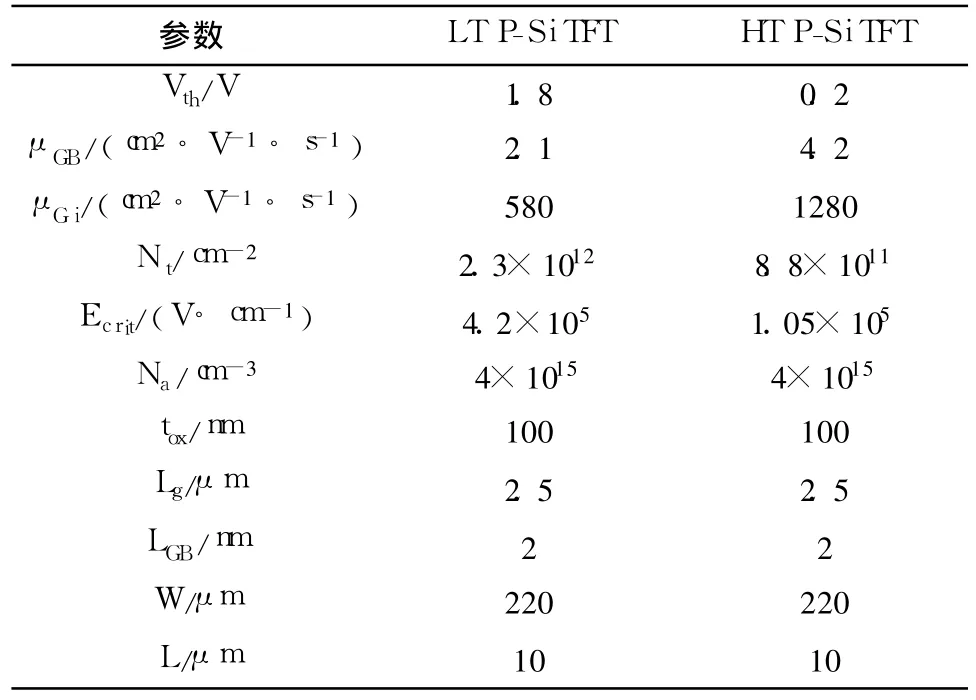

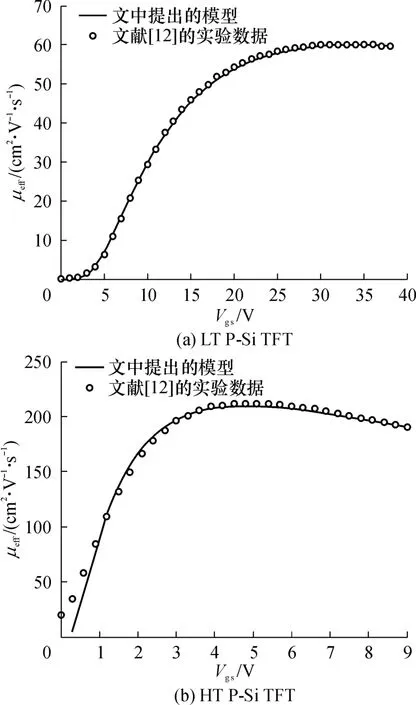

为验证模型的有效性,将仿真结果与文献[12]中N沟TFT器件的实验数据进行对比.仿真中所用的参数值见表1,其中与实验样品的参数相一致.从图 5中可见,由模型仿真得到的结果与文献[12]的实验结果有较好的一致性.其中高温结晶多晶硅(HTP-Si TFT)具有更高的有效迁移率,其参数中的晶粒间界陷阱态密度Nt较小,载流子在晶粒内部的平均迁移率 μGi以及在晶粒间界的平均迁移率μGB都要比低温结晶多晶硅(LT P-Si TFT)的大,这与实际情况相符,因为高温过程有助于减少晶粒间界陷阱态密度.在高栅压时,有效迁移率逐渐远离与栅压的线性关系,显示出有效垂直电场对迁移率退化的控制作用.

表1 仿真中所用的参数Table 1 Parameters used in simulation

图5 本研究提出的模型的仿真结果与文献[12]中的实验数据比较Fig.5 Comparison of simulated resu lts of themodel proposed in this study and the experimental data in reference[12]

3 结论

(1)本研究提出的P-Si TFT有效迁移率模型同时考虑了沟道内晶粒的数目、载流子在晶粒与晶粒间界处具有不同的输运特性和栅致迁移率降低效应,适合于从小晶粒到大晶粒线性区的P-Si TFT.

(2)对于小晶粒的P-Si TFT,特别是当Lg<0.4μm时,可认为其有效迁移率主要由晶粒间界所控制;降低晶粒间界陷阱态密度可大大提高有效迁移率;此外,栅压对有效迁移率的影响随栅氧化层厚度的减小而增加,高栅压时的有效迁移率退化效应更为明显.

[1] Gupta N,Tyagi B P.On the mobility,turn-on characteristics and activation energy of polycrystalline silicon thinfilm transistors[J].Thin Solid Films,2006,504(1/2): 59-63.

[2] Jagar S,Cheng C F,Zhang S,et al.A SPICE model for thin-film transistors fabricated on grain-enhanced polysilicon film[J].IEEE Transactions on Electron Devices, 2003,50(4):1103-1108.

[3] 姚若河,欧秀平.低掺杂多晶硅薄膜晶体管阈值电压的修正模型 [J].华南理工大学学报:自然科学版, 2010,38(1):14-17,43.

Yao Ruo-he,Ou Xiu-ping.Modified model of threshold voltage for thin-film transistorswith low-doped polysilicon [J].Journal of South China University of Technology: Natural Science Edition,2010,38(1):14-17,43.

[4] King T,Hack M G,Wu I.Effective density-of-states distributions for accurate modeling of polycrystalline-silicon thin-film transistors[J].Journal of Applied Physics, 1994,75(2):908-913.

[5] Lee SW.Universality ofmobility-gate field characteristics of electrons in the inversion charge layer and its application in MOSFET modeling[J].IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems,1989,8(7):724-730.

[6] Hatzopoulos A T,Tassis D H,Hastas N A,et al.On-state drain currentmodeling of large-grain poly-Si TFTs based on carrier transport through latitudinal and longitudinal grain boundaries[J].IEEE Transactions on Electron Devices,2005,52(8):1727-1733.

[7] Chern H N,Lee C L,Lei T F.An analyticalmodel for the above-threshold characteristics of polysilicon thin-film transistors[J].IEEE Transactions on Electron Devices, 1995,42(7):1240-1246.

[8] Yamauchi N,Hajjar J,Reif R.Polysilicon thin-film transistors with channel length and width comparable to or smaller than the grain size of the thin film[J].IEEE Transactions on Electron Devices,1991,38(1):55-60.

[9] Seto JYW.The electricalproperties of polycrystalline silicon films[J].Journalof Applied Physics,1975,46(12): 5247-5254.

[10] Yang G,Hur S,Han C.A physical-based analytical turnon model of polysilicon thin-film transistors for circuit simu lation[J].IEEE Transactions on Electron Devices, 1999,46(1):165-172.

[11] 欧秀平,姚若河,吴为敬.多晶硅薄膜晶体管中的晶粒间界电荷分享效应[J].微电子学,2008,38(6): 796-799.

Ou Xiu-ping,Yao Ruo-he,Wu Wei-jing.Charge sharing effects of grain boundary in polysilicon TFTs[J].Microelectronics,2008,38(6):796-799.

[12] Wang M,Wong M,Shi X,etal.Effective channelmobility of poly-Silicon thin film transistors[C]∥8th International Conference on Solid-State and Integrated Circuit Technology ICSICT'06.Piscataway:IEEE,2006:1395-1397.