集成电路产业技术发展趋势探讨

2024-01-11刘新阳LIUXinyang晁沛荫CHAOPeiyin李婷宇LITingyu

刘新阳/LIU Xinyang,晁沛荫/CHAO Peiyin,李婷宇/LI Tingyu

(深圳市中兴微电子技术有限公司,中国 深圳 518055)

1 宏观环境变化带来集成电路产业新形势

1.1 国际集成电路产业形势

集成电路是一个全球化的产业,参与全球化分工的各个国家、地区依托自身的优势,历经数十年市场竞争,形成了当前的产业格局。美、欧、日、韩、中国是集成电路产业链的主要参与方。其中,美、欧、日在集成电路上游领域较强。美国整体优势最大,例如美国在电子设计自动化(EDA)、IP、装备等领域均有明显优势,欧洲在IP、装备领域较强,而日本在材料、装备方面占优。2018年以来,中美科技竞争愈演愈烈,人工智能[1-5]、5G[6-9]等未来数字化、智能化产业升级的关键技术成为竞争焦点。作为算、存、传、管、智数字化基础设施的底层关键技术,集成电路更是受到前所未有的关注。围绕集成电路产业的竞争逐渐从企业层面扩展到产业链甚至国家/地区层面。集成电路全球产业链的发展越来越具有不确定性。

2021年2月,拜登政府执政之初就“美国供应链安全”签署了14017号行政命令。同年6月,白宫发布了一份《供应链百日评估》报告,指出美国供应链存在的一系列漏洞,并要求“建立有弹性的供应链,振兴美国制造业,促进广泛的增长”。在这一报告的指导下,美国随后密集出台相关法令法规,一方面通过政策、金融、市场等多种手段加强其在前沿技术上的研发和市场优势,推动芯片生产制造端重新回归美国国内,建设本土半导体制造产业链;另一方面在其政治盟友的基础上构建产业链盟友圈,在降低自生供应链风险的同时遏制战略对手获得半导体相关技术和装备。其中,影响力较大的法令法规包括:

· 2022年8月9日,美国通过《2022年芯片与科学法案》,向新兴技术提供超过2 000亿美元的投资,其中对美国本土芯片产业提供超过500亿美元补贴,涵盖半导体制造激励、商业研发和劳动力发展、教育基金、国防基金、创新基金等,同时要求任何接受补贴的公司10年内禁止在“特定国家”扩大和新建芯片产能。

· 2022年8月12日,美国商务部工业和安全局(BIS)出台新规定,限制全栅场效应晶体管(GAAFET)电子计算机辅助软件(EDA/ECAD)、宽禁带半导体材料氧化镓(Ga2O3)和金刚石、压力增益燃烧技术(PGC)等前沿技术出口。

· 2022年10月8日,BIS发布新规定,对出口管制条例(EAR)进行修订,增加对先进计算芯片、超级计算机等的出口限制,并增加外国直接产品FDP脚注的公司名单,以及对美国人/美国公司的出口合规约束。本次修订对中国企业获取高性能计算芯片、超级计算机、半导体制造设备进行了严格限制。

· 2023年9月22日,美国商务部国家标准与技术研究所(NIST)发布了《芯片法案》(“CHIPS Act”)护栏条款实施细则,将所有位于中国的企业(不限于国有企业)列为受关注外国实体。

· 2023年10月18日,BIS修改出口管制条款,进一步收紧对先进计算和先进工艺的限制,展现了保持甚至拉大中美技术差距的战略决心。

作为集成电路产业地图上的重要成员,欧洲和日本在今年也相继发布了相关法案。2023年1月24日,《欧洲芯片法案》草案和修正案通过,其配套的430亿欧元资金与美国芯片法案接近。该法案主要目标是解决集成电路供应短缺问题,加强欧洲的技术领先地位,并制定措施,与成员国和国际合作伙伴一起应对未来供应链中断的挑战。仅3天后,就传出美国已和荷兰、日本就限制向中国出口一些先进的芯片制造设备达成协议的消息。2023年7月23日,日本修订外汇与外贸法相关法令,对先进半导体制造所需的23个品类设备追加出口管制的措施开始正式生效。

可以看出,各国家/地区正在通过宏观政策强化自身在集成电路产业链上的力量,这使全球化发展趋势面临更大的不确定性。在此背景下,加强集成电路产业链自立自强是中国必由之路。

1.2 中国集成电路产业形势

在“十四五”产业数字化转型政策的推动下,各行各业对人工智能、5G等技术的需求持续扩大。作为数字化底座的基础技术,中国集成电路产业一方面受到市场需求的推动,对芯片特别是高端芯片的需求越来越大[10],另一方面由于全球化产业链的发展面临不确定性,供应端风险在增大。

习近平总书记说过,“关键核心技术是要不来、买不来、讨不来的”。面对宏观环境的不确定性,中国最具确定性的出路,就是打出政策、产业、技术和人才体系的全方位组合拳,对中国集成电路产业链形成有效推动力。

近年来,中国集成电路产业链在各个环节都取得长足进步:

· 装备和材料实现从无到有,对成熟制程形成整体供给支撑能力,部分产品进入先进制程供应体系;

· 制造工艺技术取得长足进步,逻辑电路、三维闪存、内存均有突破,并实现量产;

· 封装集成从中低端进入高端,传统封装规模世界第一,先进封装达到国际先进水平,技术种类覆盖90%;

· 设计能力得到大幅提升,处理器、现场可编程门阵列(FPGA)、通信系统级芯片(SoC)等高端芯片取得重大突破。

中国集成电路产业不断攻克技术难题,产业链持续向上突破,并向产业生态体系化建设发展。

中国的集成电路产业在快速发展,但也存在发展时间短、关键领域处于落后位置的问题。中国的服务器、通用处理器在技术和市场上均取得快速提升,而国际领先者Intel、NVIDIA等公司也不断推出新产品,他们不仅在先进工艺、先进封装领域持续发展,还在领域定制、异构计算、Chiplet[11]等架构创新的推动下获得性能领先。这使得中国同类产品与国际领先者的差距进一步拉大。中国迫切需要有竞争力的设计企业以实现产品竞争力的突破,需要在技术路线上坚持多元化发展,立足内循环,坚持双循环,积极吸收和应用外部的先进技术和能力,以便更好地支撑千行百业的数字化升级。

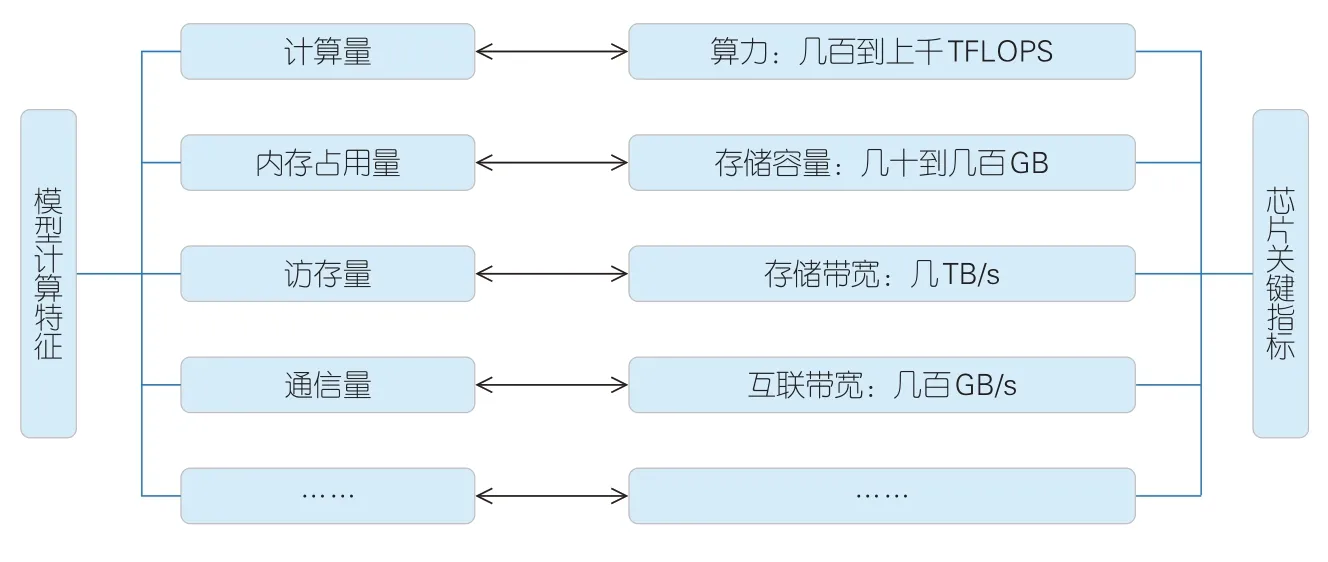

2 未来技术发展趋势

集成电路技术创新对国民经济的发展非常重要,是经济增长的触发器。信息社会数字化转型对数据获取、存储、处理需求的不断增加,导致算力需求指数持续上升。集成电路产业技术发展的目标,是单位面积、单位功耗或单位成本下计算密度、存储密度、连接密度的不断提高。自2018年起,大模型蓬勃发展[12]。2023年ChatGPT的火爆更是为该领域发展按下加速键,全球科技企业与研究院校等纷纷推出自己的大模型。由此带来的新一轮AI芯片对算力、存力、运力均提出更高需求,如图1所示。

图1 模型计算特征与芯片关键指标

在图2中蓝色为传统卷积神经网络(CNN)、循环神经网络(RNN)等传统模型训练算力,红色为大模型训练算力,灰色为摩尔定律下硬件算力。该图表明,随着大模型参数量规模增长至千亿甚至万亿量级,大模型训练算力每2年提升750倍,芯片算力随摩尔定律每2年提升2倍,大模型训练所需算力增速已远远超过摩尔定律带来的算力供应能力。随着未来越来越多的大模型应用落地,更大的算力需求将被释放。由于芯片算力=晶体管密度×芯片面积×利用率,因此算力的提升需要从3个方向同时发力,在先进工艺、先进封装、架构创新等方向多路径创新。

图2 模型训练计算量与摩尔定律随时间发展增速对比[13]

2.1 先进工艺

晶体管密度的提升来自于先进工艺的不断演进。数十年来,摩尔定律是集成电路技术发展的主旋律:每18~24个月实现性能、功耗、面积(PPA)性能翻倍,推动着集成电路从技术、产品到产业持续指数发展。尽管摩尔定律现在有所放缓,但是在光刻技术、材料、晶体管结构等的推动下仍在持续演进。如表1所示,工艺制程对PPA提升的贡献是其他路径所无法替代的。提高晶体管密度可以使产品集成度增加,从而可在单位面积上实现更多的功能;提升晶体管速度可以提高工作频率,进而提升产品性能;降低晶体管功耗有助于减少整机功耗,从而让产品变得更加节能。

▼表1 TSMC典型工艺节点对性能、功耗、面积(PPA)的提升

因此,国际领先的晶圆厂均在持续提高工艺水平。TSMC在晶圆代工制造领域仍处于绝对领先地位,主节点2年一代,保持持续领先优势。可以预见,装备技术和材料科学的持续进步,将为集成电路的持续微缩提供技术基础,推动先进工艺制程在未来数年里继续向1 nm节点发展。

2.2 先进封装

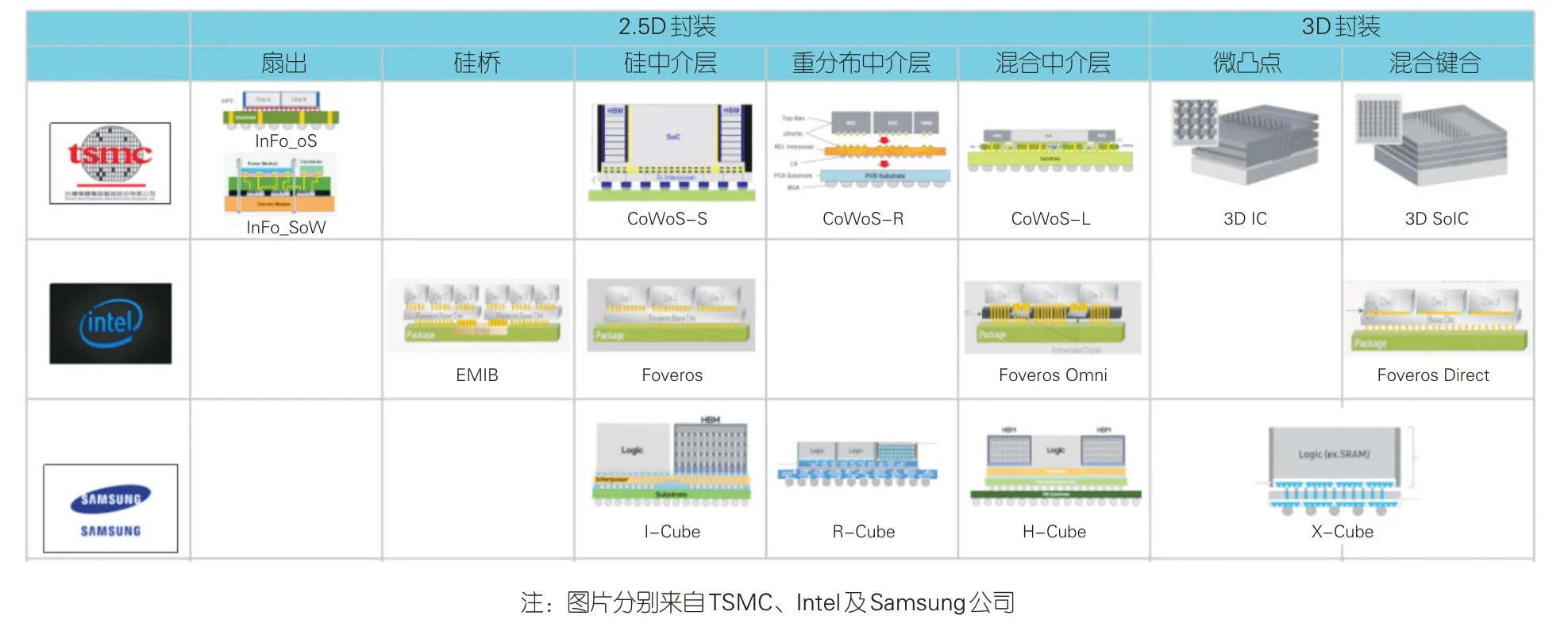

在半导体制程工艺提升放缓的趋势下,使用先进封装实现更高集成度,可以扩展芯片面积,从而提升算力,这成为业界越来越关注的技术方向。先进封装分为2.5D封装和3D封装。前者在二维平面扩展芯片面积,后者在三维竖直方向堆叠扩展芯片面积。硅通孔(TSV)技术是先进封装的基础技术之一。高密度高深宽比的TSV制备效果直接关系到集成技术的可靠性和良率等问题。

2.5D封装可以通过扇出、硅桥、硅中介层、重分布中介层、混合中介层等方式实现。目前业界主流且已实现量产的代表技术包括CoWoS(TSMC)、InFO_oS(TSMC)、EMIB(Intel)等,如图3所示。2.5D封装需求强劲,尺寸和结构持续发展,其中大尺寸是发展趋势。单芯片制造的最大面积上限由光刻机的光罩尺寸(reticle)决定。当前2.5D封装尺寸可达3.3×reticle面积(3 000 mm2左右),未来2年预计可达6×reticle面积(5 000 mm2左右)。与此同时,晶圆级封装也得到越来越多的应用。中国主流晶圆厂和封测厂等封装产业链各环节厂商纷纷建立2.5D先进封装能力。

图3 业界典型2.5D封装和3D封装技术

相比于2.5D封装,3D封装可以提供更高带宽、更低延迟、更低功耗、更强系统集成能力。与此同时,3D封装的封装复杂度、成本也更高。目前,3D封装在中央处理器/图形处理器、存储、光电合封芯片等领域都已经实现应用。同时,3D封装从微凸点向混合键合演进,通过更高的互连密度来大幅提升带宽。中国3D封装在存储领域已实现量产,逻辑芯片也已进入研发导入流程。

综上所述,先进封装有多种细分技术方向,在带宽、封装面积、信号完整性(SI)、电源完整性(PI)、热管理、工艺成熟度和成本等方面各有不同,需要结合相应产品需求选择匹配的封装方案。

2.3 架构创新

图灵奖获得者J.M.HENNESSY和D.A.PATTERSON认为,CPU等通用架构处理器的性能增加越来越缓慢,未来10年将是体系结构发展的黄金年代。特定领域架构(DSA)的设计可以进一步提升系统性能。Google、Tesla等基于特定应用设计他们的DSA芯片。即便当前占据绝对市场的Nvidia GPGPU芯片也越来越多地通过融合DSA设计来提升性能。通过分析需求场景和算法特点,DSA可以发现不能被当前架构较好支持的部分,并能用指令粗粒度固化该部分进行加速计算,从而提高系统性能。然而DSA架构在软件方面仍存在巨大挑战,例如指令的碎片化会导致软件适配的工作难以被下一代芯片复用。因此,架构设计的关键在于:根据算法趋势和应用场景,在硬件极致能效和通用可编程之间找到平衡。

除DSA外,另一种重要的架构创新是被称为“乐高式”架构的异构集成Chiplet架构技术,即小芯片或芯粒。Chiplet技术将多个可模块化芯片(主要形态为裸片“Die”)通过Die to Die互连技术集成在一个封装内,构成专用功能异构芯片。Chiplet能够从成本、性能、最小化资源需求和灵活搭配4个角度对现有架构进行优化,逐渐成为未来算力方案的基础架构。

Chiplet技术不是简单的“拆/分”“拼接”方案,要想最大化产品的性能、功耗、面积、成本竞争力,需要从先进封装、Die to Die互连技术、系统级协同设计3个维度协同创新。先进封装是实现2.5D封装的工艺基础。Die to Die互连技术是系统能够高效组合芯粒的关键技术。互连协议标准应具备兼容性与开放性。目前国际上BoW(开放计算项目提出的并行互联标准)、AIB(Intel提出的并行互联标准)等并行方案可能趋向收敛于UCIe(Intel提出的通用Chiplet并行互联标准),但仍存在超短距离SerDes串行互联标准(XSR)和极短距离SerDes串行互联标准(USR)等少量串行方案。与此同时,中国相关联盟也在建立标准,积极推动Chiplet生态建设。系统级协同设计是指如何根据目标,构建最优的芯粒分解-组合-集成方案,同时在整个前端-后端-封装的开发流程中进行适配。此外,Chiplet技术还面临着散热、供电、多物理场仿真、可测性等方面的挑战,需要芯片设计公司、OSAT、Foundry、EDA、IP、原始材料供应商等产业链各方共同培育完整的生态。

3 结束语

集成电路产业对人工智能、5G等产业升级起到关键基础作用,是全球科技竞争的焦点之一。各个国家/地区在通过政策手段加强自身竞争优势、降低供应链风险的同时,向竞争对手施加出口管制,给产业的供需端带来更大的不确定性。在外部宏观环境的变化和自身产业升级需求的推动下,中国致力于建设自立自强、可持续发展的集成电路产业,为各行业的产业数字化和全球竞争提供支撑。从技术发展趋势来看,中国既要在先进工艺、先进封装、架构创新等方面进行多路径创新,同时也要坚持多样化发展,进行独特的路径创新,建立可持续发展生态。

致谢

感谢深圳市中兴微电子技术有限公司王健、庞健和吴枫对本论文做出的贡献!