FPGA软件开发系统布局模块探讨

2023-12-09王硕苏峰黄赜

王硕,苏峰,黄赜

北京航天长征飞行器研究所,北京,100048

0 引言

在FPGA软件开发系统的应用中如果不采用国外的平台,将会严重影响FPGA用户的使用体验。因此有必要加强对FPGA软件开发系统布局模块的研究分析,从而在满足FPGA硬件需要的同时,提供配套的FPGA开发系统,为国内用户提供更好的使用体验,带动FPGA技术在国内实现更好的发展。

1 FPGA软件开发系统介绍

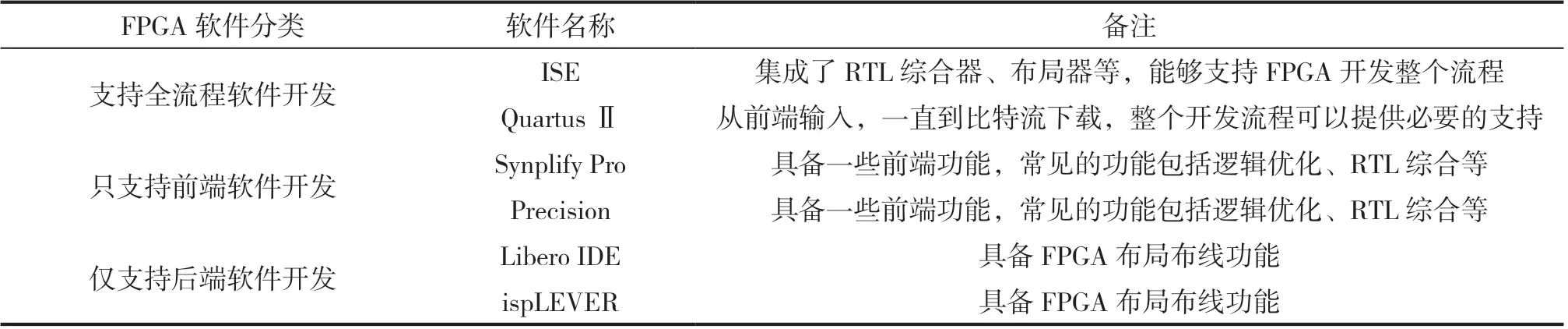

FPGA即现场可编程门阵列,本质上属于一种半定制电路。FPGA的存在,促使可编程更加灵活,可编程门电路容量也得到了有效提升。除此之外,FPGA的成本更低,运行功耗更小,且有着较高的密度,运行速度也会不断加快。在开发数字电路功能时,应用FPGA能够显著提升开发效率[1]。FPGA的基础编程资源一般包括三项内容:一是逻辑模块;二是输出/输入模块;三是可编程开关模块。其中前两种资源经常用到,这是实现开发功能的关键所在。在FPGA生成时,相关的厂商可以灵活地以各种开发需求为依据,设计生产出不同的FPGA产品。产品不同,具体的编程技术应用、产品结构以及配置的资源规模也会有所不同。在国内,FPGA软件开发平台仍有很大的探索发展空间。国外成熟的FPGA软件开发平台分类以及平台名称如表1所示。

表1 FPGA 软件开发平台分类以及平台名称

2 FPGA软件开发系统布局面临的挑战

2.1 挑战一

当前FPGA软件开发系统均采用了模块化设计方式。模块不同,实际输入和输出也有所差异。例如在ISE软件开发系统中,RTL通过综合生成NGC(包含逻辑设计数据和约束的网表)格式文件后,随后将其处理为NGD(本地通用数据库)格式文件,MAP读取NGD格式文件后,通过工艺映射与组装处理,最终输出了NCD格式文件。然后,再通过PAR读取NCD格式文件,完成整个布局布线过程。从中可知,上述仅仅一个基础流程便非常复杂,需要进行多种不同格式文件的转换处理,实际效率低下。为解决这一问题,本次在FPGA软件开发系统开发设计的过程中,主要目的是围绕不同模块,组建一套通用的数据模型。通过这一模型,不同模块之间可以交互,降低格式文件转化的复杂程度。所以,如何进行通用的数据模型设计,是本次FPGA软件开发系统布局挑战之一。

2.2 挑战二

通过上文叙述可知,FPGA产品不同,实际配置的资源规模、种类等有所差异。因此在设计通用模型时,需要围绕不同的基本单元,完成对应的建模。但上述整个过程占据的内存空间非常大[2]。在具体使用FPGA产品时,一般只会使用其中一种产品。所以在完成通用模型设计后,只需要存储在硬盘中。在开发时,需要某个对应的模型,可以通过硬盘进行内存读取,可以解决存储空间占用较大的问题。在实际建立器件模型的过程中,针对HWD2V/4V系列FPGA产品,还需要考虑其在结构、规模等方面存在的差异。在这一过程中,可以找到相同点,简化建模过程。针对不同点,则需要加强设计和测试。想要完成上述目标,需要建立器件模型文件规则,这也是本次研究的一项挑战。

2.3 挑战三

通过实现FPGA软件开发系统自动化布局,目的是提高用户FPGA产品的使用体验,让用户感到更加便捷。但对HWD2V/4V系列FPGA产品来说,实际容量非常大,因此需要解决大容量FPGA优化布局算法设计问题。在这一过程中,针对FPGA的一些特殊资源,由于数量较少,可以进行优先布局。针对其他一些资源,如何高效地完成布局优化,也是一项重大的挑战。

2.4 挑战四

对FPGA软件开发系统布局模块而言,在实际运行时,自身必须具有一定的可扩展性,才能满足后续的开发要求。在扩展要求方面,一是要实现命令可扩展,二是在不改变代码内容的条件下,满足添加器件封装的要求。所以对布局模块而言,如何实现可扩展性设计,是一项重大的挑战。

3 FPGA软件开发系统布局技术分析

3.1 XDL文件的分析与数据建模

在Xilinx中,XDL文件比较常见,该文件属于一份网表文件。文件语法如图1所示。从中可知,Design可以对设计信息进行详细描述。Design Name则是指设计的具体名称。Device代表的是FPGA具体的名称。Package则是指器件封装。Speed代表的是速度。Version指的是本地电路描述版本号。在cfg中,则包括了一些配置信息。配置信息不同,相应的名称、逻辑等也有所差异。对inst而言,则是在整个逻辑网表中,代表其中一个逻辑实体块。这种实体块在信息配置方面,整体的配置方法与design相同。Net代表的是一组实体之间的连接关系。Outpin与Inpin分别代表输出/输入管脚,二者均源自inst管脚。在一个XDL文件中,有且仅有一个design语句。除此之外,还包括一些inst与net语句。

图1 XDL 代码语法

在建立数据模型时,需要以XDL文件为核心,通过分析组装对象,完成实体类的建立。实体类不同,代表了不同阶段的网表。因此需要着重考虑处于不同阶段网表的需求信息。比如在组装阶段,需要表示具体的逻辑单元信息[3]。在布局阶段,需要表示布局后的物理位置信息。在获取实体类以及对应关系后,还需要通过设计分析,完成类图的建立。以数据模型为依据,布局模块能够与其他模块互相产生影响,彼此实现交互。对输入的XDL而言,可以代表多种内容,比如可以是网表文件,也可以是一种组装结果。在完成布局后,结合最终的布局结果,需要将其写入数据模型内部。如此一来,布线器可以发挥出应有的价值。

3.2 FPGA器件资源分析与数据建模

针对FPGA的布局模块分析,想要实现自动化布局以及布线操作,需要对FPGA器件资源进行分析,并完成模型构建。对HWD2V系列FPGA而言,本身的结构非常复杂,整体的结构是一种岛型结构。不仅如此,在资源分布方面,物理分布形式与其他分布形式也比较相似。在器件资源硬件配置方面,实际种类没有明显的差别。但在数量上,差异关系比较大。所以在实际设计的过程中,需要充分考虑资源类型。基于不同的类型,先完成资源模型的构建。在布局模块方面,可以应用XML文件存储器件资源信息。在应用过程中,针对XML文件,需要自定义一些具体的标签与语法规则。在定义XML标签时,可以以不同器件资源为依据,完成各种标签定义。随后再确定不同标签对应的语法规则。例如一个标签io用于表示一个管脚[4]。管脚需要对应管脚名称、类型等信息。上述这些信息实际存储位置并不确定。比如可以在io标签属性中进行存储,也可以存储在其子标签内部。如果实际的资源量比较大,需要采用循环结构完成建模,提升建模效率。

3.3 基于随机布局策略的布局方案优化

在布局方案优化方面,可以采用随机布局策略,完成初始方案的设计。随后,在模拟退火算法的帮助下,完成对初始方案的优化。具体的优化算法流程如下。

第一步,通过对布局方案S进行初始化,设置最优方案Sbest=S。

第二步,完成初始温度T设置。在不同温度下,需要结合实际,设置迭代次数SwapNum。除此之外,还需要做好初始交换范围的设置。

第三步,针对Sbest方案关键路径进行计算分析。然后以延时延矩阵为依据,获得初始花费代价C。

第四步,判断是否满足退出条件,如果没有满足条件,则执行第五步与第六步。

第五步,从Range入手,采用随机选择的方式,获取2个逻辑模块。在此基础上,需要交换模块的具体位置,最终可以获得布局方案Snew。最后,还需对相应的关键路径进行复杂的计算,可以获得花费代价Cnew。

第六步,根据以下公式作出判断:ΔC=Cnew-C(1),小于0,则设置C=Cnew,Sbest=Snew。

第七步,降低温度T,对Range进行更新,跳回第四步。

第八步,优化结束。

在温度更新与模块交换的过程中,二者的成功率与优化是否成功有着紧密的关系。一般情况下,优化越成功,温度下降速度越快。在计算关键路径时,需要应用到关键路径算法。该算法在图论中应用比较广泛。在对FPGA软件开发系统布局的过程中,设计关键路径所付出的代价大小,一般与布局方案质量水平高低有着非常密切的联系。通常而言,关键路径付出的实际代价越小,说明布局方案得到了更好的优化,最终的布局结果越好。在具体进行关键路径计算时,通过采用逻辑模块作为顶点,然后立足不同模块之间,选择相应的连线和信号流通方向。然后整合上述内容,使其作为有向图的边。在此基础上,结合实际信号的延迟时间大小,赋予有向图边具体的属性,以此来完成有向图的构建。与此同时,还应注意,需要再添加一个新顶点作为源点。那么源点到有向图之间,针对为0的顶点,实际付出的代价也是0。在这一过程中,还需要结合实际情况,添加一个新的顶点。该顶点可以成为有向图的汇点。那么顶点到汇点,最终的代价都是0。最终形成一个新的有向图[5]。在新的有向图上,可以计算出关键的路径。

3.4 布局模块扩展设计分析

在开发实践的过程中,开发人员在实际使用FPGA产品时,经常会习惯性应用TCL脚本。在该脚本的帮助下,在实际开发的过程中,可以实现批量处理。实际开发效率将会得到有效提升。因此在实际设计的过程中,开发语言应选择TCL语言。与此同时,为了进一步提升自身的运行处理效率,并更好地满足可扩展性需求,还需要在TCL开发语言的帮助下,完成底层处理工作。在开发设计的过程中,需要采用C++。不仅如此,开发人员可以结合自身实际需求,对基本TCL扩展命令进行灵活组合,从而形成新的自定义命令。

在底层中,通用模型开发在采用TCL语言时,能够在不改变C++代码的前提下,完成对器件模型的封装。在这一过程中,通过应用C++和TCL相互调用技术,可以进一步提升FPGA的布局模块的可扩展性。通过运用C++语言,调用TCL的过程并不复杂。只需要应用TCL Interpreter解析器,完成对TCL语句的解析处理,或者解析TCL的脚本文件即可。在这一过程中,可以采用Tcl_Eval函数公式,完成TCL命令的执行。随后,将会返回执行结果。该函数通过解析器完成解析处理,随后再完成相应脚本的执行。在执行后,如果返回的结果存在错误,将会把结果保存到tclInterp的result中。透过现象看本质,在TCL脚本中,还需要调用C++函数。采用该函数,可以生成TCL命令。在具体进行注册的过程中,第一步,需要先调用Tcl_CreateInterp函数,创建一个解析器interp。第二步,再调用Tcl_Init函数,对函数进行初始化处理。在此基础上,还需要输入参数interp。第三步,还需要调用Tcl_CreateCommand函数,完成C++函数到解析器中的注册。

4 结论

总而言之,针对FPGA软件开发系统布局模块设计开发是一项专业、系统、复杂的工作,在这一过程中,需要对相应的开发系统布局模块进行深入了解,认识到当前系统面临的问题,在提出解决方案的同时,提出一些有效的开发设计技术方法,提升FPGA软件开发系统布局模块设计开发效果。