面向下一代移动通信的高效率超宽带线性化技术的研究

2023-03-20黄健安郭新郝建豹胡光雄

黄健安 郭新 郝建豹 胡光雄

关键词:下一代移动通信;数字预失真;非线性滤波模型;现场可编程门阵列

0引言

当前移动通信网络中,数据量呈指数式增长。为适应这个趋势,移动通信网络迫切需要进一步优化和升级,向多载波及多输入多输出(multiple-input multiple-output,MIMO)技术演进。在网络建设中,射频功率放大器(简称“功放”)作为一个核心部件,对上述目标达成起着至关重要的作用。

下一代移动通信信号的宽频带和高峰均比给射频功率放大器提出了更高的要求。为了达到更高的效率,通常让功放在饱和区工作,但是在超宽带信号下,功放会有记忆效应且信号易失真,对通信质量产生影响。由于功放的效率和线性度是矛盾的,既要保证功放的效率,又要使其具有尽可能高的线性度,是研究人员要实现的复杂平衡。

目前,改善功放线性度较理想的方法是数字预失真(digital pre-distortion,DPD)技术,其具有性能良好、实现灵活、一致性好的特点。但是,数字预失真系统能够处理的信号带宽也受到反馈回路中模数转换器(analog to digital converter,ADC)的速率和位数限制,同时为了实时更新功放模型参数,需要消耗大量高速运算和存储资源,从而增大系统功耗。

针对目前超宽带高线性通信技术存在的问题,本研究提供一种带限函数自适应数字预失真算法,可克服ADC的速率和位数限制,并不需要增强数字信号处理器件的性能。

1系统硬件设计

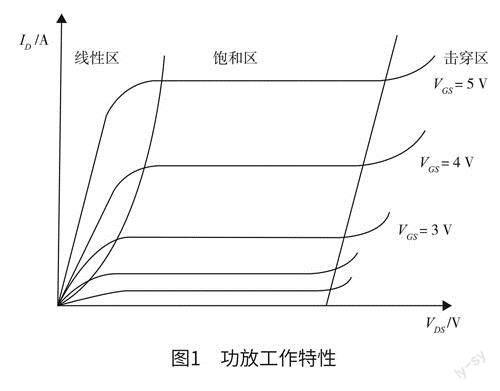

根据功放原理,目前主流的横向双扩散金属一氧化物一半导体场效应管(lateral double-diffusedMOSFET,LDMOS)功放的典型工作特性如图1所示。

当功放在线性区时,表现为很好的线性度,不过由于效率太低,会对无线通信基站造成巨大的能量浪费和设备发热问题。因此,功率回退的方法无法广泛应用于射频功放线性化场合。

预失真技术,即预先在射频功放模块前插入一个与射频功放工作特性相反的预失真单元,把理想的原信号经过预先处理变成设定的预失真信号,这时射频功放的输入就换成了新的预失真信号,从而提高了功放线性度。具体的实现原理图如图2所示。模拟预失真因为电路简单得到了广泛使用,然而模拟预失真通常只适用于双音信号或较窄带的信号,不适用于宽带的信号。

数字预失真是一种把射频功率放大器输出信号通过下变频混频电路变至基带后,与射频功放的输入信号产生射频功率放大器的逆模型。功放的逆模型参数存储在现场可编程门阵列(field-programmable gate array,FPGA)等芯片中。基于查找表(LUT)技术的数字预失真方法是数字信号处理(digital signal processrng,DSP)芯片依据输入信号的特性调用相应的表项参数进行数字预失真。数字预失真结构原理框图如图3所示,D/A为数字信号转换成模拟信号;A/D是模拟信号转换成数字信号。

本文设计一种基于数字预失真硬件平台的算法,其硬件原理框图如图4所示。

2系统软件设计

本文提出一种软件设计方法,在数字预失真硬件平台中运行,解决了大功率射频功放应用中遇到的效率和线性度矛盾问题。

在非线性系统分析中,幂级数是一种最基本的分析方法,适用于无记忆的弱非线性系统;谐波平衡法适用于大信号激励的强非线性系统。沃尔泰拉(Volterra)级数是一种更高级的分析方法,是泰勒(Taylor)级数的推广。它在系统识别领域有广泛的应用。

带宽的增加不仅会导致很强的记忆效应,而且对ADC的要求也会更高。如果输入信号带宽为80 MHz,5阶模型对应的带宽就是400 MHz,根据奈奎斯特(Nyquist)采样定理,则ADC采样速率需要达到800 MSa/s,这无疑对ADC提出了极高的要求。而带限函数自适应数字预失真(简称“带限数字预失真”)技术只需关注载带和邻带信号,即专注优化邻道的功率泄漏,而无须对整体频谱进行优化。这就大大降低了对ADC性能的需求。带限数字预失真结构如图5所示,DAC为数字模拟转换器;IQ信号又称同向正交信号,是连续信号在二维直角坐标系中的映射,通常用于基带信号的转换和重建,其中,I为同相(in-phase),Q為正交(quadrature),与I的相位相差90°; RF为射频信号(radio frequency)。

由于功放的输出信号在数学上可表达为由低到高的非线性分量相加,本文根据不同带宽的信号非线性分量设计阶数不同的非线性多项式。实验表明,模型的非线性阶数越接近对应频谱扩展的带宽,建模的精度就越接近理想值。Volterra级数带限函数模型如图6所示,x(n)为输入信号,y(n)为输出信号,y(n)为经过低通滤波器(FIR LPF)后的输出信号,n为Volterra级数的阶数,D1、D3、D5分别为Volterra级数模型中的一阶、三阶、五阶分量,h1、h3、h5分别为对应的一阶、三阶、五阶Volterra核系数。

本文通过将带限函数加入模型,既能使建模的精度满足数字预失真的需要,又能减少模型误差;不但使模型带宽得以控制,而且又能维持Volterra级数的阶数。

(1)在同等的性能条件下,与传统的带限记忆多项式模型相比,浮点运算数目和模型系数数目分别下降了约48%和28%。

(2)采用自适应的算法求解小数时延,可解决带限数字预失真系统中的环路延时问题,提高算法估计的精度,并且采用自适应的估算算法,具有一定的工程实现参考价值。

(3)实验结果表明,输出信号的相邻信道功率比(adjacent channel power ratio,ACPR)改善了27dBc,误差向量幅度(error vector magnitude.EVM)改善了3%,并且对超出模拟滤波器带宽外的频谱也有一定的线性化能力。

本文基于时域信号,设计模型控制滤波器的带宽来改变带限表达式的带宽。设计的模型较好地拟合了输入信号与输出信号间的工作特性,并具有很高的建模精度,而无须考虑功放输出带限信号的带宽。如式(1)所示,NMSE为归一化后的平均绝对误差,通过控制阶数不变,调整滤波器带宽,可将误差控制在0.682以内。

3结语与展望

本文提出的方案通过设置预失真模块,并优化时序分析处理算法,可避免设备过热的问题,并解决功放在超宽带范围内线性差的问题,提高了功放效率。

随着SG时代的到来,SG基站、智能移动终端及物联网(IoT)终端射频功率放大器应用已十分普遍,并且迎来高速发展。据统计,智能移动终端射频功放市场规模从2017年的50亿美元增长到2023年的70亿美元,高端长期演进技术(LTE)功率放大器市场的增长,使其在高频和超高频领域有更广阔的发展空间。本文提出的方案可直接应用在射频功率放大器的生产当中,将带来较大的经济效益。