国产JRAX1000型反熔丝FPGA应用演示系统设计

2022-03-17于跃隽扬曹靓赵桂林孙杰杰杨霄垒

于跃,隽扬,曹靓,赵桂林,孙杰杰,杨霄垒

(中科芯集成电路有限公司,江苏无锡,214072)

1 概述

中电五十八所研制的百万门级JRAX1000型反熔丝FPGA内部逻辑资源等效门数100万门,带三模冗余加固的寄存器单元有6048个,时钟资源包括4个硬线时钟(Hardwired)和4个布线时钟(Routed),此外芯片还内嵌了162Kbit带自刷新(EDAC)功能的RAM块[2]。JRAX1000型FPGA通过烧写相应位置的反熔丝,将程序代码固化在芯片内部,上电即运行,所以不需要额外的配置芯片引导启动。采用JRAX系列反熔丝FPGA在硬件设计上,较传统SRAM型FPGA简便。由于反熔丝FPGA属于一次可编程器件,不能多次编程,因而在代码设计和调试方面,较传统SRAM型FPGA复杂。为了解决代码设计和调试上的难度,通常采用SRAM型FPGA验证和调试代码的逻辑功能,在逻辑功能验证通过后,再将源代码移植到反熔丝FPGA开发坏境Libero软件中,进行时序约束和布局布线等操作,在时序满足要求后,再通过烧写器对程序进行固化。

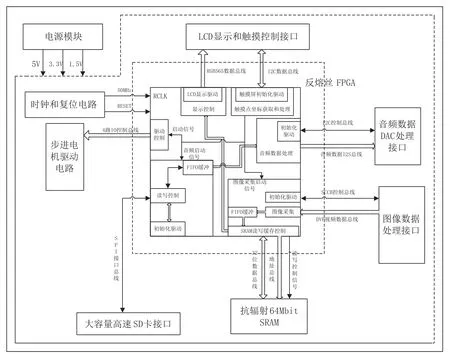

2 演示系统硬件设计

2.1 LCD显示和触摸控制电路

LCD显示和触摸控制电路作为整个系统的人机交互窗口,是两个独立功能的模块。其中触摸控制电路负责检测人体在显示屏上的触点坐标,根据触点在屏幕上不同区域的位置,系统开启和关闭相应的功能。LCD显示控制电路负责将系统运行的结果反馈在屏幕上,能直观的看出演示效果。

反熔丝FPGA通过IIC总线与触摸控制芯片FT5206进行通讯,完成对FT5206上电初始化,触点坐标实时监测[3]。反熔丝FPGA对接收到的坐标信息,进行坐标变换,并判断开启或关闭相应功能操作。在系统运行结果显示方面,反熔丝FPGA通过RGB565总线提供LCD液晶屏16位像素点数据,并按数据使能同步模式(DE MODE)、分辨率 1024×600,同步时钟50MHz的方式显示图像。

2.2 音频数据DAC处理电路

音频数据处理电路采用WM8731芯片内部集成的数模转换器DAC和运放,将存放在外部大容量SD卡内的无损音频数据,转换为采样率48KHz的音频模拟信号,并通过外部扬声器播放出来。在音频数据传输过程中,首先反熔丝FPGA通过SPI总线对外部SD卡初始化后,从SD卡中读入音频数据,并在FPGA内对数据进行处理,然后输出到WM8731中进行模数转换及信号放大[4]。其中FPGA通过IIS总线配置WM8731及数据传输,WM8731配置成从模式(Slave Mode)、过采样率256×fs(fs为音频数据采样率48KHz)、20位采样位数。因WM8731配置成从模式工作,所以WM8731的主时钟MCLK和位时钟BCLK都由反熔丝FPGA提供,这两个时钟频率计算如下:

图1 演示系统硬件组成框图

2.3 图像数据采集电路

图像数据采集电路采用OV5640图像传感器,其内部集成感光阵列、增益放大器、10位模数转换器ADC、图像处理单元和时序发生器[5]。感光阵列将光信号转换成模拟信号,经过增益放大后进入10位模数转换器;ADC转换器将模拟信号转换为数字信号,图像处理单元对数字信号进行压缩、格式化等处理,在时序发生器的作用下,将图像数据流按一定的时序输出。

在图像数据流传输过程中,首先反熔丝FPGA通过SCCB总线初始化OV5640图像传感器,设置传感器内部系统时钟、输出图像数据格式、水平和垂直像素点大小、曝光和白平衡等参数。在图像传感器初始化完成后,反熔丝FPGA通过DVP数字图像接口采集图像数据,并将采集到的数据存入外部64Mbit SRAM缓存。在一帧图像数据缓存完后,将SRAM中的数据送入LCD驱动模块并按相应时序进行显示。在固定时间循环反复进行图像数据采集、存储,显示等操作,完成图像数据的更新。

3 反熔丝FPGA程序设计

反熔丝FPGA是一次可编程器件,不像其他可重复编程的FPGA,程序一旦烧录进反熔丝FPGA中将无法修改,若程序运行不正确,则需要更换FPGA后重新固化程序,不利于代码的调试,而且增加了设计成本。所以在代码的前期设计和调试时,采用可反复擦写的FPGA验证代码的逻辑功能,在逻辑功能验证通过后,再将代码移植到反熔丝FPGA开发平台下。

反熔丝FPGA开发平台是基于 Libero9.2 IDE软 件,其 集 成Synplify编译综合、Modelsim仿真、时序约束、布局布线、以及生成反熔丝FPGA烧写文件,最后通过专用烧录器将程序文件固化到国产反熔丝FPGA中。反熔丝FPGA程序设计流程如下图2所示。

图2 反熔丝FPGA程序设计流程框图

3.1 逻辑代码设计与调试

在逻辑代码前期设计与调试中,采用Altera公司EP2C20F484C8型FPGA作为逻辑代码功能验证FPGA。此SRAM型FPGA不仅可以反复擦写,而且其内部自带有SignalTap逻辑分析仪工具,便于程序的修改和调试,极大的提高了代码开发的效率。

演示系统代码设计采用自顶向下的模块化分层设计,有利于功能划分和模块复用。具体的功能模块设计如下图3所示。

图3 逻辑代码模块框图

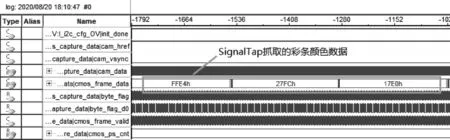

在代码设计完成后,利用Altera公司FPGA自带的SignalTap工具,对代码进行调试。在图3底部列出的图像数据捕获模块中,为了便于观测捕获的图像数据,先将图像传感器配置成输出彩条模式,期望的输出效果和采用SignalTap工具抓取到的图像数据如图4所示。由图4可以看出,SignalTap抓取的彩条数据与期望的输出数据一致,此模块采用SignalTap调试正常。利用此工具调试完成所有逻辑模块的功能。

图4 SignalTap抓取图像传感器输出彩条图像数据

3.2 Libero时序约束及优化

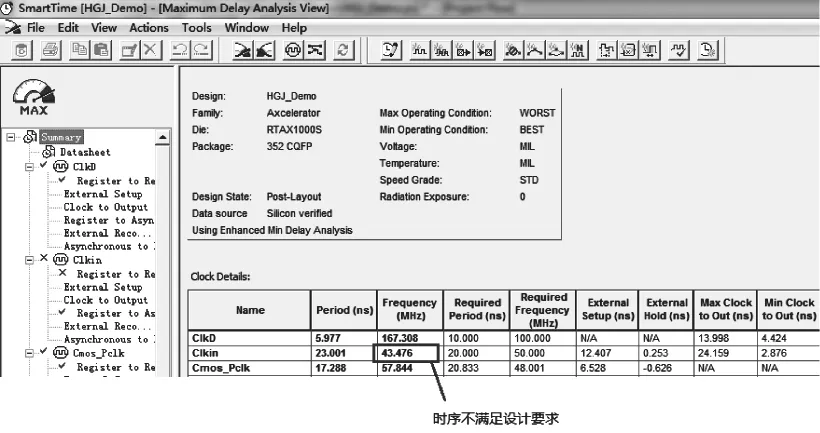

在代码逻辑功能验证通过后,将代码移植到Actel公司的Libero IDE编程环境下,继续完成反熔丝FPGA的后续设计工作。在Synplify综合工具中添加FDC约束文件,其主要约束了程序的外部时钟频率、生成时钟频率以及IO端口[6]最大、最小延迟等参数。通过编译综合、布局布线后,时序报告显示移植的源代码最高频率只能工作在43.476MHz,不满足系统时钟频率50MHz的设计要求,如下图5所示。而SRAM型FPGA在相同条件下,时序报告显示工作频率在66.42MHz,满足系统设计要求,如下图6所示。

图5 反熔丝型FPGA时序分析报告

图6 SRAM型FPGA时序分析报告

在Libero开发平台下,基于反熔丝FPGA的代码时钟频率不满足设计要求,根据FPGA内部时序分析的基本原理,影响时钟频率的主要原因是部分路径的延迟太长,造成FPGA内部寄存器的建立时间Tsu不满足要求。所以为了提高设计的主频,需要对建立时间Tsu违规的路径进行分析和优化。通过以下三种优化方法和思路,可以将此演示系统代码主频提高40%左右。

(1)通过Libero平台下的SmartTime时序分析工具,可以查看具体哪个路径的建立时间余量最小,如下图7所示。将此路径对应到源代码中分析,可以看出是代码中构建的一个128位宽的寄存器变量,影响了整体的性能。所以对此寄存器变量的位宽进行拆分,将一个128位宽的寄存器拆分成两个64位宽的寄存器变量。通过拆分的方法和思路,可以将此寄存器相关的路径都约束至时序收敛。

图7 部分违规路径时序分析报告

(2)采用拆分的方法处理后,时序报告中还存在某些路径建立时间Tsu不满足要求,这时需要采用第二种方法:在延迟较大的组合逻辑路径中插入寄存器,优化路径的建立保持时间,使时序满足设计要求,如下图8所示。

图8 插入寄存器优化时序路径

(3)此外Libero开发软件在布局布线过程中,也能设定布局布线的优化程度。布局布线优化程度越高,代码的主频速度越快,可是利用此方法提高速度效果有限。

除了对建立时间Tsu违规路径优化外,还需要查看保持时间Th是否存在违规路径。通常FPGA内部寄存器保持时间Th违规,主要是时钟偏斜造成的。在程序设计过程中,尽量使用全局时钟资源,避免使用分频产生的时钟作为寄存器的驱动时钟,这样可以有效减少时钟偏斜,在时序分析时不会产生保持时间违规路径。

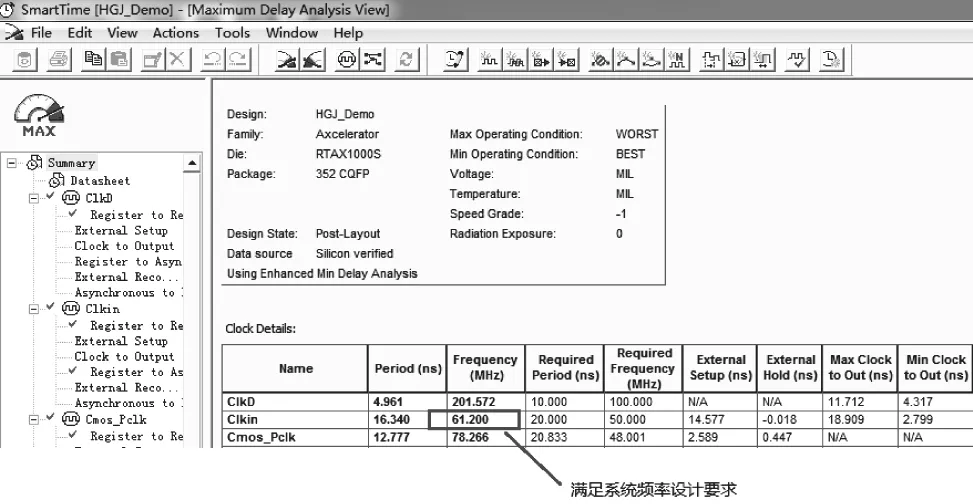

通过以上方法和思路,对时序约束不满足要求的路径逐一进行分析和优化,最终使程序稳定运行的频率提高到61.2MHz,满足50MHz的频率设计要求,如下图9所示。

图9 优化后的时序分析报告

4 结束语

本文利用国产百万门级反熔丝FPGA进行应用演示系统设计,从硬件功能划分、程序设计、代码优化等几方面展开介绍,并最终将代码固化到实际反熔丝FPGA中验证,演示系统实现了幻灯片、图像采集、音频播放、电机驱动等功能,符合预期的演示效果。通过对比常用SRAM型FPGA和反熔丝型FPGA在时序分析时的差异,点明在反熔丝FPGA开发流程中时序约束的重要性。为将来国产百万门级反熔丝FPGA的应用推广,提供一定的实际参考意义。