衬底浮空的新型绝缘体上硅基横向功率器件分析*

2021-08-05唐春萍段宝兴宋坤王彦东杨银堂

唐春萍 段宝兴† 宋坤 王彦东 杨银堂

1) (西安电子科技大学微电子学院, 宽禁带半导体材料与器件教育部重点实验室, 西安 710071)

2) (西安微电子技术研究所, 西安 710071)

针对有机半导体领域的发展要求, 报道了一种能够应用于有机半导体领域衬底浮空的新型SOI LDMOS(silicon on insulator lateral double-diffused metal oxide semiconductor)功率器件, 不同于传统无机半导体中SOI LDMOS功率器件, 该新型器件可以与绝缘的柔性衬底结合应用于有机半导体领域, 这给有机半导体领域的研究方向提供了新的可能. 本文通过仿真和流片实验共同验证了当常规SOI LDMOS缺失衬底电极后,比导通电阻和阈值电压均无明显变化, 但击穿电压会因为缺失衬底电极和纵向电场而下降15%左右. 针对该现象提出了一个具有表面衬底电极和漂移区氧化槽的新型SOI LDMOS功率器件, 该新型器件能够重新给衬底提供电极、优化横纵向电场、不明显改变比导通电阻与阈值电压, 同时将常规SOI LDMOS的击穿电压提高57.54%, 缓解了应用于有机半导体领域带来的不良影响. 为传统功率半导体应用于有机半导体领域的研究提供了可能, 对于有机半导体研究领域的拓展具有创新意义.

1 引 言

传统无机半导体中功率器件能够实现电能的变换与控制, 目前已经广泛地应用于国民经济的各个领域. 其中LDMOS(lateral double-diffused MOSFET, LDMOS)因能够作为功率放大器、开关电源等设备应用于家电、汽车电子、计算机和通讯等领域而在科学研究和工业领域都发展迅猛. 20世纪60年代SOI(silicon on insulator)技术被发现并应用于LDMOS领域. SOI LDMOS因具有低功耗、低漏电流、低寄生电容和高可靠性等独特优点而被广泛应用于功率集成电路和高压集成电路. 目前国内外关于能够提高LDMOS和SOI LDMOS性能的手段有很多, 其中包括降低表面电场(reduced surface field, RESURF)技术[1-3]、场板技术[4-7]、横向变掺杂[8-10]和横向变厚度[11]等表面终端技术, 也包括降低体内电场(reduced bulk field,REBULF)技术[12-14]、多浮空埋层技术[15]和图形化埋氧层技术[16,17]等体内终端技术, 还包括横向和纵向超结技术[18-21]等.

目前LDMOS的研究大多在无机半导体领域,但随着半导体行业的发展, 有机半导体的导电性能逐步被人们认识, 同时发现有机半导体有许多性能优于无机半导体, 因此有机半导体领域在半导体行业掀起了一个新的研究热潮[22-24]. 有机材料及其器件可以实现硅等无机半导体的信息显示、传感、存储、光电转换等功能. 并且就目前工业发展来看,有机电子材料及其器件的主要发展方向是在简单电路中取代无机晶体管, 从而在有机半导体领域中实现潜在的应用价值. 虽然有机半导体领域发展很快, 但目前仍然存在有机材料电学性能有限、有机集成电路发展缓慢等局限性问题. 无机材料能够弥补有机半导体材料电子性能较差的缺陷, 因此可将无机材料与有机材料结合. 同时, 由于目前有机半导体领域关于功率器件、集成电路等领域的研究还处于空白, 因此开始考虑能否将LDMOS作为开关电源、功率放大器等设备应用于有机半导体领域. 有机半导体功率器件使得有机集成电路的构成更完善、未来应用前景更加广阔, 同时还能实现传统无机半导体功率器件与有机半导体领域新的突破与创新.

由于有机半导体领域大多具有绝缘基底, 这使得其器件均位于柔性绝缘衬底上, 意味着常规LDMOS的衬底将浮空并且缺失衬底电极, 从而缺失RESURF技术, 因此性能将会变差. 本文通过仿真发现, LDMOS和SOI LDMOS在衬底浮空后, 击穿电压(breakdown voltage, BV)会分别下降23.3%和17.4%. 同时考虑有机半导体领域大多需要器件具有较薄的衬底厚度, 而SOI LDMOS中的埋氧层能够实现在较薄衬底厚度时承受较大耐压, 因此本文重点研究了衬底浮空的SOI LDMOS的性能变化, 并针对衬底浮空的现象, 提出了如图1(b)所示的具有P+多晶硅作表面衬底电极和漂移区氧化槽的新型SOI LDMOS结构.

图1 两种器件结构示意图 (a) 常规SOI LDMOS结构;(b) 带有表面衬底电极和漂移区氧化槽的新型SOI LDMOS结构Fig. 1. The schematic diagrams of the two devices are as follows: (a) Conventional SOI LDMOS structure; (b) a novel SOI LDMOS structure with a surface electrode and a drift oxidation groove.

2 器件结构

RESURF技术是器件发展的一个重要表面终端技术, 即将外延层厚度减薄使其完全被耗尽, 外延层能承受的反向偏压会提升. 外延层耗尽区中的电场与衬底耗尽区中的电场相互作用, 使得外延层中电场分布不再是单峰值的三角电场, 而是具有两个峰值的电场分布, 从而使得表面电场峰值降低.而衬底、外延层界面处的纵向PN结的电场峰值会先达到硅材料的临界电场强度, 使得击穿发生在体内, 从而实现表面电场的优化.

图1(a)为常规且具有RESURF技术的SOI LDMOS结构. 因为具有衬底电极和纵向电场, 所以能在减薄外延层厚度的同时实现RESURF技术, 但是当SOI LDMOS应用于有机半导体领域后衬底会浮空, 继而缺失衬底电极和纵向电场, 因此SOI LDMOS将无法实现RESURF技术, 其埋氧层也不再有优化电场的优势. 针对上述问题, 本文提出了如图1(b)所示的具有P+多晶硅作表面衬底电极和漂移区氧化槽的新型SOI LDMOS结构. 其中增加表面衬底电极会因为重新给衬底提供电极而改善衬底浮空的现象, 而在漂移区增加一个氧化槽, 使得实际漂移区长度增加, 能够在比导通电阻变化不大的情况下提升SOI LDMOS的击穿电压[25,26].

3 衬底浮空的SOI LDMOS仿真与实验结果

设计SOI LDMOS的性能指标为: 器件耐压60 V, 工作漏电流50 mA, 器件仿真结构参数如表1所列. SOI LDMOS用途主要是驱动10个LED灯, 设计的漂移区长度为4 μm, 栅宽为400 μm.主要工艺流程如下: 选取晶向为 〈 100〉 的P型SOI基衬底; 由于深N阱防止漏电, 从而进行深N阱注入, 并通过退火使得杂质扩散完成推阱; 因为高压P阱具有防止器件闩锁的作用, 所以通过注入获得高压P型辅助层和N型漂移区; 通过氧化刻蚀获得有源区和栅氧化层; 通过注入退火生成低压P阱和N阱, 其中低压P阱即为器件基区, 低压N阱作为缓冲区域, 缓解漏电极高峰电场来提高器件稳定性; 通过淀积获得多晶硅并进行多晶硅重掺杂形成栅电极; 通过N+和P+注入获得源极、漏极和基区接触; 通过光刻淀积获得器件的接触孔和金属布线; 通过金属淀积获得顶层技术; 最后进行金属电极表面钝化. 图2所示为实验后的8 in晶圆图片和其在电子显微镜下的截面图与俯视图.

表1 常规SOI LDMOS与衬底浮空SOI LDMOS器件仿真最优参数Table 1. Simulation optimal parameters of conventional SOI LDMOS/ substrate floating SOI LDMOS devices.

图2 实验结果 (a) 8 in晶片; 电子扫描显微镜下的SOI LDMOS结构截面图(b)和俯视图(c)Fig. 2. Experimental results: (a) 8-inch wafer; (b) sectional view and (c) vertical view of SOI LDMOS under an electron scanning microscope.

借助中国航空工业集团公司的下属公司江苏七维测试技术有限公司的测试平台完成了8 in晶圆测试. 测试设备为测试仪T862和探针台JC8001;测试温度为20—24 ℃; 测试湿度为(45% +/—10%)RH; 测试间洁净度为10000级. 下面通过仿真和流片实验及其测试来对比分析具有RESURF技术常规SOI LDMOS在衬底浮空前后的性能变化.

图3所示为常规且带有RESURF技术的SOI LDMOS在结构参数和掺杂浓度相同时, 衬底浮空前后的表面电场和纵向电场仿真结果对比图. 如图3(a)所示, 在衬底浮空前, 器件耐压主要取决于栅边缘的P阱和漂移区构成的PN结与漏端N+N结, 在表面电场图中表现为表面有两个峰值, 一个位于栅电极附近, 另一个位于漏极附近. 在衬底浮空后, 由于衬底对表面电场的调制作用变差, 表面耐压主要取决于P阱和漂移区构成的PN结, 因此表面电场分布逐渐不均匀, 趋于三角电场, 此时器件更容易击穿. 如图3(b)所示, 衬底浮空前SOI LDMOS因为埋氧层的调制, 能够在较薄衬底时实现较好耐压. 在衬底浮空后, 器件的纵向电场分布明显变差, 埋氧层的调制作用变差, 电场峰值会下降25%左右.

图3 衬底厚度Tsub = 15 μm, 漂移区长度LD = 4 μm的SOI LDMOS电场分布图 (a) 表面电场分布图; (b) 纵向电场分布图Fig. 3. Electric field distribution graph for SOI LDMOS with substrate thickness of 15 μm (Tsub = 15 μm) and drift zone length of 4 μm (LD = 4 μm): (a) Surface electric field distribution graph; (b) longitudinal electric field distribution graph.

图4 所示为常规且带有RESURF技术的SOI LDMOS在衬底浮空前后的输出和转移特性仿真与实验结果对比图. 仿真和实验均基于衬底厚度为15 μm和漂移区长度为4 μm的SOI LDMOS.由于使用ISE-TCAD进行器件仿真时, 虽然考虑了诸如载流子运输模型、载流子产生-复合模型、迁移率模型等影响因素, 还考虑了载流子散射、能带变窄等非理想因素, 但相较于实验所得器件而言,还是处于较理想状态. 工艺过程中, 由于仪器的精密程度、外延层生长环境和退火条件等因素的影响, 使得实验所得器件性能略差于仿真所得器件,因此实验所得器件的电流会低于仿真所得结果. 从图4还可以看出, 不论是仿真结果还是实验结果,衬底浮空对SOI LDMOS转移和输出特性的仿真与实验结果均无明显影响. 其中如图4(b)所示, 因为在衬底浮空后, 衬底对漂移区电场调制效果减弱, 表面电场变弱, 漂移区中载流子速度变慢, 器件准饱和漏电流变小. 因为器件栅极结构和基区掺杂没有变化, 所以在仿真和实验结果中器件的阈值电压均不变.

图4 衬底厚度Tsub = 15 μm, 漂移区长度LD = 4 μm的SOI LDMOS仿真和实验结果对比 (a) VGS = 5 V时的输出特性曲线; (b) VDS = 10 V时的转移特性曲线Fig. 4. Comparison of simulation and experimental results for SOI LDMOS with substrate thickness of 15 μm (Tsub =15 μm) and drift zone length of 4 μm (LD = 4 μm): (a) Output characteristic curve when VGS = 5 V; (b) transfer characteristic curve when VDS = 10 V.

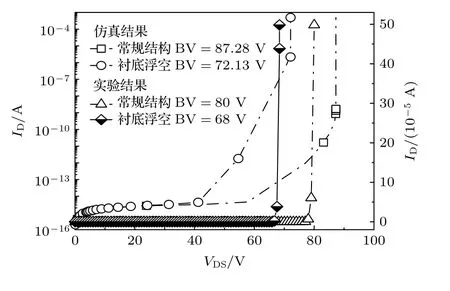

图5 所示为常规且带有RESURF技术的SOI LDMOS在衬底浮空前后的击穿特性仿真与实验结果对比图. 从图5中的仿真结果可以看出, 在相同结构参数和掺杂浓度时, 衬底浮空后, 击穿电压从87.28 V降低到72.13 V, 下降了17.4%. 导致常规SOI LDMOS衬底浮空后击穿电压降低的主要原因如图6所示, 图6为上述两种结构在掺杂浓度相同时仿真击穿电压与漂移区掺杂浓度的关系曲线. 由于衬底浮空后, 缺失衬底电极使得原器件失去RESURF技术, 电场分布也会变化, 从而使得器件最优击穿电压对应的漂移区浓度发生变化, 因此常规SOI LDMOS在衬底浮空后击穿电压会降低. 两种结构的比导通电阻(specific on-resistance,RON,sp)均为2.21 mΩ·cm2, 没有明显变化. 并且由于埋氧层的优势, 零栅压下器件的漏电流均为5 ×10—14A/μm左右. 从图5中实验结果可以看到, 在衬底浮空后, 器件的击穿电压从80 V下降到60 V.虽然性能有所下降, 但是仍然可以驱动10个LED灯.

图5 SOI LDMOS击穿特性的仿真和实验结果对比图Fig. 5. SOI LDMOS comparison of simulation and experimental results of breakdown characteristics.

图6 漂移区掺杂浓度对SOI LDMOS两种结构对应的击穿电压的影响Fig. 6. Effect of doping concentration in drift region on breakdown voltage of two SOI LDMOS structures.

4 新型SOI LDMOS的仿真与优化

常规且带有RESURF技术的SOI LDMOS在应用于有机半导体领域时会使其衬底浮空, 进而缺失衬底电极和RESURF技术, 性能就会有所降低. 因此提出具有P+多晶硅作表面衬底电极和漂移区氧化槽的新型SOI LDMOS结构. 该新型结构的工艺相较于第3节不同的部分如下: 1)在N阱和P阱工艺完成后, 在器件左端刻蚀一个窗口, 淀积多晶硅并进行P型重掺杂, 从而获得表面衬底电极; 2)器件表面生长钝化层, 在N阱表面刻蚀出一个窗口, 通过干氧工艺生长氧化槽. 该新型结构可以通过转印工艺与柔性衬底结合, 作为开关电源、功率放大器等设备应用于有机集成电路,从而实现其在研究领域、应用前景等方面的拓展.下面将针对常规SOI LDMOS、衬底浮空的SOI LDMOS、增加表面衬底电极和衬底浮空的SOI LDMOS以及同时具有P+多晶硅作表面衬底电极和漂移区氧化槽的SOI LDMOS这几种器件的性能进行分析比较.

图7所示为四种器件的表面电场和纵向电场的对比图. 如图7(a)所示, 在衬底浮空后, 漂移区不能完全耗尽, 表面电场分布趋于三角电场. 加上表面衬底电极后, 曲线和有衬底浮空前重合, 器件性能得到优化. 再在漂移区加上氧化槽以后, 漂移区有效长度增加, 器件的表面拓展到槽表面, 能够达到对表面电场的优化效果. 器件的表面电场增加一个新的电场峰, 达到优化表面电场的目的. 如图7(b)所示, 常规SOI LDMOS因为埋氧层的调制, 能够在较薄衬底时实现较好耐压. 当衬底浮空后, 器件的纵向电场分布明显变差, 经过表面衬底电极和漂移区氧化槽的横纵向电场的同时优化, 器件的纵向电场耐压提升.

图7 几种SOI LDMOS的电场分布图 (a) 表面电场分布图; (b) 纵向电场分布图Fig. 7. Electric field distribution of several SOI LDMOS:(a) Surface electric field distribution; (b) longitudinal electric field distribution diagram.

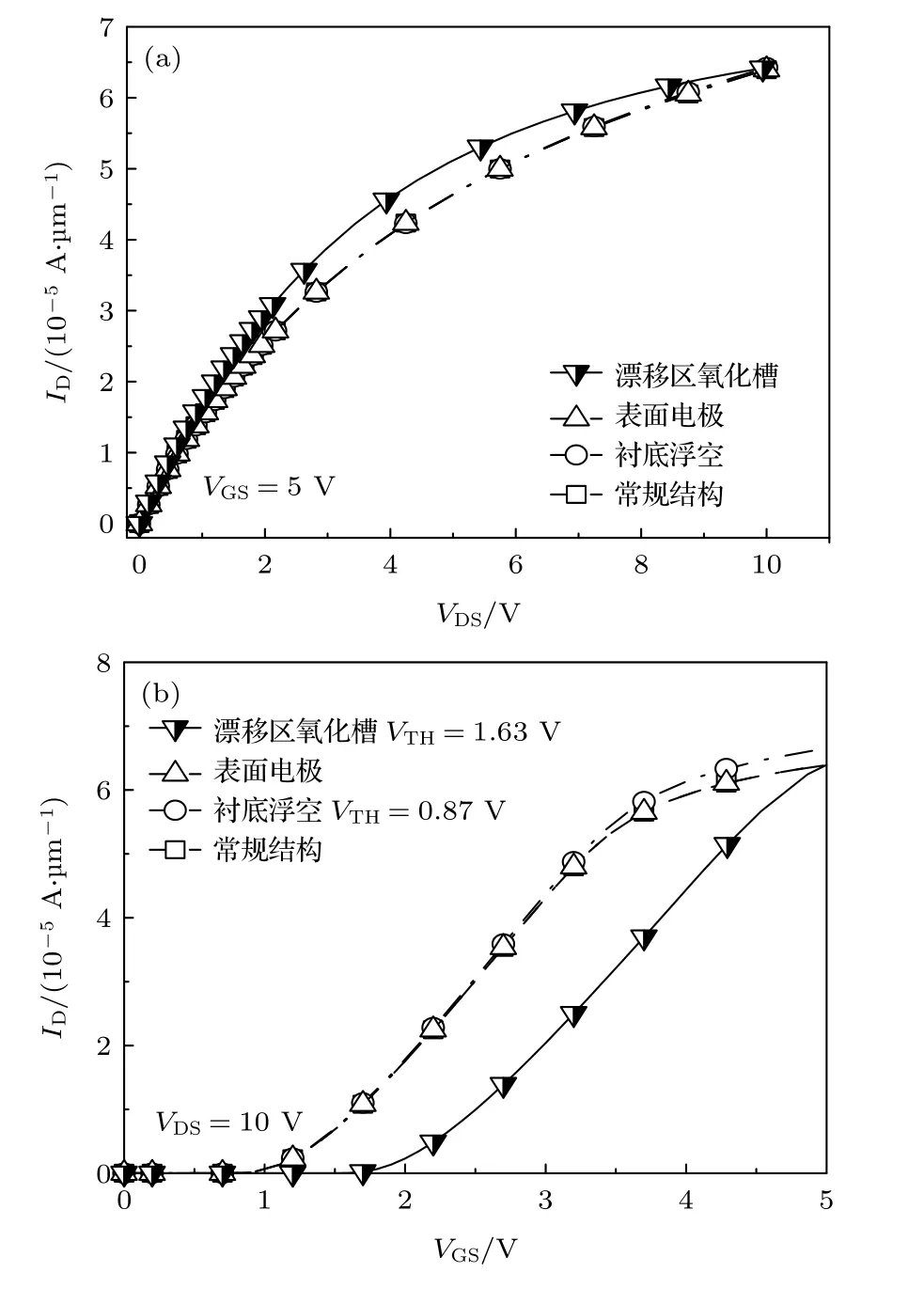

图8和图9所示为几种器件的击穿、转移、输出特性曲线. 由图8可知, 在衬底浮空后, SOI LDMOS的击穿电压从87.28 V降低到72.13 V, 下降了17.4%, 加上表面衬底电极后, 击穿电压恢复到常规SOI LDMOS的击穿电压. 比导通电阻都为2.21 mΩ·cm2, 没有明显变化. 在漂移区加上氧化槽以后, 横纵向电场得到同时优化, 击穿电压提高到137.5 V, 相比于常规SOI LDMOS增加了57.54%. 由图9可知, 增加漂移区氧化槽之前的几种器件阈值电压为0.87 V, 衬底浮空对阈值电压没有明显影响. 在加了漂移区氧化槽后, 阈值电压(threshold voltage,VTH)增加到1.63 V. 与此同时, 衬底浮空对器件的电流、比导通电阻均没有明显影响. 通过上述分析可知, 该新型SOI LDMOS能够较好地缓解衬底浮空后的不良影响, 并且还能在比导通电阻变化不大的情况下提高其击穿电压.

图8 几种SOI LDMOS的击穿特性图Fig. 8. Breakdown characteristics of several SOI LDMOS.

图9 几种SOI LDMOS的仿真结果 (a) 输出特性曲线;(b) 转移特性曲线Fig. 9. Simulation results of several SOI LDMOS: (a) Output characteristic curve; (b) transfer characteristic curve.

图10 所示为该新型SOI LDMOS结构中漂移区浓度ND、氧化槽宽度DOX和厚度TOX等参数对击穿电压BV和比导通电阻RON,sp的影响曲线.如图10(a)所示, BV随ND的增加呈现出先上升后下降的变化趋势, 而RON,sp则呈现出下降的趋势, 因此综合考虑漂移区浓度最终选取5 × 1016—6 × 1016cm—3. 如图10(b)所示, BV随DOX的增加先迅速上升后变化不大, 而RON,sp变化趋势则与BV相反, 因此选取DOX为3—4 μm. 如图10(c)所示, BV随TOX的增加先上升后下降, 而RON,sp则随之增加呈现持续上升的趋势, 因此最终选取TOX为0.5—0.6 μm, 表2所列为该新型器件优化后对应的结构参数. 最终该新型SOI LDMOS的击穿电压为137.5 V, 比导通电阻为1.96 mΩ·cm2,能够实现在RON,sp基本不变的情况下将常规SOI LDMOS的BV增加57.54%, 从而实现常规SOI LDMOS在应用于有机半导体领域后衬底浮空时的性能优化, 也实现了将功率开关器件与有机半导体领域的新的突破与创新.

图10 新型SOI LDMOS的几种参数对BV和RON, sp的影响 (a) ND的影响曲线; (b) DOX的影响曲线; (c) TOX的影响曲线Fig. 10. Influence of several parameters of new SOI LDMOS on BV, RON,sp: (a) Influence curve of ND; (b) influence curve of DOX; (c) influence curve of TOX.

表2 新型SOI LDMOS器件仿真最优参数Table 2. Simulation optimal parameters for novel SOI LDMOS devices.

5 结 论

本文通过仿真和流片实验两种方式共同验证当常规且带有RESURF技术的SOI LDMOS在应用于有机半导体领域后, 衬底会浮空使得常规SOI LDMOS缺失衬底电极和RESURF技术, 同时使得SOI LDMOS中埋氧层优化电场的作用也消失, 进而使得常规SOI LDMOS的击穿电压从87.28 V下降到72.13 V. 针对该现象, 提出的具有P+多晶硅作表面衬底电极和漂移区氧化槽的新型SOI LDMOS结构能在比导通电阻没有明显变化的情况下, 将衬底浮空的SOI LDMOS击穿电压从72.13 V上升137.5 V, 相比常规SOI LDMOS增加了57.54%. 在实现SOI LDMOS与柔性衬底结合且不降低器件原本性能的同时, 实现了传统无机半导体功率器件与有机半导体领域新的突破与创新. 不仅能弥补有机半导体材料电子性能较差的缺陷, 同时还能拓展有机半导体的研究领域. 未来可以通过工艺的创新和改进, 给有机半导体领域功率半导体方向提供更多的创新和可能性.