60 mm 尺度CMOS 图像传感器装片工艺技术研究

2021-05-06

(中科芯集成电路有限公司,江苏无锡 214072)

1 引言

目前应用最为广泛的图像传感器有电荷耦合器件CCD(Charge-Coupled Device)和互补金属氧化物场效应管CMOS(Complementary Metal Oxide Semiconductor)[1]。其中,CMOS 因其集成度高,且能与数字电路形成片上系统(System on a Chip,SoC),具有低功耗、工艺成本低等特点,近年来被广泛研究,逐渐成为消费类电子产品的主流[2]。其种类包含感光阵列、列放大器、模拟信号处理电路、数字信号处理电路,帧(行)控制电路和时序电路、A/D 转换电路等[3]。由于CMOS 芯片的像素很高,因此芯片的尺寸相对较大,通常在30 mm 以上,最大尺寸可达100 mm。

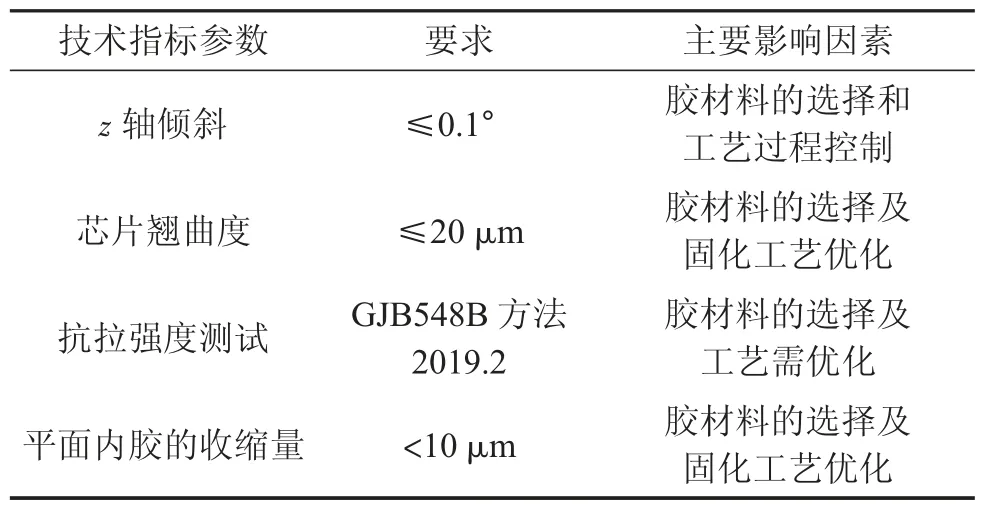

为了保证CMOS 图像传感器工作时的扫描精度和扫描范围,对芯片贴装的平面度有非常严苛的要求,具体要求如表1 所示。这对60 mm 以上超大尺寸CMOS 图像传感器芯片的贴装工艺来说是一个非常严峻的挑战。关于大尺寸芯片与超薄芯片的封装翘曲问题,国内外从工艺、变形机理、协同设计等角度进行了研究[4-8]。

表1 60 mm 级CMOS 图像传感器装片要求及主要影响因素

本文针对一款60 mm 尺度超大尺寸CMOS 芯片装片工艺,通过装片结构分析、装片胶的材料选择和装片工艺参数的优化,解决芯片装片倾斜和表面不平整问题。

2 结构设计

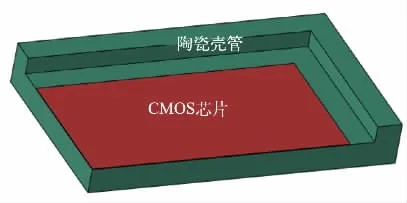

CMOS 图像传感器芯片通过装片胶贴装在管壳底座上。该装片结构的基本模型是一个芯片/装片胶/管壳三明治结构。图1 为该三明治结构的简化模型(四分之一对称仿真模型)。管壳材料相对明确,一般选择氧化铝陶瓷管壳。图中红色区域为CMOS 芯片。CMOS 芯片的尺寸为63 mm×32 mm,厚度仅为50 μm,属于超大而且超薄的CMOS 芯片。介于芯片与管壳之间的材料为装片胶,厚度为25 μm。

CMOS 芯片的翘曲与芯片、装片胶、管壳之间的热膨胀系数(CTE)不匹配有关。陶瓷管壳为氧化铝材料,CTE=6.9×10-6/℃,芯片为硅材料,CTE=2.6×10-6/℃。通过有限元仿真,可以获得封装结构从工艺温度150 ℃冷却到室温之后芯片的翘曲度。因此,对于高精度的装片要求,需要考察装片胶材料对装片翘曲的影响。从热残余应力分析角度看,主要考察装片胶的膨胀系数与装片胶的弹性模量的影响。

图1 有限元仿真模型

影响芯片贴片精度和翘曲度的因素是多方面的。人员操作的因素,可以通过人员培训将问题排除;设备方面的影响因素有点胶系统的稳定性、传送系统震动和装片夹具的精度;材料方面,装片胶的CTE、弹性模量参数都是影响芯片翘曲度的重要因素;工艺方面,基于装片胶特性和芯片面积,选择合适点胶针高度、点胶图案、点胶量以及固化程序,可有效控制芯片翘曲度和收缩率在目标范围内。

本文从两个方面进行评估:1)装片胶的选择评估,通过不同装片胶的性能比对,结合有限元结构仿真,选择符合产品规范的装片胶;2)针对优选的装片胶型号,进一步优化工艺参数,主要从点胶厚度和固化程序优化进行评估。

3 装片胶的选择

3.1 管壳尺寸及装片胶的膨胀系数、弹性模量的影响

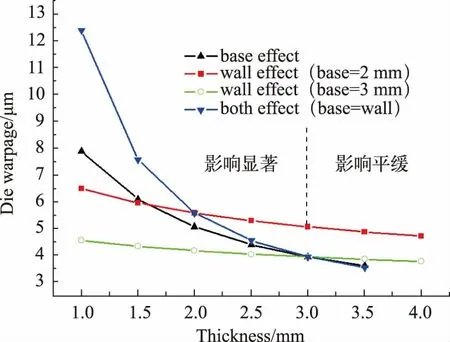

为了减少管壳尺寸因素对装片翘曲的影响,在研究装片材料对芯片翘曲的影响之前,首先对管壳壁(wall)和管壳底部(base)的厚度进行了研究。仿真分析通过Abaqus 软件进行。结果表明(见图2),增加管壳壁的厚度或者增加管壳底部的厚度,都可以提高装片后芯片的翘曲度,降低芯片的翘曲。其中,管壳壁厚度的影响相对平缓,而管壳底部厚度的影响更为显著。为了尽量减少管壳因素对芯片翘曲的影响,管壳壁的厚度和管壳底部的厚度均可在3 mm 以上。

图2 管壳壁厚尺寸对CMOS 芯片翘曲的影响

假定管壳壁厚度为3 mm,底部厚度为3 mm,对胶的膨胀系数与弹性模量的影响展开研究。装片胶的膨胀系数的变化范围为50×10-6/℃~400×10-6/℃,而弹性模量的变化范围为10 MPa~3000 MPa,基本涵盖各种装片胶的性能范围。

图3 装片胶的CTE 与弹性模量对芯片翘曲的影响

根据图3,在装片胶CTE 不变的情况下,适当提高装片胶的弹性模量,有助于减少装片后的芯片翘曲。图中的各条曲线大致相交于模量为2.2 GPa 处,表明装片胶的弹性模量为2.2 GPa 左右时,装片后芯片的翘曲较为稳定与优化,为3.2 μm 左右。过大的弹性模量,会引入封装应力,对超薄芯片抵抗应力不利。当装片胶的弹性模量比较低时(小于2.2 GPa),表现为装片胶的膨胀系数越低,芯片的翘曲就越小。所以,低膨胀系数的装片胶是一个比较优化的选择。

3.2 装片胶优选

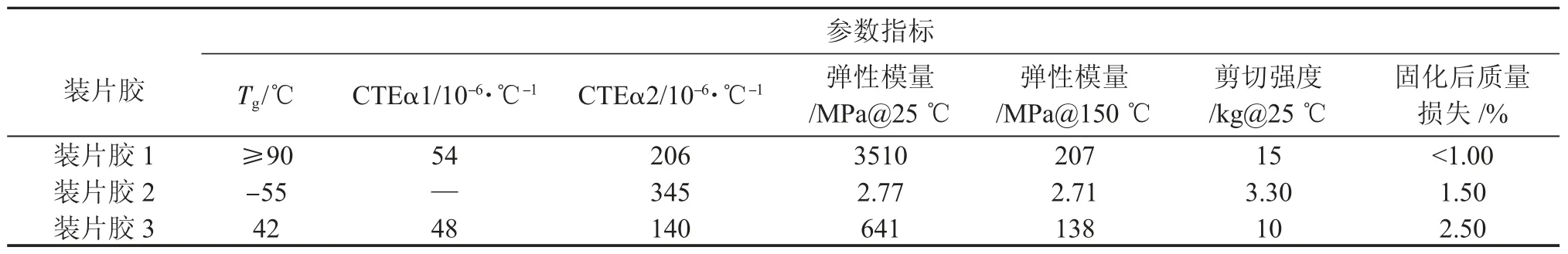

相对于DSP、FPGA 等集成电路芯片,图像传感器芯片功耗一般不大,且通常对芯片衬底电位无要求,本文主要选择承受温度在200 ℃的非导电胶。表2 是传感器芯片的3 款常用装片胶的性能。这些性能包括玻璃化转变温度(Tg)、高低温下的CTE、高低温下的弹性模量、剪切模量和质量稳定性等。当温度低于Tg时,环氧装片胶呈玻璃态;当温度高于Tg时,环氧装片胶硬度明显下降,呈橡胶态,且CTE 也产生变化。CTEα1是指温度低于Tg时材料的热膨胀系数,CTEα2 是温度高于Tg时材料的热膨胀系数。如果二者相近,则Tg不在考虑范围;如果二者相差非常大,装片胶Tg应该尽可能高于器件工作温度,以保证CMOS 芯片在工作时的翘曲度及可靠性。

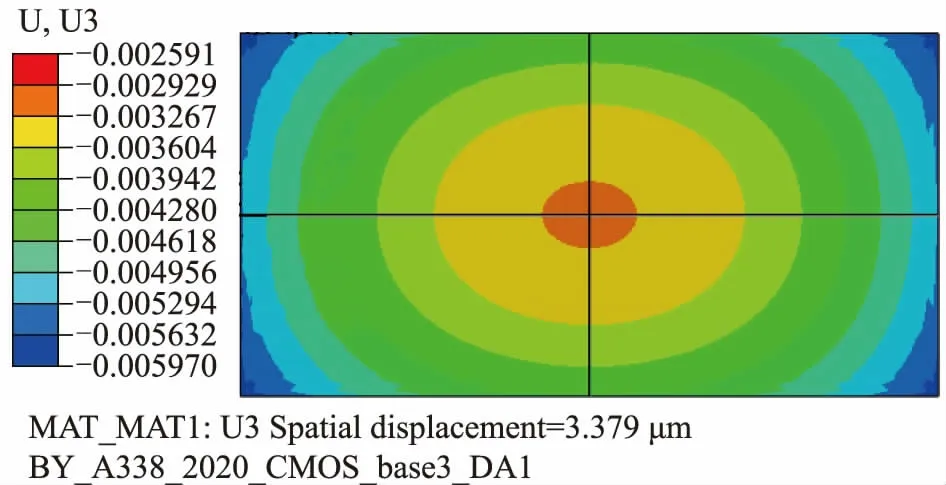

针对3 款常用装片胶用有限元仿真优选,3 款胶具有不同的Tg温度、热膨胀系数和弹性模量(如表2所示)。仿真结果见表3。图4 为采用装片胶1 时芯片的翘曲云图,装片胶2 与装片胶3 的云图与之类似。共同特点是芯片的翘曲均不大,在3.5~4.0 μm 范围内。3 款装片胶均能满足芯片整体翘曲度小于20 μm 的要求。由于陶瓷管壳的膨胀系数比芯片的膨胀系数略高,因此降温过程收缩更大,于是芯片翘曲形状体现为中部位置比四周的位置要高些。

表2 装片胶主要参考指标比对

表3 3 款装片胶的翘曲仿真结果

图4 装片胶1 的翘曲云图

从装片胶的化学稳定性(释气)进行优选。装片胶1 的固化释气值(Weight Loss on Cure)非常小,预测胶在固化过程中的排气量(Out Gassing)比较小,可很好地控制密封器件的释气。装片胶3 的各项性能介于装片胶1 和2 之间,不足的是固化释气值比较高,且装片胶3 的Tg接近器件工作温度,因此装片胶3 不在考虑范围内。

从装片胶的粘接强度进行优选。装片胶2 的Tg非常低(-55 ℃),模量非常小(仅2.77 MPa),材料非常软,胶的CTE 非常大(345×10-6/℃)。表3 表明,装片胶的等效应力越小,胶的剪切强度也越小。通过比对装片胶1和装片胶2 在25 ℃下的芯片粘接力,可以发现装片胶1 的芯片剪切强度是装片胶2 的4.54 倍。因此,装片胶2 的膨胀系数偏大,芯片粘接力偏低。

总之,装片胶1 粘接芯片与管壳的粘接强度高,且装片胶1 的Tg高于器件工作温度,CTEα1 较小,预期器件工作时胶的变形量小,可靠性有保证,最终选择装片胶1 为该工艺使用的材料,进行工艺优化。

4 装片工艺参数优化

装片胶1 是双组份胶,在使用前按比例混合搅拌,并进行脱泡处理。用压力-时间点胶系统,压力值固定不变,点胶量的多少与点胶时间成正比。在进行点胶试验前,需要先计算合适的点胶量,根据点胶量评估点胶针直径和点胶行程。

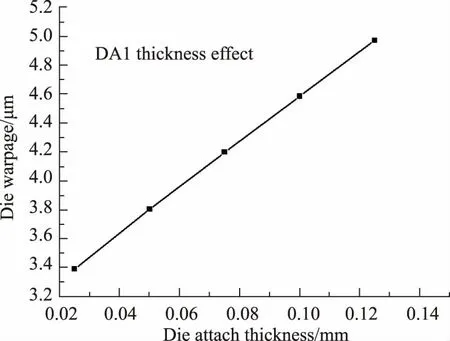

首先分析点胶厚度对芯片翘曲度的影响。根据装片胶1 的特性,通过有限元分析点胶厚度25~125 μm时芯片翘曲度值,参见图5。有限元分析结果显示,在点胶厚度范围25~125 μm 内,装片胶厚度越小,芯片翘曲量越小。这种现象可以解释为装片胶与芯片之间存在CTE 的差异,在拉伸模量比较高的情况下,胶层越厚,装片胶因CTE 失配对芯片的“拉扯”程度越大。

图5 装片胶1 的厚度对芯片翘曲的影响

根据图5 所示的仿真结果,胶层太厚对芯片翘曲影响大,而胶层设定太薄会造成胶量不好控制易产生空洞,因此固化后装片胶厚度目标设定值在30 μm。

点胶完成后进行装片胶的固化,固化曲线一般包含升温(控制升温速率)、恒温和降温(控制降温速率)。通常而言,固化峰值温度越高,装片胶与芯片的粘结强度越大,Tg也越高,但胶的收缩率也会相应变高,因此根据需要选择一个合适的固化峰值温度非常重要。通过胶材料的性能可知,该胶最低固化温度是120 ℃,环氧树脂开始发生一系列的交联固化反应,同时保持一定的恒温时间,能够保证固化充分。

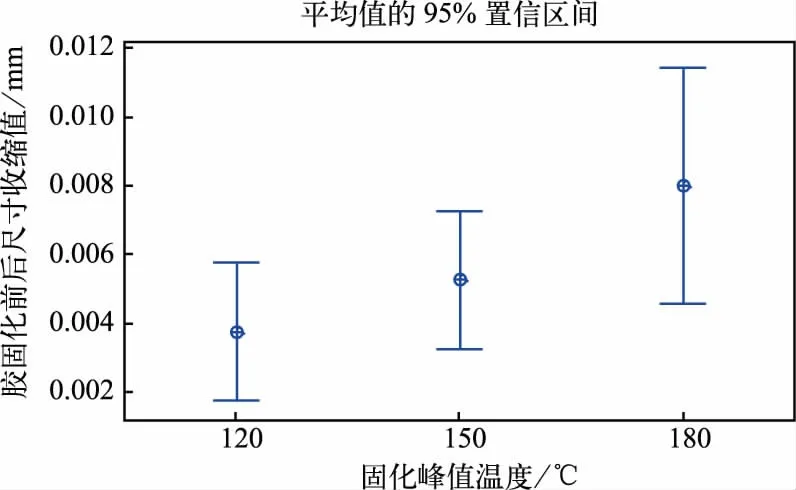

过高的升温速率,会使装片胶内一些反应单体迅速挥发,装片胶收缩率变大,胶与芯片之间的应力增大。因此降低固化升温速率,或者采用两步固化,可以有效地降低装片胶收缩率,进而控制芯片的翘曲度和倾斜度。过快的降温速率会对芯片产生热应力,但过慢会影响产能。因此降温速率一般选择最大自然降温速率,器件在烘箱内降温至100 ℃后取出,在环境氮气下自然降温。结合胶材料的性能和实际生产情况,对装片胶1 采用两步升温工艺,先升温至90 ℃,再升至峰值温度下固化1 h。试验分别评估120 ℃、150 ℃与180 ℃峰值温度下胶的收缩尺寸,如图6 所示。峰值温度条件为120 ℃和150 ℃,胶固化前后收缩尺寸均能控制在10 μm 以内,满足胶收缩率小于10 μm 的要求。通过差示扫描量热法(DSC)检测,峰值温度为150 ℃,1 h 后胶已完全固化。因此最终选择2 步升温固化方式,先升温至90 ℃,再在峰值温度150 ℃下固化1 h。

图6 不同固化峰值温度下胶收缩尺寸对比

衡量点胶固化工艺是否符合要求,主要是对固化后芯片翘曲度、胶的收缩、粘接强度检测以及后续的可靠性试验进行评估。通过3 点固定平面,计算芯片表面最大高度与最小高度的差值为翘曲度,图7 为固化后检测芯片翘曲度的控制图,可以得出芯片的翘曲度远低于20 μm 的控制范围。

图7 芯片翘曲度的I-MR 控制图

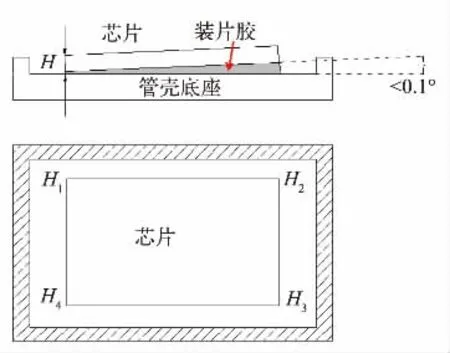

图8 所示为芯片装片后的倾斜度,计算通过对芯片4 个角的位置与陶瓷管壳底部上表面的高度差(H1、H2、H3和H4),然后得到芯片对角线位置的高度差与芯片对角线长度比值的反正弦角度小于0.1°,即arcsin|H1-H3|或者|H2-H4|/ L对角线<0.1°。最终通过测量和计算,倾斜度小于0.1°,满足工艺要求。

图8 芯片贴片倾斜度测量示意图

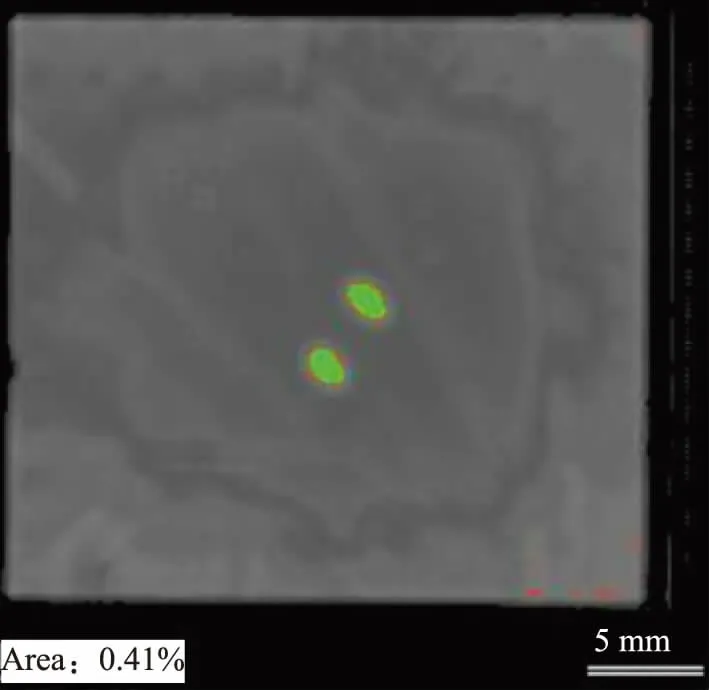

图9 为超声扫描观察固化后芯片与管壳的粘结情况,空洞占芯片面积比率(0%~5%)均优于20%的要求(GJB548B-2005 方法2030)。芯片粘接强度采用拉脱强度检测,测试数据大于20.00 kg,断裂模式为芯片与粘结材料,基板未脱离,满足GJB548B-2005 方法2019.2 的1.0 倍判据(大于6.71 kg)要求。

图9 固化后C-SAM 芯片的粘接层空洞

5 结论

管壳尺寸优化结果表明,陶瓷管壳壁厚3 mm 以上、底厚3 mm 以上时,管壳尺寸对芯片翘曲的影响相对平缓,有助于降低芯片的翘曲。封装结构中管壳尺寸的优化为研究装片胶材料性能对芯片翘曲的影响打下了基础。通过研究装片胶的材料性能(弹性模量和膨胀系数)对芯片翘曲的影响,发现当装片胶的弹性模量在2.2 GPa 左右时,装片胶膨胀系数的变化对芯片翘曲度的影响达到最小,有助于获得稳定的封装质量。对几种装片胶材料进行了优选,控制其释气率(化学稳定性)和装片胶的粘接强度。最后通过优化装片胶的厚度、固化工艺参数等,实现了芯片翘曲度小于20 μm 的要求(实际小于10 μm),同时芯片的粘结可靠性满足要求。