JESD204C协议接收端64 B/66 B链路层电路设计

2021-04-19张春茗王一平

张春茗,杨 添,王一平

(西安邮电大学 电子工程学院,陕西 西安 710121)

模数转换器(Analog-to-Digital Converter,ADC)和数模转换器(Digital-to-Analog Converter,DAC)作为模拟信号和数字信号相互转换的关键部件被广泛应用在航空航天、医疗仪器和移动通信领域[1-2]。随着应用的迅速增长,对ADC和DAC转换速率和精度的要求快速增长,这对转换器接口的数据传输速率、传输效率和传输稳定性有了更高的要求[3]。为了满足这些需求,联合电子设备工程委员会(Joint Electron Device Engineering Council,JEDEC)发布了其数据转换器的串行接口标准(JEDEC Standard Serial Interface Data Converters No.204,JESD204)。

JEDEC发布的JESD204协议有A、B和C三个版本[4]。与互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)信号和低压差分信号(Low-Voltage Differential Signaling,LVDS)并行接口协议相比JESD204B版协议有着单通道传输速度高、印制线路板(Printed Circuit Board,PCB)布线设计简单等优点[5-6],被广泛应用于高速转换器接口的设计中。

目前,对JESD204的研究主要集中在应用方面,即其内部电路的实现方法,例如,文献[7]采用控制信息与数据信息并行处理的方法设计了JESD204B接收系统中的同步电路。文献[8]采用极性信息简化编码技术实现了JESD204B中8B/10B编码电路的设计。文献[9]基于JESD204B协议设计了适用于3 Gbit/s 12位模数转换器ADC的接口电路。但是,JESD204B有着单通道数据传输率不能超过12.5 Gbps的限制,在实现更高带宽的数据传输时,需要更多的通道数,增加了布局布线的难度,无法支持实现尺寸较小的解决方案。

相比于JESD204B协议,JESD204C协议将所支持的单通传输速率提升到了32 Gbps,有效数据传输效率提升到97%,这意味着可以用更少的通道来完成数据的传输,更少的互连可以简化布局布线,支持实现尺寸更小的解决方案[10-11]。JESD204C协议发布后很快被国外的转换器制造商应用于实际,例如,德州仪器(Texas Instruments,TI)公司发布的ADC12QJ1600和亚德诺半导体技术有限公司(Analog Devices Inc,ADI)发布的AD9081均采用JESD204C接口。目前,国内对于JESD204C接口的应用和研究进展较慢,有待进一步深入。

JESD204C协议支持的单通道传输速率和有效数据传输速率比JESD204B协议高的原因之一是增加了对64 B/66 B链路层的支持。该链路层规定了新的数据同步机制、加扰机制和数据校验机制。采用何种方法实现这些新规定的机制,影响着接收端64 B/66 B链路层电路的整体性能。

本文拟提出一种64 B/66 B链路层电路的设计方案。在头同步功能实现过程中,通过增加位数据滑动状态(SH_SLIP)的方法,来完成并行数据中同步头序列的检测,以减小电路设计的复杂度。拟采用并行设计思想,完成解扰电路和12位循环冗余校验(12-bit Cyclic Redundancy Check,CRC12)电路的设计,以满足接收端64 B/66 B层以块为单位进行数据处理的要求。

1 64 B/66 B链路层协议解析

JES204C协议中的64 B/66 B链路层分为发送端和接收端。发送端通过给64位样本加扰数据添加同步头的方式,将负载数据以块、多块和扩展多块的数据格式发送给接收端。接收端通过头同步、多块同步、扩展多块同步、解扰、冗余校验等操作来完成发送端64 B/66 B链路层传输数据的恢复[12]。66位数据块由2位同步头后接64位样本加扰数据构成[13],其结构示意图如图1所示。其中,SH表示2位同步头;S0到S7表示由8个8位字节所构成的64位样本加扰数据。

图1 66位块数据结构

同步头由同步字中的同步位映射而来,同步位值为1时所对应的同步头为10,同步位值为0时所对应的同步头为01。一个同步字有32个同步位,它包含有多块尾序列、扩展多块尾标记位、命令字和多块数据的校验码。根据包含校验码或命令字位宽的不同,可将同步字分为独立命令通道同步字、12位循环冗余校验码(12-bit Cyclic Redundancy Check,CRC12)同步字、3位循环冗余校验码(12-bit Cyclic Redundancy Check,CRC3)同步字和前项纠错(Forward Error Correction,FEC)码同步字,用户可根据电路所支持的检错机制来选择对应类型的同步字生成格式。

设计所支持的检错机制为CRC12冗余校验,其同步字(S_word)映射格式如表1所示,表中CRC12为前一个多块数据的12 bit冗余校验码。CMD为7 bit命令字信号。EOEMB为扩展多块尾标记位,当EOEMB值为1时,表明当前多块为扩展多块;后5位的00001序列为多块尾序列[13]。

表1 12位循环冗余校验码同步字映射格式

2 接收端64 B/66 B链路层电路设计

采用自顶而下的设计方法,进行接收端64 B/66 B链路层电路的设计,设计的电路架构示意如图2所示。该电路包括速箱模块(Gearbox)、头同步模块(SH_aligment)、同步头处理模块(Head_handler)、解扰模块(Descramble)、CRC12校验模块(Crc_mismatch)、数据缓冲器模块(Buffer)和缓冲器控制模块(Buffer_controller)。

图2 接收端链路层电路架

2.1 变速箱设计

物理层与链路层之间的数据传递通过变速箱来完成。变速箱主要功能是将64 bit数据转换成66 bit数据。变速箱包括异步先进先出(First Input First Output,FIFO)存储器模块和位宽转换模块[14]。异步FIFO模块进行数据的跨时钟域传输,位宽转换模块进行读写数据位宽的转换以及剩余数据位的处理。

位宽转换模块由两个移位寄存器、一个计数器和一个选择器构成。在写时钟域内,寄存器对输入数据进行两级寄存,使得位宽转换电路可以在同一时刻对128 bit数据进行采样处理。计数器在接收到第一个数据时开始计数,计数周期为32。选择器根据计数值从128 bit数据中选择66 bit数据输出,以此完成64 bit数据到66 bit数据的转换,不同计数值所对应的选择输出位如图3所示,图中d1表示一级寄存器的缓存数据,d2表示二级寄存器中的缓存数据,cnt表示计数器的计数值。

图3 输出位选择示意

当计数值为31时,33个64 bit数据已被完全转换为32个66 bit数据并进行输出。当计数值为32时,二级寄存器中的数据d2是计数值为31时一级寄存器中的数据,此时,从d2中选取的任何两位数据与一级寄存器中的数据d1构成的66位数据均为错误数据(此时选择器的输出值可随意给定),即当计数值为32时,异步FIFO的写信号写使能信号均需置为无效,阻止无意义的数据的写入,确保跨时钟域数据的正确性。

2.2 头同步电路设计

变速箱所转换的66位块数据中有效同步头的位置是不确定的,它可能在块数据中的任何比特位。若不满足JESD204C协议所定义的块数据格式,则接收端64 B/66 B链路层电路无法进行后续的数据处理。因此,需要头同步电路从66位并行数据中找出有效同步头的位置,恢复出正确的块数据。根据协议中所规定的头同步达成条件,头同步电路中有SH_INIT状态、SH_HUNT状态、SH_LOCK状态和SH_SLIP状态4个工作状态,它们之间的转移过程示意图如图4所示。

图4 并行数据头同步状态转移过程

链路复位后,电路进入SH_INIT状态。在此状态下,电路对块数据中同步位上的同步头序列进行检测,并对检测到的无效同步头序列进行计数。当检测到的无效同头序列累计到2 048个时,若还未检测到有效同头序列,则电路进入SH_SLIP状态;当检测到有效同步头序列且无效同步头序列累计检测个数小于2 048时,电路进SH_HUNT状态。

在SH_HUNT状态下,电路继续对块数据中同步位上的同步头序列进行检测,并对检测到的有效同步头序列进行连续计数。若检测到64个连续有效的同步头序列,则电路进入SH_LOCK状态;若未检测到64个连续有效的同步头序列,则电路进入SH_SLIP状态。

在SH_LOCK状态下,电路继续对块数据中同步位上的同步头序列进行检测,并对检测到的无效同步头序列进行计数。若检测到的无效同步头序列累计有16个,则电路进入SH_SLIP状态。

在SH_SLIP状态下,对同步头序列位置指示计数器加1,并将新指定的同步头序列挪移到块数据的同步位上,即块数据的最低位,新指定同步头序列后的数据依次向前挪移。挪移完成后,电路再次转移到SH_INIT状态。

2.3 同步头处理电路设计

同步头处理电路的功能包括扩展多块同步、校验码转换和错误多块尾序列检测等。同步头处理电路包括EMB_INIT状态、EMB_HUNT状态和EMB_LOCK状态等3个工作状态,它们之间的状态跳转过程示意图如图5所示。

图5 同步头处理电路跳转过程

系统复位后,电路进入EMB_INIT状态。在此状态下,电路对同步头中包含的扩展多块尾序列(EOEMB=100001)进行监测,若在同步头锁定信号有效的情况下监测到扩展多块尾序列,则进入EMB_INIT状态。

在EMB_HUNT状态下,电路对扩展尾部位上的序列值进行检测,若在4个连续的扩展多块尾部位检测到4个有效的扩展多块尾序列,则说明扩展多块同步完成,电路进入EMB_LOCK状态;若在扩展多块尾部位检测到无效的扩展多块尾序列,则进入EMB_INIT阶段。

在EMB_LOCK状态下,接收数据中多块尾和扩展多块尾的位置已经确定,电路可以从同步头中恢复出相应的多块冗余校验码,对接收数据进行冗余校验。另外,在EMB_LOCK状态下,继续对多块尾和扩展多块尾部位上的序列值进行监测,并对监测到的无效扩展多块尾序列进行计数,若累计监测到8个无效扩展多块尾,则电路进入EMB_INIT状态。

2.4 CRC12校验电路设计

JESD204C协议规定64 B/66 B链路层必须支持使用CRC12校验码对数据传输中出现错误的监测,12位循环冗余校验码生成多项式为

G(x)=x12+x9+x3+x2+x+1

(1)

其中:x12、x9、x3、x2和x分别表示第12级、第9级、第3级、第2级和第1级寄存器反馈线;常数1表示输入数据存在反馈。

发送端计算每个多块数据的12位冗余校验码并映射到同步头中传输到接收端,接收端CRC12校验电路对接收到的多块数据进行12位冗余校验码的计算并与从同步头中接收到的冗余校验码进行对比。若CRC12校验码不一致,则说明接收到的数据至少存在一位错误,触发错误标志。

CRC12校验码有串行与并行两种计算方式[15-16]。单独使用并行或串行方式来完成多块数据冗余校验码计算,都不足以满足64 B/66 B链路层电路的数据处理格式,为此,采用串并结合的方式来完成多块数据冗余校验码计算电路的设计。设计电路在一个时钟周期内进行64位并行数据的冗余校验码计算,然后,连续计算32次64位并行数据的冗余校验码,第32次计算所得的冗余校验码为多块数据的冗余校验码,即在多块尾对计算所得的冗余校验码进行取值。

块负载数据的并行计算方式由串行计算方式迭代64次所得,串行计算方式中处理j+1位数据后CRC寄存器中的值由处理j位数据后CRC寄存器的值、多项式系数值和处理数据值进行逻辑运算得到,逻辑运算关系表达式为

(2)

其中:Ci,j+1(j=0,1,2,…,63;i=0,1,2,…,12)表示处理完j+1位数据后CRC寄存器中第i位的值;C11,j表示处理完j位数后CRC寄存器中第11位的值,dj+1为第j+1位输入数据;gi为多项式系数;Ci-1,j表示处理完j位数后占据CRC寄存器中第i-1位的值。

2.5 解扰电路设计

JESD204C协议中64 B/66 B链路层所采用的自同步加解扰多项式为

G(x)=x58+x39+1

(3)

其中:x58和x39分别表示第58级和第39级寄存器反馈线;常数1表示输入数据存在反馈。

解扰电路有串行扰码方式和并行扰码两种方式[17]。64 B/66 B链路层中待解扰数据位宽为64位且数据传输数率需要达到32 Gbps,串行解扰方式难以满足要求,为此采用并行解扰的方式来等效实现,以满足链路层对数据传输速率的要求。设计的64位并行解扰电路架构示意图如图6所示。

图6 64位并行加扰电路架构

64位并行加扰电路由串行加扰电路递推所得。图6中的S1n、S1m和S1k(n、m、k=0,1,2,…,63)分别表示上一时刻接收到的并行加扰数据中的第n、m和k位;Sn、Sm和Sk表示当前时刻接收到的并行加扰数据中的第n、m和k位;Dn表示当前时刻64位解扰数据中的第n位。当前时刻64位解扰数据中的第n位与当前时刻和上一时刻接收到并行加扰数据中的第n、m和k位的关系可以表示为

2.6 弹性缓冲电路设计

弹性缓冲电路位于64 B/66 B链路层的各个通道之中,其控制并实现链路的多通道对齐功能。弹性控制电路监测电路各个通道的有效扩展多块尾序列。当检测到某个通道的有效扩展多块尾后,就将对应该通道的弹性缓冲使能置为有效,随后,弹性缓冲电路开始缓冲各自通道的解扰数据。当所有通道的弹性缓冲使能均有效时,弹性缓冲控制器电路将弹性缓冲器的释放使能置为有效,各个通道的弹性缓冲器均在同一时刻释放所缓存的数据,从而实现多通道数据对齐功能。

3 仿真与综合

3.1 仿真验证

为了验证设计电路的功能,使用verilog语言对JESD204C协议中发送端64 B/66 B链路层和C类物理子层的功能进行行为级建模,并且与设计的接收端64 B/66 B链路层电路进行回环对接验证。在VCS上搭建验证平台,验证平台架构如图7所示。其中,Input_sign_generate模块被用于提供并行数据流和时钟信号。Tx_64B/66B_link_layer和Phy_layer模块被用于模拟发送端64B/66B链路层和物理层的电路功能。Rx_64B/66B_ link_layer为设计的电路。

图7 验证平台架构图

采用以下两种方式进行对比验证,确保功能验证的完备性。

验证1将接收端恢复数据与发送端输入数据进行对比,以验证收发数据是否一致。

验证2人为构造负载数据传输错误、同步头传输错误和扩展多块尾序列传输错误,以验证接收端64 B/66 B链路层电路能否完成传输错误的检测与处理。

验证方式1中,发送端和接收端64 B/66 B链路层仿真验证波形图分别如图8和图9所示。图8中tx_data_L0与tx_data_L1分别为输入到发送端链路层的64位并行数据。L0_phy_data与L1_phy_data为经过发送端链路层处理过后送入发送端物理层的通道数据。图9中的L0_phy_data与L1_phy_data为接收端物理层发送到接收端链路层的通道数据。Rx_L0_data与Rx_L1_data为接收端恢复的64位有效数据。可以看出,发送端在20.30 ns时输入的数据,接收端64B /66 B链路层在22.45 ns时正确恢复并且双通道数据对齐,通过验证。

图8 发送端64B/66B链路层仿真验证波形图

图9 接收端64B/66B链路层仿真验证波形图

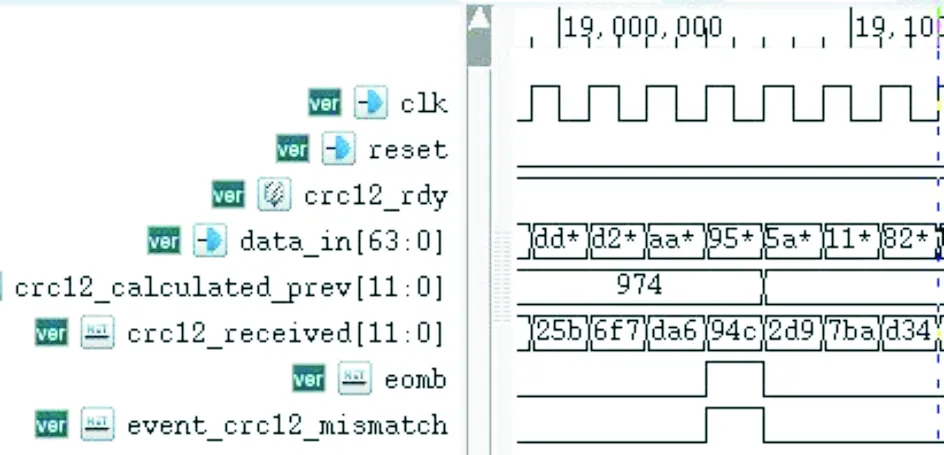

验证方式2中,人为构造负载数据传输错误后的仿真验证波形图如图10所示。图中crc12_calculated_prev为接收端通过接收数据计算出来的冗余校验码,crc12-received接收到的冗余校验码,eomb为多块尾标记信号,event_crc12_ mismatch为数据传输错误标记信号。人为插入错误数据后,多块尾处crc12_calculated_prev值与crc12 -received值不同,负载数据传输错误被检测。可以看出,接收端64 B/66 B链路层电路能够完成传输错误的检测与处理,通过了验证。

图10 传输错误后的仿真验证波形

3.2 综合结果

在Synopsys 公司的Design Compiler平台上,采用台湾积体电路制造股份有限公司(Taiwan Semiconductor Manufacturing Company,TSMC)90 nm互补金属氧化物半导体(Complementary Metal Oxide Semiconductor,CMOS)工艺对接收端64 B/66 B链路层电路进行综合,链路层电路参数如表2所示。设计电路的最大工作频率为484 MHz,相对应的时间裕度为0.27 ns,单通道的数据传输数率为32 Gbps,达到了JESD204C协议对64 B/66 B链路层传输速率的要求。

表2 接收端64 B/66 B链路层电路参数

基于不同高速串行接口协议所设计的接收端链路层电路参数如表3所示,可以看出,相较于文献[18]和文献[19]的方法,设计的接收端64 B/66 B链路层电路面积较小、有效数据传输速率和单通道传输速率较高。这是因为,接收端64 B/66 B链路层电路在完成链路同步功能时,仅需要对2 bit的同步头进行序列检测即可实现,从而减小了比较器资源的使用和电路面积。另外,电路按块格式处理数据,块数据中用于同步的非样本数据仅占2 bit,使得有效数据的传输效率达到96.97%,虽然电路使用较为落后的工艺实现,但是其最大的工作频率也可达到484 MHz,单个时钟周期内处理数据的位宽为66 bit,使得单通道最大数据传输速率达到了32 Gbps。

表3 不同协议的接收端链路层电路参数

4 结语

提出了一种基于JESD204C协议接收端64 B/66 B链路层的完整架构以及各个模块的设计方法。设计的接收端64 B/66 B链路层的关键模块包括变速箱、头同步检测器、同步头处理器、解扰器、传输错误校验器等。其中,采用位数据滑动的方法实现头同步模块设计,采用并行算法设计解扰模块和CRC12校验模块。仿真与综合结果表明,所设计的接收端64 B/66 B链路层电路的性能满足协议要求,可用于JESD204C高速串行接口电路设计中。