Gardner位同步算法及其在中继卫星模拟器中的应用 ①

2021-04-09朱博文韦玉锋吴皓威

朱博文,韦玉锋,高 洁,吴皓威,2*

(1.重庆大学,微电子与通信工程学院,重庆 400044;2.重庆大学,通信与测控中心,重庆 400044)

0 引言

随着太空探测的逐渐深入,传统的地基测控技术已经无法解决航天测控通信中距离遥远导致的信号损耗大、通信延迟长、连续测轨困难等问题[1]。因此,世界各国都在大力开展全球天基测控系统的研究与建设。20世纪80年代美国建立了全球首个数据中继卫星系统——“跟踪与数据中继卫星系统”[2]。目前,我国是继美国之后世界上第二个拥有对中、低地球轨道航天器全球覆盖的国家。中继卫星系统的建立为各种低轨航天器尤其是遥感卫星和侦察卫星、航空器等军民用户的中继数据提供了数据传输和跟踪服务,以较低的成本和较少的地面站解决了地面测控网低用户覆盖率的问题,在军民应用中发挥了重要的作用。

中继卫星模拟器是指中继卫星的测控链路模拟设备,在中继卫星的前返向链路中,调制方式多,如BPSK、QPSK、OQPSK、UQPSK、QAM等,码速率变化范围大,从10Kbps到10Mbps不等,因此需要中继卫星模拟器的发射机和接收机都具有很强的适应性,这给前返向链路接收机的设计带来了挑战。

位同步算法是中继卫星接收链路处理的关键技术之一,其目的是确定调制符号最大值的采样判决时刻。常用的实现方式有:插入导频法和直接位定时同步法[3,4]。前者需要插入专用导频,影响信息的传输效率。后者不需要在发送的码元序列中插入导频信息而直接从接收到的信号中提取出时钟,从而达到位同步的功能[5-7]。Gardner算法作为一种经典的直接位定时同步法,其结构简单、计算速度快,每个符号仅需两个采样点,易于高速实现。同时该算法具有检测性能不受载波是否同步的影响、对多种调制模式和码速率的信号具有很好的适应性等优点,在现在的通信系统中得到广泛应用。

1 算法原理

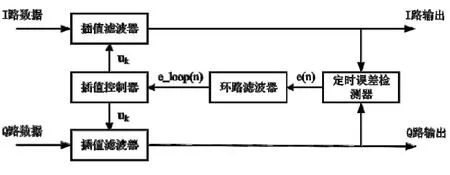

基于Gardner算法的位定时同步环路的实现框图如图1所示,主要包括定时误差检测器、环路滤波器、插值滤波器和插值控制器等。

图1 基于Gardner算法的位定时同步环路框图

1.1 定时误差检测器

定时误差检测器用来计算真实采样点与最佳采样点之间的偏差程度。Gardner算法进行定时误差检测时每个符号只要两个采样点,一个为符号的最佳判决点,一个为相邻两个最佳判决点之间的过零点。误差提取模块每个符号周期计算一次,BPSK、QPSK和QAM调制的理论计算公式为:

e(n)=I[(n-1/2)Tb](I[nTb]-I[(n-1)Tb])+

Q[(n-1/2)Tb](Q[nTb]-Q[(n-1)Tb])

(1)

而针对OPQSK调制信号的误差提取公式为:

e(n)=I[(n-1/2)Tb](I[nTb]-I[(n-1)Tb])+

Q[nTb](Q[(n+1/2)Tb]-Q[(n-1/2)Tb])

(2)

其中I[nTb]和Q[nTb]表示第n个码元时刻I/Q两路的采样值,I[(n-1)Tb]和Q[(n-1)Tb]则表示第n-1个码元时刻I/Q两路的采样值。I[(n-1/2)Tb]和Q[(n-1/2)Tb]表示相邻两个采样点之间的值。定时主要分为三种情况,定时准确,定时超前和定时滞后,如果超前,那么其误差为负,如果滞后,那么其误差为正。

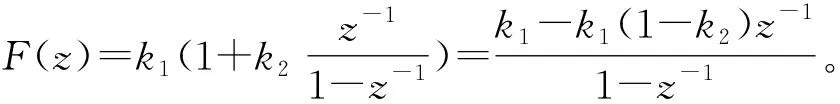

1.2 环路滤波器

环路滤波器中,K1和K2的取值直接影响到环路等效噪声带宽以及增益[8]。K1和K2越小,带宽越小,跟踪时间越长,抗噪声性能越好;同时K1和K2的增大可以使环路增益增加并减少捕获时间,但滤波性能会下降[9]。K1和K2的取值可以通过下面的公式计算求得:

(3)

(4)

其中,Tb中为NCO的更新周期,即为符号周期。而Kd和Ko为鉴相增益和NCO增益,ωn为环路自然频率,ξ为阻尼因子取0.707。

1.3 插值滤波器

插值滤波器通过对输入的信号进行重采样得到最佳采样信号,为便于实现,插值滤波器一般采用多项式插值方法[10],即:

(5)

工程中常使用的多项式插值滤波器有线性插值,立方插值和分段抛物线插值[11]。由于分段抛物线插值精度较高,所以本设计采用的是分段抛物线插值,其中

(6)

1.4 插值控制器

插值控制器的作用是确定重采样时刻Ti和输出分数间隔uk,它由数控振荡器(Numerical control oscillator,NCO)和分数间隔计算器两部分组成。NCO的作用是产生数字时钟,即确定插值基点mk,其参考时钟为原始采样速率fclk=1/Ts,在本设计中为16倍的符号速率。重采样的间隔为符号速率的两倍,这说明本设计中的NCO需要每隔8个参考时钟输出一个信号作为重采样时刻的标志。NCO是通过一个相位递减器实现的,其差分方程为[12]:

η(m+1)=η(m)-W(m)

(7)

其中,η(m)为NCO寄存器变量, 为NCO频率控制字,也即NCO每隔Ts就要减一个W(m)。当同步后,W(m)几乎稳定于某一恒定值。此时NCO每隔Ts*1/W(m)时间溢出一次,所以NCO的时钟周期为Ti=Ts/W(m),得到

(8)

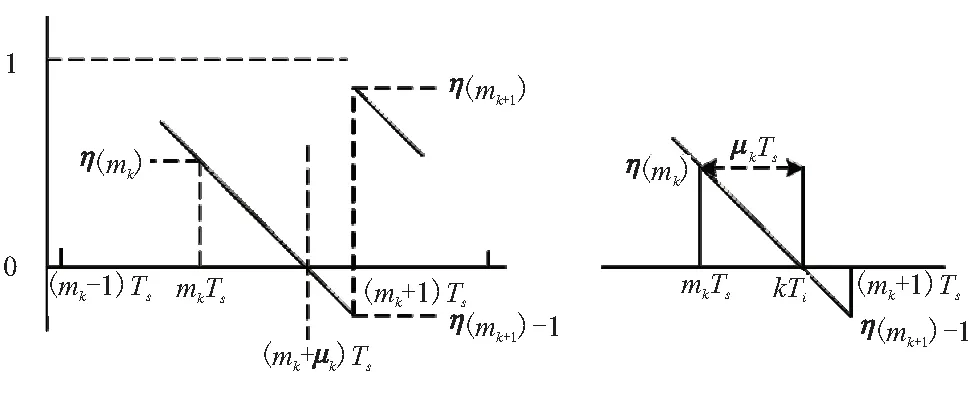

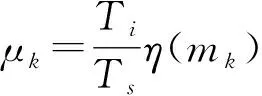

图2所示为计算分数间隔μk大小的参考图,主要是根据NCO中相位递减器的溢出值来计算的。其中,mkTs是插值基点,KTi=(mk+μk)Ts代表该码元的最佳采样时刻,η(mk)和η(mk+1)代表相位递减器的输出,在mk+1Ts时刻相位溢出,输出时钟。

2月9—10日,全国水利规划计划工作会议在辽宁沈阳召开。水利部部长、党组书记陈雷作《推进水利跨越式发展中规划计划工作应着力把握的几个问题》的重要讲话(全文本期刊发)。辽宁省委书记王珉出席开幕式。辽宁省省长陈政高致辞。水利部副部长、党组副书记矫勇主持开幕式并作总结讲话(全文本期刊发)。辽宁省副省长赵化明出席会议。水利部长江水利委员会主任蔡其华、黄河水利委员会主任陈小江出席会议。水利部总规划师兼规划计划司司长周学文宣读《关于表扬全国水利规划计划工作先进集体和先进个人的通报》并作工作报告。国家发展改革委、财政部有关领导在会上发言。

图2 相位递减器变化曲线

根据图2所示,由相似三角形原理易推出下面关系式:

(9)

将上式变形可得:

(10)

2 算法仿真

仿真条件:基带输入信号符号速率Rb=100Ksym/s~20Msym/s,采样频率fs=1.6MHz~320MHz,根升余弦成型滤波器滚降系数为0.35,信道所加噪声为高斯白噪声,信噪比为SNR=10dB,NCO的初始相位为1,初始频率间隔为0.125。阻尼因子ξ=0.707,鉴相增益kd=1.7,ko=1.0,利用ξ,kd,ko,Tb可得到环路滤波器系数K1,K2。输入信号经过内插器插值和定时误差检测器计算得出差值,再过环路滤波器滤波,送入插值控制器得到控制信号进而用于控制插值器,完成最佳采样点的选取。

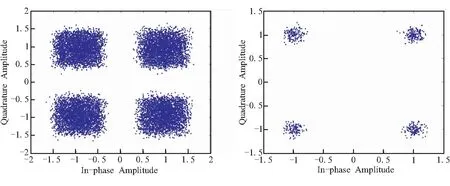

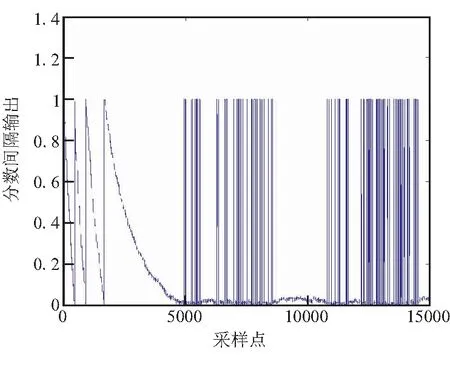

图3(a)所示为典型的符号速率Rb=10Msym/s,采样频率fs=160MHz,定时超前4个采样点时QPSK信号的星座图,从图中可以看出此时星座点比较发散。图3(b)所示为定时同步后的QPSK信号的星座图,对比图3(a)我们可以看出其收敛很多。图4为插值控制器计算输出的分数间隔,从图中我们可以看出在5000个符号周期后其值比较稳定,代表此时已经同步。其他任意符号速率及调制方式的位定时同步环路效果亦如此,表明了基于内插的Gardner位定时同步算法收敛速度快,可支持100kbps-20Mbps的宽码速率变化范围,而且适用于BPSK、QPSK、OQPSK、UQPSK、QAM等常见的天基测控信号的接收处理。

(a)定时前QPSK信号星座图 (b)定时后QPSK信号星座图

图4 分数间隔uk值

3 Gardner算法在中继卫星模拟器中的应用

3.1 卫星模拟器基带板卡硬件

卫星模拟器基带板卡是6U尺寸的CPCI板卡,主要包括三路射频链路、一路中频链路、信号处理FPGA和配置芯片等电路。射频链路主要采用ADI公司的AD9361;中频接收电路选用ADI公司的AD9626;中频的发射电路DA器件选用ADI公司的AD9957。信号处理FPGA采用英特尔公司Stratix IV系列,负责射频通路和中频通路的数据收发以及基带算法处理,其中有三个射频收发通路和一路中频收发通路,根据任务需求其他两个射频通道增设了两个备用收端通路。该板卡支持三种主流中继卫星的通信链路模式,具有很强的灵活性,既支持三条通信链路能同时工作也支持只有部分通信链路工作,并且射频芯片AD9361可以灵活配置收发的频点。硬件板卡实物如图5所示。

图5 硬件板卡

3.2 算法实现

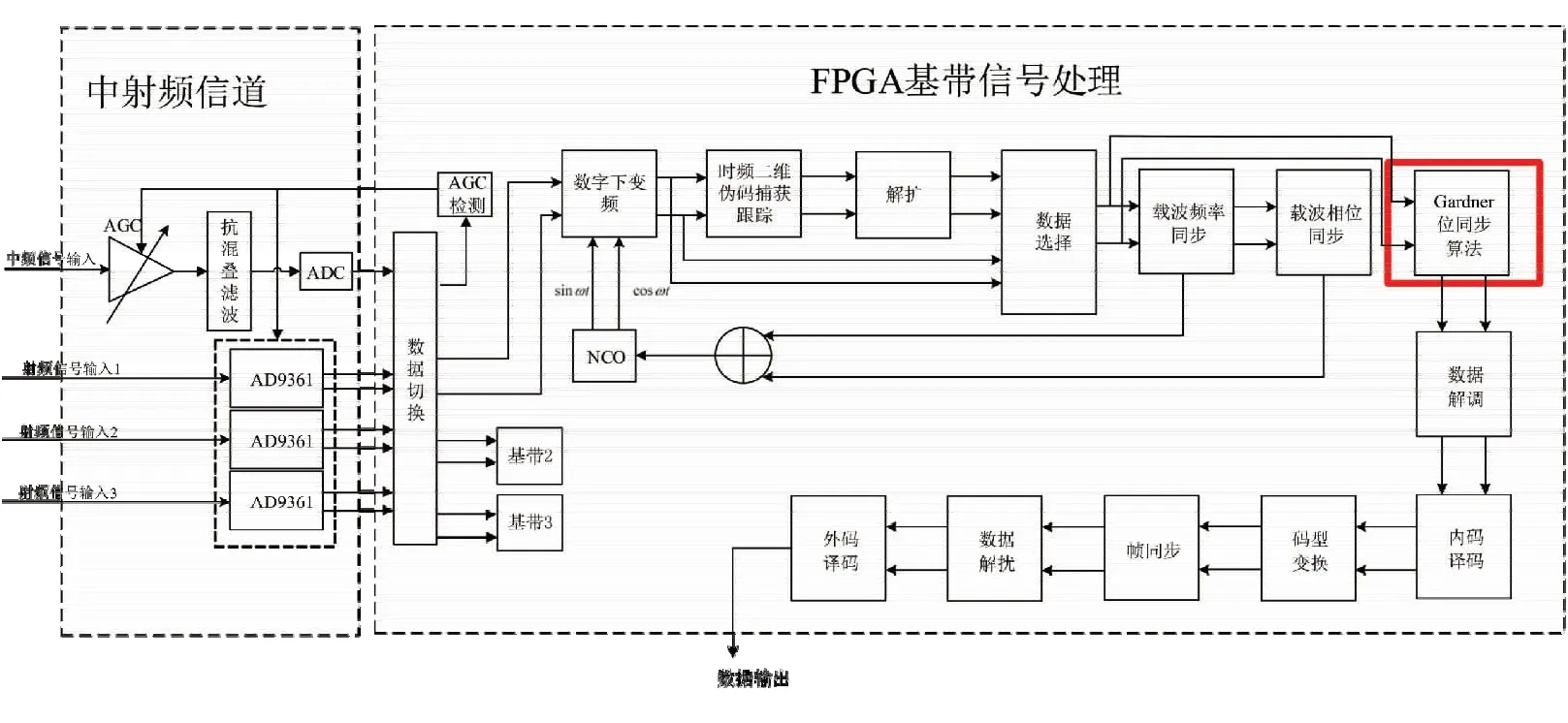

位同步是对数据进行解调和译码的前提,在中继卫星模拟器接收机中具有很重要的作用。针对三种主流的中继卫星通信链路的基带系统如下图6所示。由于Gardner位同步算法具有可处理高速信号、通用性强和收敛速度快等特点,因此在扩频和非扩频接收机中常采用Gardner算法来进行位同步。

图6 基带信号处理结构图

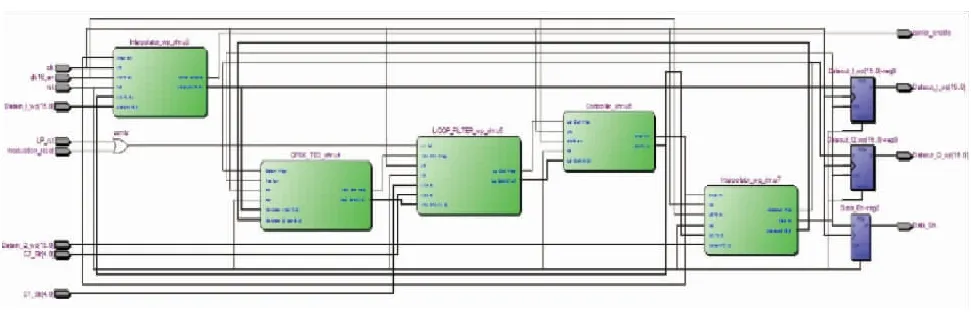

Gardner位同步算法实现的RTL图如图7所示,算法包括插值滤波器、位定时误差检测器、环路滤波器、插值控制器。

图7 Gardner算法的RTL图

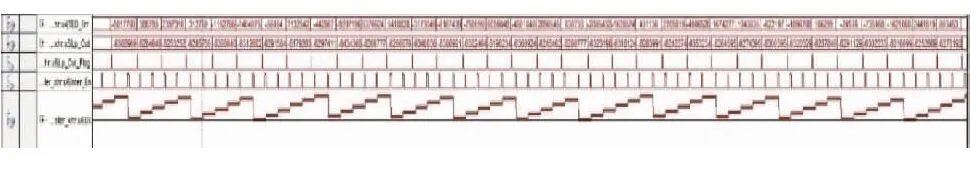

图8 Gardner位定时同步算法主要信号图

图8所示信号为定时误差TED_Err,环路滤波输出Lp_Out和分数间隔Uk,可以看到定时误差TED_Err经环路滤波器后的输出值已经趋于稳定,在其附近浮动不大,说明此时位同步已经完成。

4 结论

在中继卫星模拟系统中,本地时钟频率和实际接收信号频率难免存在偏差,导致接收信号码元不同步,误码率显著提高。本文从Gardner位定时同步环的基本原理出发,给出了定时误差检测的一般公式、环路滤波器系数的计算方法以及内插器、插值控制器的工作原理。在内插器对信号进行插值时,利用插值控制器给出的分数间隔即可计算出正确的插值位置,得到最佳采样点。使用MATLAB对环路设计进行性能仿真并在FPGA平台上进行了实现,结果分析指出,采用基于内插的Gardner位定时同步系统结构简单,易于实现,收敛速度快,不仅支持100kbps-20Mbps的宽码速率变化范围,而且适用于BPSK、QPSK、OQPSK、UQPSK、QAM等常见的天基测控信号的接收处理,可直接应用于各种卫星模拟器设备基带模块中。