基于FPGA的数字加速度计设计与实现

2021-03-05毕彦峰胡陈君

王 特,李 杰,毕彦峰,胡陈君

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.苏州中盛纳米科技有限公司,江苏 苏州 215123)

0 引 言

现代化战争中,制导弹药面临远程精确打击的作战需求,因此弹体飞行姿态的准确获取至关重要。加速度等惯性数据作为姿态获取中最重要的参数,会直接影响实时解算的准确性[1]。加速度传感器通常以模拟量输出,但在进行姿态解算时需要的却是数字量,所以需要对其进行模数转换[2]。由于三轴传感器的安装轴向并不是完全正交的,现有的加速度传感器在使用之前需要对传感器进行标定,在解算时还需对传感器进行轴向补偿来减少交叉耦合[3]。

针对以上问题,提出一种将三轴加速度传感器模拟量电压输出转换为加速度数字量输出的方法。三轴加速度计输出的模拟信号经调理后发送给A/D输入端,现场可编程门阵列(field programmable gate array,FPGA)控制A/D芯片将三轴加速度计输出的模拟信号转换为数字量,并通过FPGA将电压值与标定系数矩阵进行一系列的运算,将转换得到的加速度量化成为16bit数字量,相较以往模拟量输出而言,数字量输出精度更高便于处理。

1 系统总体设计

系统主要由三轴加速度计、信号调理单元、模数转换单元、采集控制单元和数据处理单元、以及接口转换单元等部分组成。系统的总体框架如图1所示,FPGA控制A/D芯片将三轴加速度计输出的电压值进行模数转换,通过数据处理单元将采集到的电压数字量换算为加速度数字量,并通过RS—422通信协议输出。

图1 系统总体设计

三轴加速度计由3个两两正交的单轴加速度计组成,信号调理单元主要是对三轴加计输出的模拟电压进行放大和滤波后输入到模数转换单元,采集控制单元通过FPGA控制A/D芯片将三轴加速度计输出的模拟量转换成为数字量,数据处理单元将采集到的数字量电压进行运算后转换成为加速度量化值,最后通过接口单元将其转化为差分信号传出。考虑到资源、性能和成本等方面的需求,模数转换单元采用TI公司的ADS8365芯片,量程为+5 V,采样精度为16位。采用Xilinx公司的Spartan—6系列FPGAXC6SLX9—144I作为主控芯片,此款芯片有9152个逻辑单元、102个可配置I/O,满足设计的需要[4]。

2 理论推导

2.1 基本理论

(1)

G==A·V

(2)

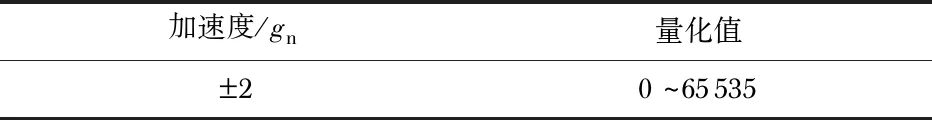

其次根据表1加速度的测量范围以及被转换的量化范围可以很轻易地计算出加速度与量化值之间的关系如式(3)所示,D为加速度量化值。

表1 加速度与其量化值对应关系

(3)

如果按照上述步骤进行计算,计算量很大而且浮点数乘法较多会导致精度损失。对以上公式进行化简可得

(4)

将前三个等式化简后,复杂的运算最终变成矩阵的一次加法和一次乘法运算。其中矩阵K和矩阵B为固定参数,可以提前算好并固化到程序中以减少不必要的运算,提高运算速度以及减少资源的使用。化简后利用整数和浮点数的运算将浮点数扩大,减少浮点数之间的乘法,有效地提高运算的精度。

2.2 浮点数精度的选择

在设计FPGA程序之前,需要确定程序中数据计算的精度。FPGA内为硬件电路,浮点数精度越低,所消耗的资源越少。如果单精度浮点数满足系统计算的需要,就不需要使用双精度浮点数,以此来减少硬件开销。

根据式(4),可得到式(5),其中D-B为正整数,所以需要将矩阵运算后的结果取整处理,对小数部分进行四舍五入

(5)

当数据精度选择为单精度时,K矩阵的最小值为10-6,ADS8365的量化值范围为-32 767~32 768,当参数矩阵K<10-6时:即Kmn<10-6m,n=1,2,3,可得到

|Knl·DataXMAX+Kn2·DataYMAX+Kn3·DataZMAX|≤10-6×3×32 768=0.098 304,n=1,2,3

近年来,智能交通领域更多涉及到深度学习的全面运用。在人工智能的操控下,智能化系统针对实时性的当前路况就能予以全方位的识别,然后借助摄像头来实现针对前方路况的预判。技术人员凭借人工智能手段还可提取微观性的路段通行信息,以此来预测当前所处路段是否表现为堵塞状态。通过运用宏观性的道路预测手段,针对即将行驶路段是否具备坑洼现象、路面塌陷以及路面施工等要素都能予以提前预知,从而保障了车辆得以顺利行驶。

(6)

根据式(6),当数据小于10-6时,产生的最大值为0.098 304,对最终结果的舍入几乎无法产生任何影响,所以最终程序中数据精度采用单精度浮点数。

3 数据处理单元

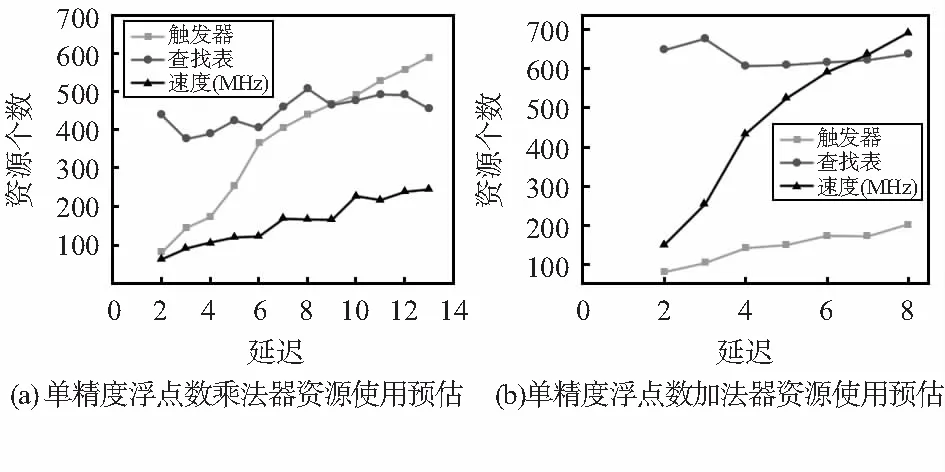

浮点数乘法和加法采用Xilinx公司提供的浮点数IP核进行乘法和加法运算,用户可以配置浮点数的精度为单精度浮点数、双精度浮点数以及自定义精度浮点数。自定义精度浮点数可以指定浮点数的阶码长度以及小数长度。另外,参考Xilinx官方提供的数据,浮点数IP核生成的模块数据输入到产生结果的延迟、资源的消耗与最高频率的关系如图2所示。延迟越高,资源的使用和频率上限越高[7]。

图2 单精度浮点数乘法/加法器资源使用预估

综合考虑到此设计的运行速度以及资源限制,本设计所采用的浮点数都为两级延迟,使能乘法器两个时钟周期后浮点数乘法器和加法器的输出才有效,最高运行频率为82 MHz,完全满足本设计的需求[8]。

在进行浮点数运算之前,仍有一个需要考虑的问题,即A/D芯片输出的值为16位的有符号整数,而浮点数IP核生成的浮点数乘法器不支持整数输入,所以需要将16位有符号整数转换为浮点数。Xilinx浮点数IP核不仅能计算乘法,还能提供浮点数和定点数相互转换的功能[9]。

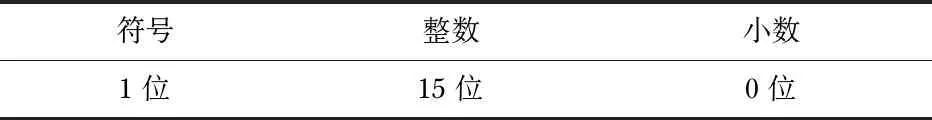

利用Xilinx浮点数IP核定点数转换为浮点数的功能将16位有符号整数转换为浮点数时,配置IP核如表2所示,定点数的整数部分设置为16位,小数部分设置为0位,输出选择单精度浮点数即可完成转换,并且会自动进行四舍五入。

表2 定点数转浮点数IP核配置

可表示范围为-32 768~32 767。

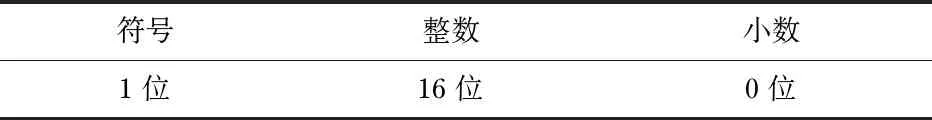

最后的计算结果为单精度浮点数,需要将其转换为正整数。此时需要将浮点数转换成为定点数,由于定点数带符号位,所以只有整数部分为17位时,才能输出最大65 535的整数[11,12],浮点转定点IP核配置如表3所示。当输入的浮点数大于65 535时,浮点数转定点数IP核将会时钟输出65 535。

表3 浮点数转定点数IP核配置

可表示范围为-65 536~65 535。

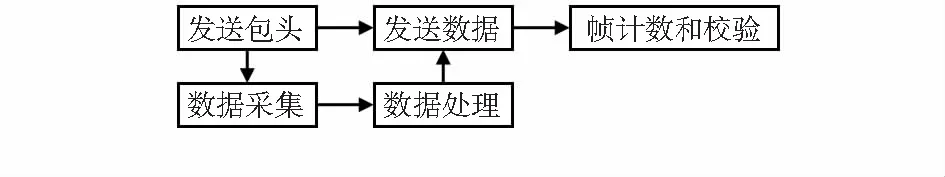

4 程序设计

数据计算的最终结果通过RS—422接口传输,为了提高传感器输出的实时性,在发送数据包头时才开始启动采集,当采集处理完毕后,直接将数据通过RS—422接口传输,在数据位后增加帧计数和校验和,便于对数据进行判读[10],程序设计的总体流程框图如图3所示。

图3 程序总体设计

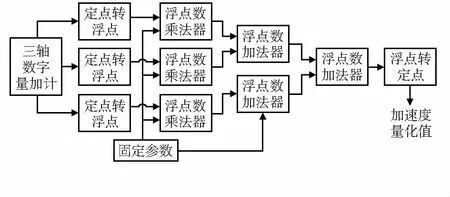

计算单轴加速度值的程序如图4所示,三轴电压数据通过定点浮点转换器转换为浮点数,接着通过浮点数乘法器与矩阵K相乘,将计算的结果和矩阵B通过浮点数加法器加在一起,通过浮点定点转化器转换为正整数输出。浮点数IP核的延时都为两个时钟的条件下,数据处理最快可以达到15个时钟,完全满足115 200波特率的时序要求。

图4 单轴加速度量化单元

综合考虑到资源、速度以及采用的控制芯片资源有限,所以本设计采用三级流水线,降低了资源的使用率减小了面积,将一个运行周期提高到57个时钟,资源使用率降低到了原来的1/3,仍然满足时序要求。

5 程序仿真与实验验证

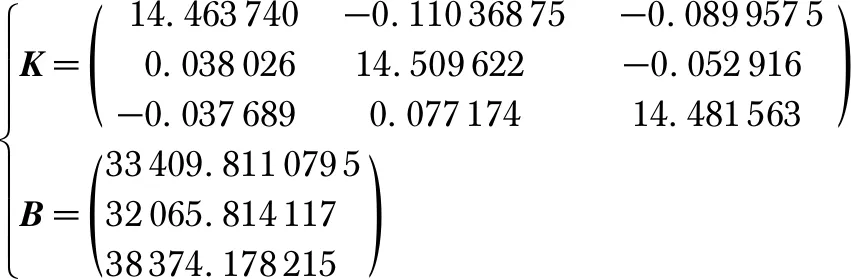

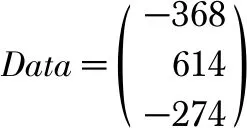

为验证程序设计的正确性,对所设计的程序进行功能仿真测试,仿真所采用的数据均为传感器的真实数据,通过式(1)与式(2)计算,将两次得到的数据进行对比,以此验证程序的正确性。程序仿真验证后为确保程序在最终系统上的运行正常,最后在三轴转台的位置模式下验证加速度传感器实际输出是否准确。用六位置法标定后得到标定系数矩阵A和零点电压矩阵VREF

(7)

根据式(4),可得到固定参数矩阵K和B

(8)

为验证程序,输入一组三轴加速度数据

(9)

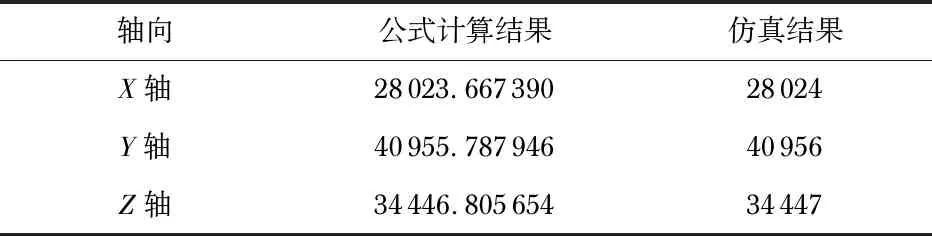

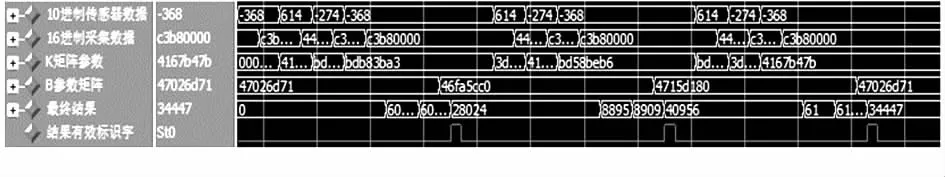

对以上数据进行仿真测试,仿真所用矩阵参数以及数据输入均为有效数据,仿真的结果如表4和图5所示,对公式计算的结果进行四舍五入,与仿真的数据进行比较证明结论正确。

表4 公式计算结果与仿真结果对比

图5 程序仿真

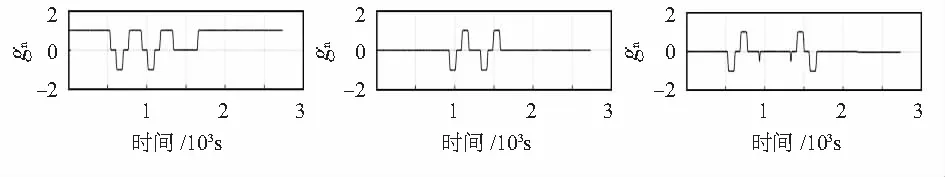

在程序仿真成功后,进行系统级调试,将系统装在三轴转台上,以位置模式转动,分别使系统处于-1,0,1gn来进行功能测试。将采集到的数据经处理后,得到的数据如图6所示。将接收到的数据分析和对比后,证实本次设计能够实现了三轴加计的数字量输出,且系统输出的数据准确无误。

图6 三轴加速度计输出

6 结 论

实践证明:本文所采用的设计将传感器的参数预先加入到系统中,使整个系统成为一个独立的模块,用户不需要考虑传感器的参数只需要关心传感器输出的加速度值,整个传感器的使用更加独立高效。经过实验验证,这种转换方式是一种有效的方法,并且可以灵活地配置数据的精度以及量化的范围,在工程实践中有着非常重大的意义。