一种基于JTAG的片内调试系统设计

2020-10-22姚霁

姚霁

摘 要: 为了给芯片设计提供一种高效方便的调试方法,提出一种基于JTAG的片内调试系统。该系统包括调试系统控制模块、断点产生模块和JTAG接口。JTAG接口实现调试指令的发送与接收;断点产生模块是调试系统硬件调试的逻辑单元;调试系统控制模块则实现断点设置、单步运行、内存调试等功能。不同的调试指令可根据不同的硬件结构自动完成其各自的处理流程,而且不同的工作模式之间可以自由切换。该片内调试系统表现出了高性能,便于操作的特点,已经通过了实际的芯片测试。

关键词: 片内调试系统; 系统设计; JTAG; 调试指令; 调试流程; 模式切换

中图分类号: TN911?34 文献标识码: A 文章编号: 1004?373X(2020)20?0031?03

Design of on?chip debugging system based on JTAG

YAO Ji

(Xian University of Posts and Telecommunications, Xian 710121, China)

Abstract: An on?chip debugging system based on JTAG is proposed to provide an efficient and convenient debugging method for the chip design. The system is mainly composed of the debugging mode control module, breakpoint generation module and JTAG interface. The JTAG interface is used to realize the sending and receiving of debugging commands, the breakpoint generation module is the logic unit for hardware debugging of the system, and the debugging system control module is used to realize the breakpoint setting, single step running, memory debugging and other functions. The different debugging commands can automatically complete their own processing flow according to different hardware structures, and different working modes can be freely switched. The on?chip debugging system shows its characteristics of high performance and easy operation, and has passed the actual chip testing.

Keywords: on?chip debugging system; system design; JTAG; debugging command; debugging process; mode switching

0 引 言

随着半导体电子技术的飞速发展,集成电路芯片的功能越来越复杂,集成度越来越高。在面对复杂SOC芯片设计时,芯片的调试手段不仅关系到芯片的质量,还直接影响到研发的效率和进度。因此在芯片仿真之外,提供高效、强大、方便、可靠的测试手段,已经成为芯片研发成败的关键。本文在基于8051控制器的芯片硬件设计基础上,提出并实现了一种基于JTAG接口的嵌入式片内调试系统(On?chip Debug System)[1]。该系统复用系统中8051控制器的JTAG接口和外部管脚不仅能避开CPU的访问,不占用CPU资源,同时提供了多种调试手段,能对控制器及存储器的内部状态进行监测,从而实现芯片的实时调试[2]。

1 基于JTAG的嵌入式片内调试系统

1.1 嵌入式片內调试系统结构

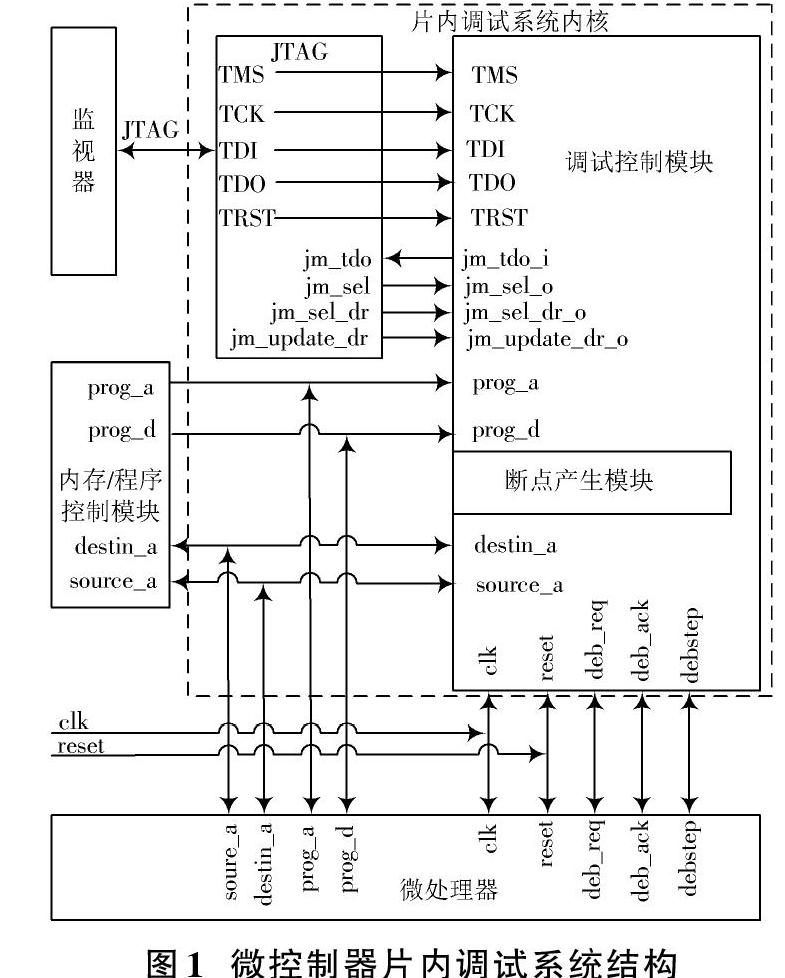

文中提出的嵌入式片内调试系统主要应用于面向基于8051微控制器的多IP模块集成的SoC芯片,主要包括JTAG接口和调试系统控制模块及断点产生模块三个部分。用户可以通过该调试复用系统的JTAG接口,完成调试指令的接收、发送、调试标志位的设置等交互信息的通信。而断点产生模块是属于调试系统的硬件逻辑部分,负责设置识别外部中断、硬件断点、软件断点等。调试控制模块则管理调试模式的进出、返回,识别指令信息并控制调试指令执行,处理硬件测试平台信息,从而实现对整个芯片的调试和监控。嵌入式片内调试系统的系统结构[3]如图1所示。

1.2 嵌入式片内调试系统工作原理

嵌入式片内调试系统是集成在微控制器芯片内部的专用调试模块,用户设置相应的调试寄存器来决定响应调试中断的优先级,并决定处理器是否直接进入调试状态。当满足调试条件进入调试状态后,用户进入调试系统,内嵌调试单元负责接收中断,并进行调试中断处理,然后通过JTAG接口向外部调试器发出信号,通知主机调试器,调试器通过内嵌的调试模块执行接收到的调试指令,监控芯片的运行、寄存器的状态以及实现存储器内容的直接读/写[4]。调试过程不但可以实现对处理器内核的监控、片内调试系统与各外围功能模块的数据交换,从而实现微控制器的实时调试,而且还可以方便地进行片内调试模式和正常模式的切换。

2 基于JTAG的嵌入式片上调试系统内核设计

片上调试系统内核是整个调试系统的核心部件,它通过总线与不同的功能接口与微控制器及外设通信。在结构和功能上包括JTAG接口单元、断点产生模块及调试控制单元三部分[5]。

2.1 JTAG接口

集成在芯片内的JTAG接口是外部调试器与内部调试系统之间的主要通信接口,根据嵌入式片内调试系统的需求,本文设计了增强的JTAG接口模块[6]。它采用标准的JTAG通信协议及端口,但在结构上增加了控制寄存器及控制单元进行数据传送控制,其结构原理如图2所示。用户可以设置控制寄存器的JEN位,进行JTAG工作模式的选择。在数据捕获之前,将来自片上调试系统的5个控制位(DBCON,DMODE,RRF,TRF, COMRST)分别写入寄存器16位DMSHR。该流程用来控制片上调试系统状态。数据传输寄存器DMTR同样也写入DMSHR准备传输数据,当数据传送信号激活后,JTAG模块的输入就会在时钟信号tck_i的上升沿被传送到寄存器DMSHR里面。从寄存器DMSHR出来的输出数据也会通过tdo_o输出到JTAG模块,并通过JTAG模块进行指令和数据处理。

在一个数据移入后,jm_update信号被激活,DMSHR中移入的数据信息被存储到各自的片上调试系统寄存器里面,同时DMSHR的数据也通过JTAG 接口送入到片上调试系统里进行处理。

2.2 断点产生模块

断点产生模块是片上调试系统硬件调试的逻辑单元。通过调试控制模块进入该模式后,基于芯片的内部存储器结构,片上调试系统利用断点产生模块产生硬件断点:指令断点和内存断点。在芯片的实际调试中,用户需要根据实际情况进行相应的断点设置操作。指令断点作用于系统处理器核的取指令阶段,物理上由多组比较寄存器组成。它是通过存储空间地址的设定来确定断点地址。芯片程序在取指令时,片内调试系统读入程序地址总线的指令地址,并与预设的程序断点地址进行比较,并判断预设的断点地址是否与程序总线传送的地址匹配,如果匹配则进入片内调试模式,反之,则程序继续运行。当用户在内存空间进行断点设置时,处理过程和指令断点类似,处理器核通过内部8位内存总线接口进行内存断点的读写,并在片内调试系统内部完成断点设置比较,如果匹配则触发片内调试系统,反之,处理器正常执行。用户在设置断点时,也可以通过外部调试软件进行断点设置,其原理与设置程序存储器断点原理相同,只是存储空间和内部总线接口不同。

2.3 调试系统控制模块

调试器的控制模块是调试系统的核心部件。片内调试系统的各个硬件操作,如调试模式进入、单步执行、存储器访问、断点设置等,都是由片内调试硬件模块的控制模块操作的。同时,调试系统的内核与处理器核及存储器的通信也都是由控制模块来实现的[7]。

2.3.1 调试模式的进出

当片内调试模式的触发事件发生时,调试系统向处理器发出中断请求int_req,然后处理器响应该请求,并反馈中断识别信号int_ack,标志着调试模式的进入,并进行压栈处理。当退出调试模式时,片内调试控制器置低中断请求信号,处理器响应该信号,执行出栈操作。片上调试系统还可以支持外部中断的产生。当外部管脚EXT上产生一个下降沿触发,由控制单元发送debug_ack信号到处理器后,芯片进入片上调试模式。

2.3.2 单步执行

单步执行是指控制单元通过握手信号向处理器申请单步调试,进行单步执行时,处理器每次执行当前指令后即进入片内调试模式。如果单步执行,片内调试模式控制寄存器将会设置控制寄存器DMTR,控制和标志单步的执行。单步执行的过程为每次单步执行完成2个SCLK以后,DebugReq被reset, 同时片上调试系统硬件系统再一次激活信号DebugReq。

2.3.3 片内访问控制

程序存储器以及内存访问控制都是控制单元通过地址读写总线prog_a和程序数据总线prog_d来对程序存储器进行数据读写以及对芯片的在线编程[8]。

3 片内调试系统的调试流程

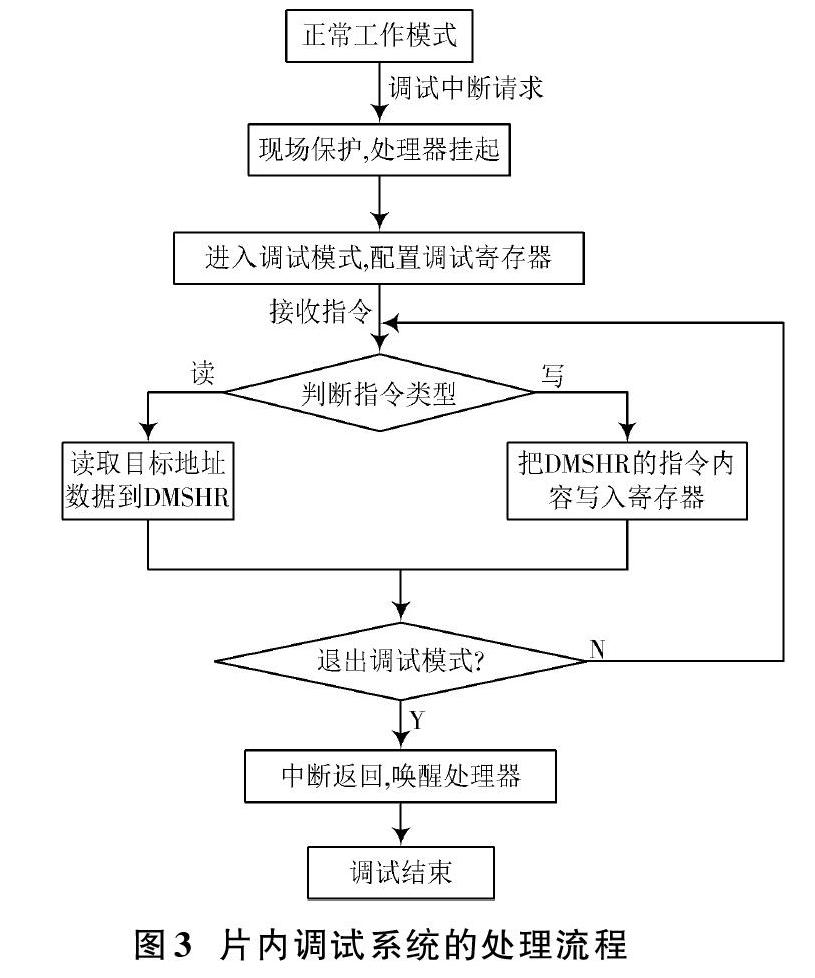

SoC系统中的微控制器可根据上电时特定的管脚配置,选择片内调试模式配置。当调试事件发生后,芯片启动调试系统,进入调试模式,处理器挂起,交出控制权。调试控制器发送调试指令,根据不同的指令进行不同的调试流程。调试完成后,处理器重新获得控制权,进入正常工作模式[9]。具体调试流程如图3所示。

4 结 论

随着SoC芯片开发复杂度的提高,传统的板级调试手段已不能满足芯片研发的调试需求,因此片内调试技术对SoC芯片的研发质量和周期至关重要。本文提出一种基于JTAG协议的片内调试系统的设计方案,可以实现断点设置、单步执行、寄存器/存储器内容读写以及在线编程、处理器核的现场配置等调试功能。本设计方案在实际的微控制器项目中成功地完成了芯片开发和调试,表现出了优异的性能。它利用通用的JTAG接口使得调试过程快速灵活,用户调试简单、方便。独特的内嵌式调试机制保证了高监控性,可以及时准确地查询设置芯片内部寄存器的状态,而且在调试时不占用芯片CPU资源,调试时间少,效率高[10]。

随着半导体技术的飞速发展,处理器提供片内的调试电路为复杂SoC芯片设计以及嵌入式系统开发提供的调试手段早已是大势所趋。本文提出的基于JTAG协议的片内调试系统方案为处理器芯片调试功能的研发提供了一个新的调试平台,为其应用开发提供了强有力的技术支持。

参考文献

[1] 虞致国,魏敬和.一种SoC片上调试与可测性的整合设计[J].电子与封装,2010,10(2):20?22.

[2] 何勇,王腾,王新安,等.一种低代价零开销SoC在线调试系统设计[J].微电子学与计算机,2014,31(3):89?93.

[3] 虞致国,魏敬和.一种基于JTAG的SoC片上调试系统的设计[J].微电子学与计算机,2009,26(5):5?8.

[4] 高瑛珂,王琪,李泉泉,等.一种基于JTAG接口的片上调试与性能分析方法[J].微电子学与计算机,2012,29(7):68?71.

[5] 常志恒,肖铁军,史顺波.基于JTAG的片上调试器与调试系统的设计实现[J].计算机工程与应用,2012,48(30):78?82.

[6] 张立强,宋玲,刘宝娟.JTAG并口下载设计[J].微处理机,2013,34(1):13?15.

[7] 荣蓉.基于SoC嵌入式片上系统应用研究[J].煤炭技术,2012,31(6):218?219.

[8] 娄冕,赵翠华,张洵穎,等.一种片内硬件调试支持单元设计[J].现代电子技术,2010,33(24):18?22.

[9] 王琪,高瑛珂,华斯亮,等.可复用微处理器片上调试功能的设计与实现[J].计算机辅助设计与图形学学报,2012,24(10):1369?1374.

[10] 陈芳芳,周克宁.面向电子控制器的片上可调试性结构设计[J].电子器件,2018,41(3):708?712.