子阵级数字化接收阵列性能分析

2020-10-09石国超王璇周子巍

石国超 王璇 周子巍

摘要:本文主要以模拟波束合成和数字波束合成的划分为变量,分析了子阵级数字化相控阵的接收灵敏度及动态范围特性,同时提出了能够将经典接收链路性能计算扩展到接收阵列使用的方法。最终实例分析了数字化程度对于接收系统性能的影响。

关键词:相控阵;数字接收机;噪声系数;动态范围

中图分类号:TP309 文献标识码:A 文章编号:1007-9416(2020)08-0073-03

0 引言

Salvador H.Talisa等学者将相控阵架构分为模拟无源(APPA,Analog Passive Phased Arrays)、模拟有源(AAPA,Analog Active Phased Arrays)、子阵级数字化(SLDA,subarray-level digital arrays)以及單元级数字化(ELDA,element-level digital arrays)四类[1]。目前相控阵体制正逐步从传统的APPA向ELDA进化。但受到成本、功耗、集成等限制,ELDA的工程实现还很困难[2],因此SLDA依然是当前工程实现上的主流架构。对阵列接收性能的分析有很多详尽的文献[3-4],但这些文献并没有重点关注上述不同架构的性能差异,Thomas M.Comberiate等学者初步比较了AAPA和ELDA的动态性能[5],本文在此基础上给出了更详细的分析,并提供了将传统接收链路分析扩展到SLDA阵列应用的思路。

1 子阵级数字化接收阵列架构

由于基于PIN二极管和铁氧体器件进行移相的APPA目前已经很少使用,同时AAPA与SLDA可认为是SLDA的特殊形式,因此本文主要针对SLDA架构进行接收性能的分析。

在图1所示的SLDA架构中,每个天线单元连接独立的低噪声放大器LNA和幅相控制器件VM,经过幅相加权后进行子阵级的MA个通道的模拟波束合成,MD个子阵输出的模拟波束通过相应的MD个数字接收机DR进行数字化,最后在数字域进行二级数字波束合成。

假定整个阵列有M个天线单元(M=MA×MD),当MD=1,MA=M时,SLDA架构变为AAPA架构;而当MA=1,MD= M,SLDA架构变为ELDA架构(为保证链路器件不发生变化,后面的分析中ELDA架构并没有去掉VM的损耗,实际ELDA阵列不需要VM器件)。在后面的性能分析中,将以MA为变量,分析在相同LNA、VM和DR等器件的条件下,从AAPA到SLDA再到ELDA的灵敏度及动态特性变化。

2 接收阵列链路级联模型

与图1对应的接收链路级联模型,以及各器件参数见图2所示,采用小写字母代表倍数值,而采用大写字母表示分贝值。各器件主要考虑增益(插损)、噪声系数、输出P-1以及输入三阶截点值。

SLDA与单通道接收链路的区别在于对合成级MA和MD的处理,对于相干信号按式(1)合成,链路增益、输出P-1以及输入三阶截点值可按此式级联。链路噪声模按式(2)合成[2]。sin,n表示第n路的输入信号,共N路合成后得到合成输出信号sout;nin,n表示第n路的输入噪声,共N路合成后得到合成输出噪声nout。假定各通道器件具有相同的性能参数,也就是所有的sin,n相同为sin,所有的nin,n相同为nin,那么(1)式退化为,(2)式退化为,两式相除就得到阵列合成能够实现的N倍的信噪比增益。

由于篇幅受限,除了上述假设外,下述分析中还做了如下简化:(1)不考虑阵列扫描和幅度加权,于是VM的幅相加权wVM可用插入损耗lVM描述;(2)不考虑阵列有源反射系数对fLNA的影响;(3)假定天线输出端口的噪声tA在合成时不相干;(4)将数字接收机简单的使用增益、噪声系数、输出P-1以及输入三阶截点值描述,未考虑采样器各参数的影响。

3 接收阵列噪声与动态性能

接收机灵敏度与动态求解过程如图3所示。SLDA阵列与接收机的主要不同在于从模块性能到链路级联过程中对于波束合成的处理,因此下面主要讨论这一过程。

3.1 噪声系统与灵敏度电平

图2所示从sin端口到sout端口增益为链路级联增益再加上阵列合成增益,如(3)式

噪声为(4)式,其中各级器件的等效噪声温度可由求得。

系统计算噪声系数时,输入噪声功率按,并且不考虑(4)式中第一项即天线引入的噪温。按文献[3]中的推导,阵列输入的总信号能量为,由噪声系数的定义可得(5)式。(5)式表明,将SLDA阵列中的模拟合成网络等效成损耗器件,即可采用链路噪声系数级联公式对SLDA进行估算。而将是MA的函数,也就是说模拟波束合成与数字波束合成的划分将通过影响阵列的噪声性能。

利用(5)式,即可通过接收灵敏度公式计算特定带宽下、特定解调信噪比条件下,等效到阵列LNA输入端口接收灵敏度电平。

3.2 单音动态与双音动态

图2所示链路LNA输入端口的输入P-1可由下式求得。

根据文献[4]中对阵列合成TOI的分析,图2所示链路LNA输入端口的TOI可由式(7)计算。假定模拟合路器的输入三阶截点无穷大,则(7)式第三项可认为对系统输入三阶截点无贡献。

通过输入P-1与灵敏度电平可求得单音动态,而通过输入三阶截点、灵敏度电平和系统链路增益(模拟部分),又可求得双音动态范围。

4 实例与对比分析

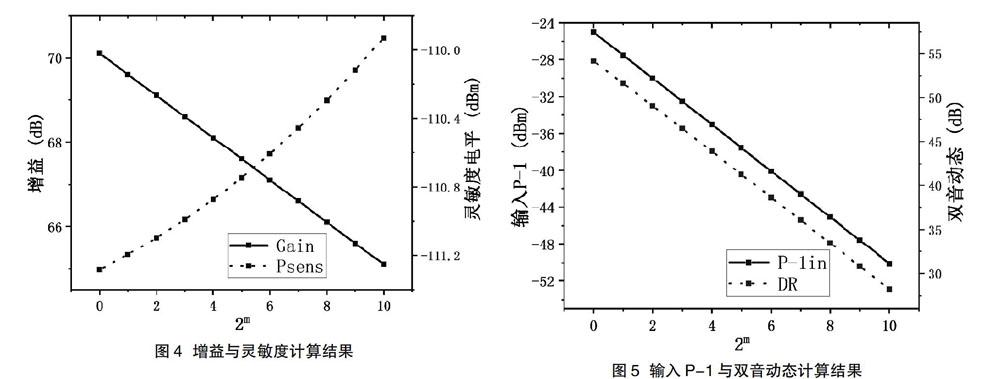

假定阵列M=210共1024个天线单元,模拟波束合成子阵通道数量为M=2m,m取值从0~10,当m=0时,阵列为ELDA,而当m=10时,阵列为AAPA。每级模拟波束合成所用合路器的插损为0.5dB,则lMA为0.5×m(dB)。各级增益分别取值为,,;各级噪声系数分别取值为,;输出P-1分别为,,;输出三阶截点值分别为,,。

通过链路计算,得到增益与灵敏度曲线如图4所示。如图所示随着SLDA的数字化程度提高(从右到左),阵列增益(Gain)和灵敏度电平(Psens)均会提高。造成这种差异的主要原因在于模拟波束合成引入的器件损耗lMA。

图5所示为衡量阵列动态特性的输入P-1与双音动态范围。如图所示,随着SLDA的数字化程度提高(从右到左),阵列输入P-1和双音动态均会提高。造成这种变化的主要原因在于模拟波束合成提高了前級器件的输出能力和增益,从而压缩系统能实现的动态范围。

上述实例采用了常规的链路器件性能参数,目的是分析阵列数字化程度提升对接收链路性能产生的影响。值得注意的是,采用经典的接收链路级联公式对接收阵列进行噪声系数和输入三阶截点分析时,模拟波束合成网络可以简单的等效为增益为(倍数值),输入P-1和输入三阶截点无限大的级联模块,进而通过图2所示的链路模型进行阵列端射情况下的指标核算。

5 结论

本文主要以模拟波束合成和数字波束合成的划分为变量,分析了子阵级数字化相控阵SLDA的接收灵敏度及动态范围特性,同时提出了能够将经典接收链路性能计算扩展到接收阵列使用的方法。实例分析结果表明,对于常规的链路增益分配并在相同链路模块性能的前提下,提高阵列数字化程度,将同时提升系统的灵敏度和动态性能。由于篇幅限制,本文加入了一系列假设来简化分析过程,更全面的分析将在完整版论文中呈现。

参考文献

[1] S.H.Talisa,K.W.O'Haver,T.M.Comberiate,etc.Benefits of Digital Phased Array Radars[J].Proceedings of the IEEE,2016,104(3):530-543.

[2] H.Bo Marr.Fundamental Energy Limits of Digital Phased Arrays[J].IEEE Transactions on Circuits and Systems,2019,66(7):2775-2783.

[3] J.J.Lee.G/T and noise figure of active array antennas[J].IEEE Transactions on Antennas and Propagation,1993,41(2):241-244.

[4] R.V.Gatti,M.Dionigi,R.Sorrentino. Computation of gain, noise figure,and third-order intercept of active array antennas[J].IEEE Transactions on Antennas and Propagation,2004,52(11):3139-3143.

[5] T.M.Comberiate,S.H.Talisa,K.W.O'Haver,A comparison of in-band linearity between element-digital arrays and active electronically-steered arrays[C].2016 IEEE International Symposium on Phased Array Systems and Technology(PAST),Waltham, MA,2016:1-4.