FPGA多重配置在LED显示控制系统中的应用

2020-05-06程宏斌郑喜凤

曹 慧,程宏斌,2*,汪 洋,2,郑喜凤,2

(1. 长春希达电子技术有限公司 吉林 长春 130103;2. 中国科学院 长春光学精密机械与物理研究所 吉林 长春 130033)

1 引 言

常规LED显示控制系统主要由上位机、发送卡和接收卡组成,通过网络链路,实现LED显示屏的显示和控制。发送卡接收视频和控制信号,并将数据打包传输接收卡。接收卡截取自己需要的数据完成灰度调制或控制响应,并通过千兆网将数据串行转发给下一张接收卡[1-3]。

在指挥、监控中心等工程项目中,LED显示屏要求(7×24)h不间断运行,因此确保控制系统程序升级正确越发重要。系统通过网络传输更新发送卡、接收卡外置Flash存储的程序文件,在过程中存在因干扰产生错误数据或遇到掉电、误擦除等破坏程序文件完整性的情况,致使现场可编程门阵列(Field Programmable Gate Array,FPGA)[4-12]不能再次调用,人工逐一板卡烧录程序费时费力,造成重大显示故障。通过Xilinx Spartan-6 FPGA的MultiBoot特性,完成FPGA多重配置设计,在Flash某一固定区域存储备用程序,当FPGA更新程序出错时,调用备用程序保障常规显示和网络链路功能,随后在线更新程序,提高控制系统的容错率。

2 多重配置原理

Spartan-6 FPGA在通电时从外部Flash加载存储的项目程序文件(mcs),完成FPGA的配置后执行系统功能。mcs文件一般只包含一个比特流配置文件,但也允许有多个。Spartan-6 FPGA具有MultiBoot逻辑配置模块,来实现MultiBoot和Fallback操作。MultiBoot操作可以有选择地从Flash的多个比特流文件中加载其中的一个,通过ICAP设置寄存器并触发IPROG命令,在系统不重复上电情况下对FPGA重新配置[4-6],实现不同的功能。Fallback操作是在切换加载比特流文件过程中出错时,用预存的安全比特流文件替代并进行FPGA的重新配置。

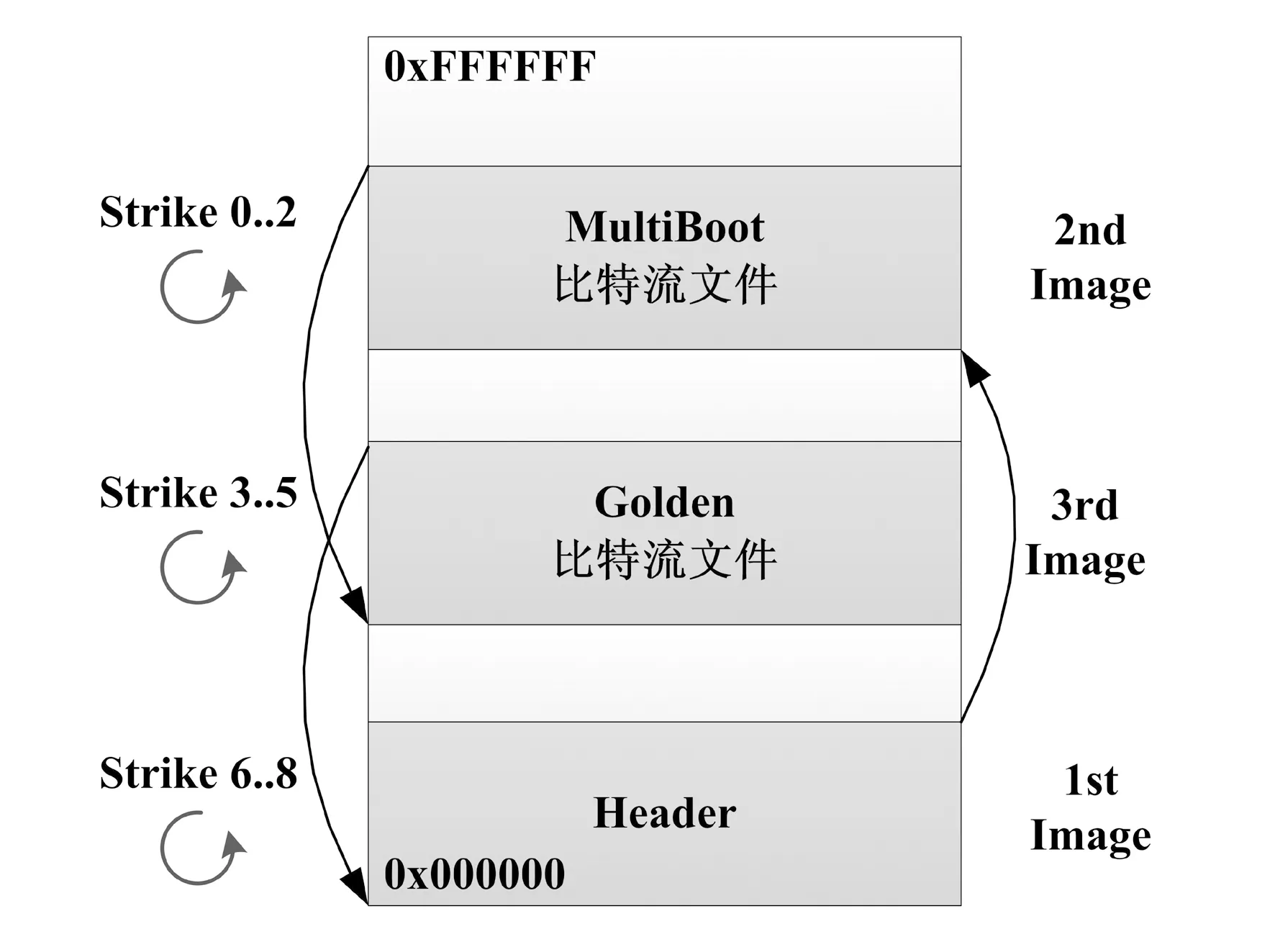

MultiBoot逻辑配置流程中有Header、MultiBoot和Golden 3个比特流配置文件,此时外部Flash存储器中的比特流文件组织模式及FPGA配置流程如图1所示。

图1 MultiBoot逻辑配置流程Fig.1 MultiBoot logic configuration process

Header配置文件包含同步字、MultiBoot和Golden配置文件在Flash存储的起始地址等信息[7]。系统上电时,FPGA从0地址加载Header配置文件,根据存储的地址跳转并加载MultiBoot配置,这是满足用户使用的系统常规程序。Golden配置文件为备用的安全程序,当加载MultiBoot配置出错时,触发Fallback操作,加载该安全程序配置FPGA。

如图1所示,Header、MultiBoot和Golden(Fallback)配置文件在加载过程中出错时,根据相应寄存器内设置的起始地址值FPGA会重新加载3次,加载次数的计数器名称为Strike。若Strike的计数值为6,则从0地址开始,FPGA执行Header→MultiBoot→Golden (Fallback)→Header的循环加载。若期间MultiBoot或Golden(Fallback)配置文件加载成功,则停止循环。每次循环Strike值加1,最多3次,Strike值为9则停止所有配置加载。

Fallback操作一旦被触发且加载Golden配置成功,只有重启系统或使用IPROG命令才能实现重新加载其他FPGA配置文件。MultiBoot特性提高了器件利用率及系统安全性、降低了复杂系统的成本。

3 系统应用设计

LED显示系统方案设计如图2所示,增加MultiBoot控制模块,采用状态机编码,按照指令流程通过Xilinx内置的ICAP核向配置文件发送IPROG命令,热启动调用Flash中存储的备用程序,实现对FPGA重新配置。

图2 系统方案设计Fig.2 System scheme design

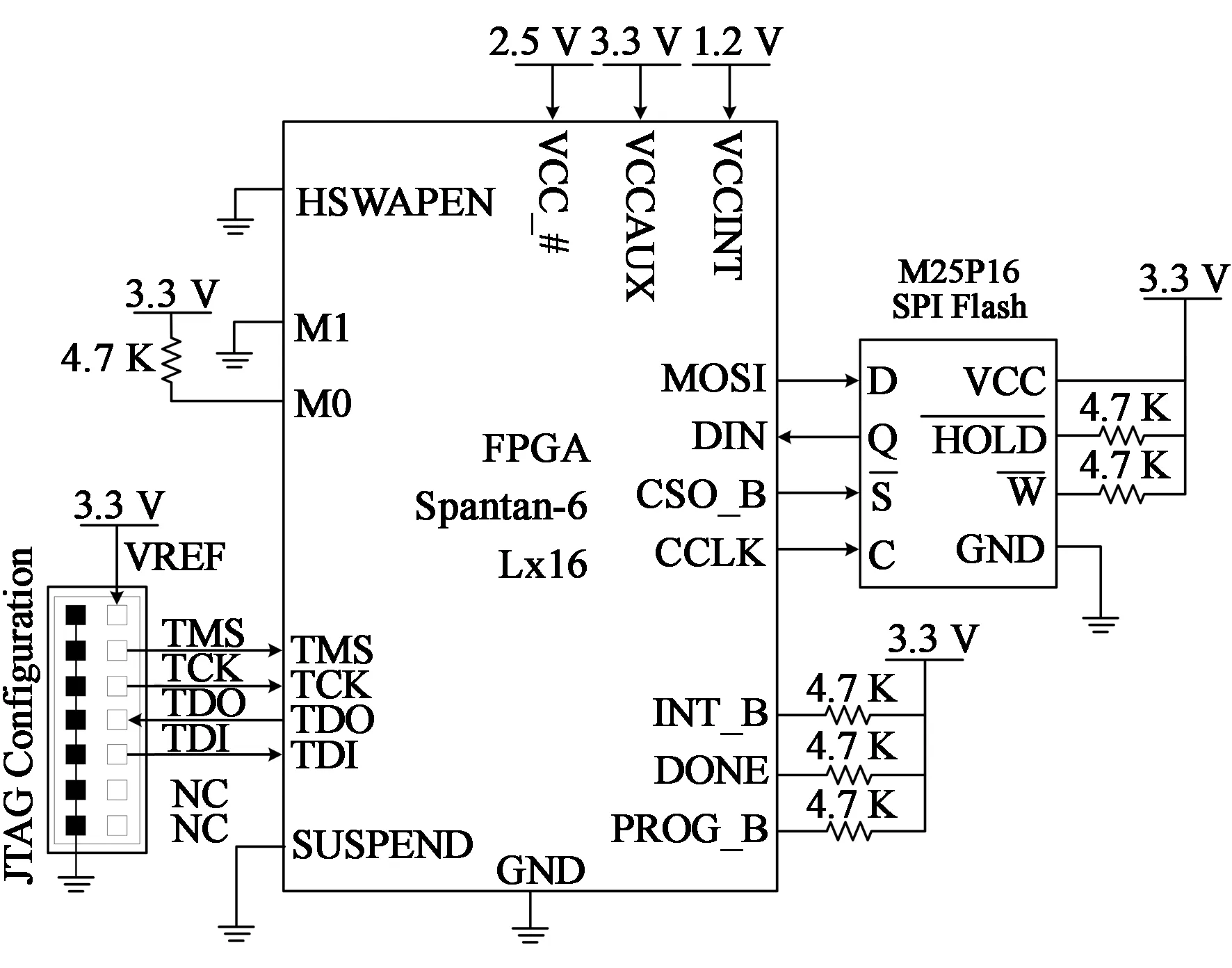

3.1 硬件设计

采用FPGA型号为Xilinx Spartan-6 Lx16、Flash型号M25P16,FPGA与SPI Flash物理连接的硬件电路如图3所示,数据宽度为×1 SPI配置的方式,M[1∶0] = 2′b01[8-9]。

图3 配置接口硬件电路Fig.3 Configuration interface hardware circuit

LED显示控制系统针对不同的显示屏需要进行相匹配的显示参数设置,在SPI Flash内采用显示参数设置与程序运行功能相独立地址存储,系统上电时加载程序比特流文件和显示参数设置文件,完成FPGA配置后实现不同显示屏的正常显示。

发送卡、接收卡的Flash存储区分为程序文件区和设置文件区。程序文件区保存实现各自功能的程序比特流数据;发送卡设置文件主要包含视频信号截取、屏幕带载分辨率、数据分包编码信息等;接收卡设置文件主要包含单卡带载分辨率、级联编码、显示灰度和刷新率、Gamma表、校正系数表等。

SPI Flash的容量选择与系统设计的加载模式和FPGA芯片的型号有关。在发送、接收端采用相同的主备两种FPGA配置加载设计方案,SPI Flash内存储Header、主程序MultiBoot、备用程序Golden比特流文件和2个程序附属显示设置文件(Config.hex)。所用型号为M25P16,16 Mbit(0x000000-0x1FFFFF)容量的Flash详细的存储空间如表1所示。

表1 Flash存储空间Tab.1 Flash storage space

3.2 软件设计

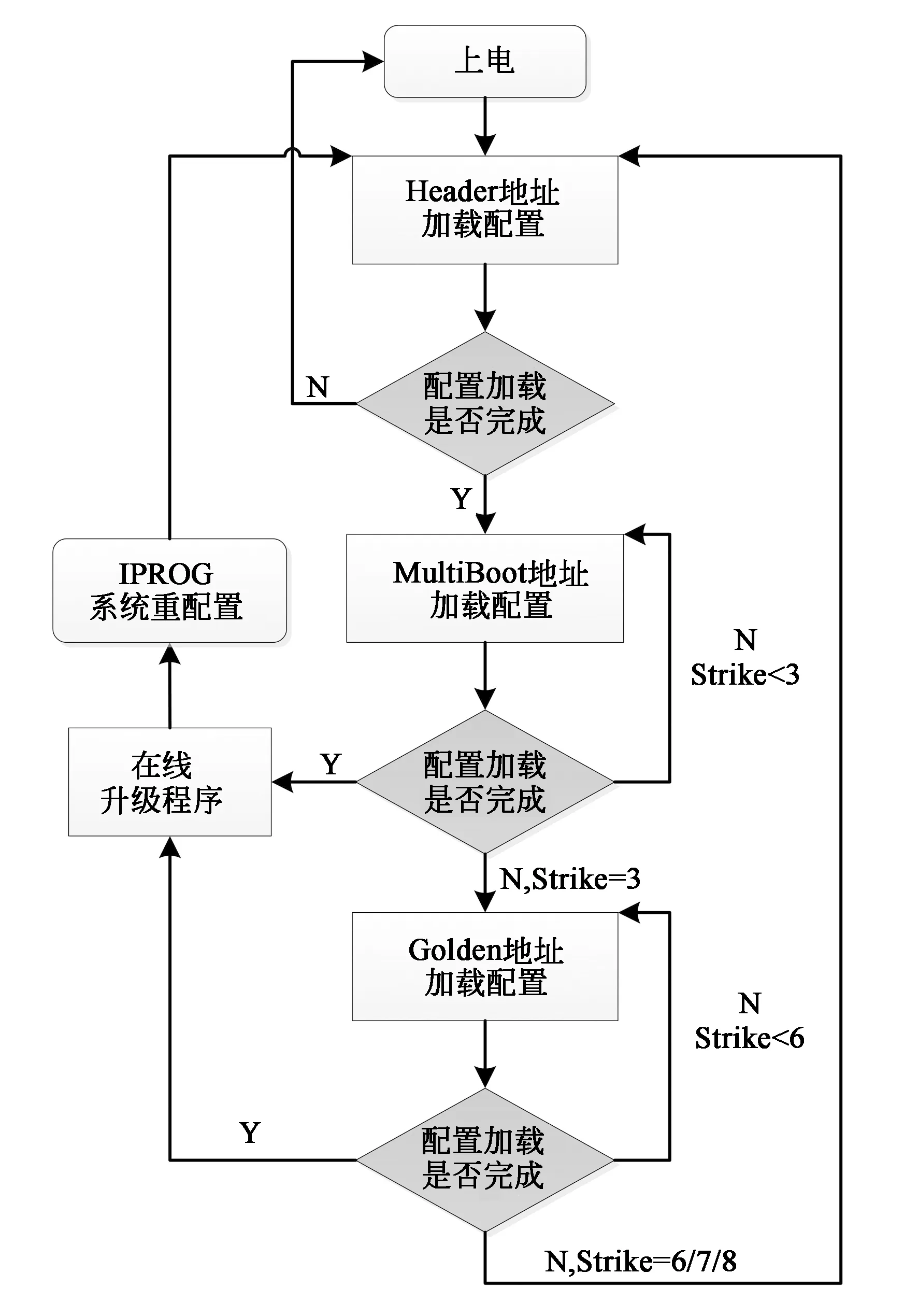

软件设计主要分为两个部分:第一部分是在FPGA上开发的应用模块。实现系统发送卡、接收卡各自的功能,同时也为配置重载模块提供时钟信号和触发信号,本文采用在线 Flash程序写入完成后输出的标识信号作为触发信号。第二部分是FPGA配置重载模块。包括Header文件编写、MultiBoot和Golden程序文件中例化ICAP核,满足触发条件后,发送IPROG命令,实现FPGA重新配置。程序备份启动及升级流程如图4所示。

图4 程序运行流程图Fig.4 Program operation flowchart

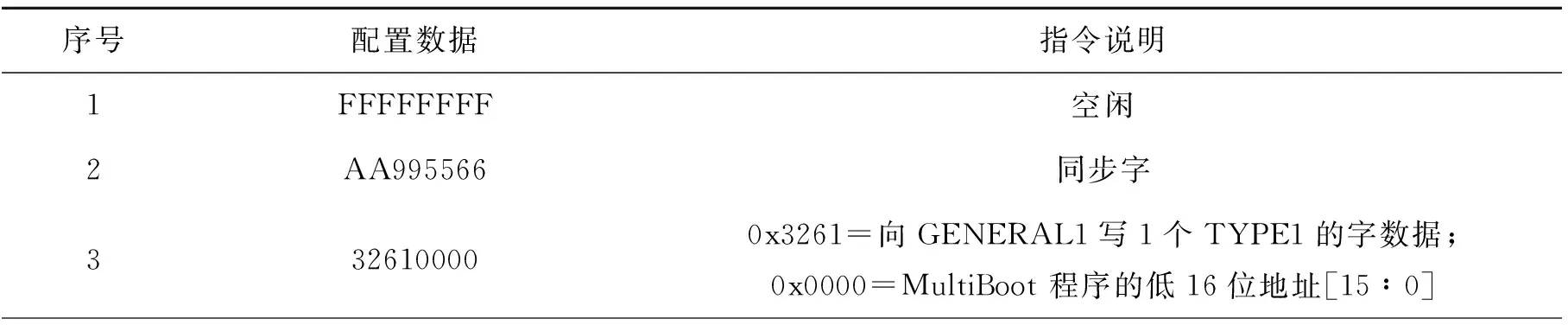

根据程序运行流程,Header配置文件作为启动引导作用,参照Xilinx Spartan-6指令对内部相关寄存器的规则[7](如表2所示),逐条编译指令数据形成Header配置文件并保存为HEX形式,图5为向内部寄存器GENERAL2写入指令数据的详解示例。

MultiBoot和Golden程序功能完全相同,需要注意的是:Golden备用程序内对应上位机程序升级指令的Flash擦除、写入的偏移地址为MultiBoot主程序地址,且各程序在SPI Flash起始地址需要与Header程序文件内地址设置值对应。在主备程序的MultiBoot控制模块中同时例化ICAP核, Xilinx的编译平台ISE中调用ICAP原语路径为Edit→LanguageTemplates,Verilog→Device Primitive Instantiation→Spartan-6→Config/BSCAN Components→Internal Configuration Access Port(ICAP_SPARTAN6),调用接口如下:

ICAP_SPARTAN6_inst (

.BUSY(BUSY), // Busy/Ready output

.O(O), // 16Bit Configuartion data output

.CE(CE), // ICAP Enable input(Active-Low)

.CLK(CLK), // Clock input

.I(I), // 16Bit Configuration data input

.WRITE(WRITE) // Read/Write control input

);

表2 Header配置文件内指令Tab.2 Header configuration directive definition

续 表

图5 指令数据详解示例Fig.5 Detailed examples of command data

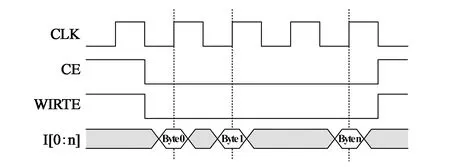

在使用该接口时,通过如图2所示的MultiBoot控制模块中状态机只对CE、CLK、I、WRITE 4个信号不断赋值来发送指令数据,不用关注BUSY、O的值[7]。ICAP写数据的指令时序图如图6所示。

图6 ICAP写数据指令时序图(I总线宽度为16 bit)Fig.6 ICAP write data instruction timing chart (I bus width is 16 bit)

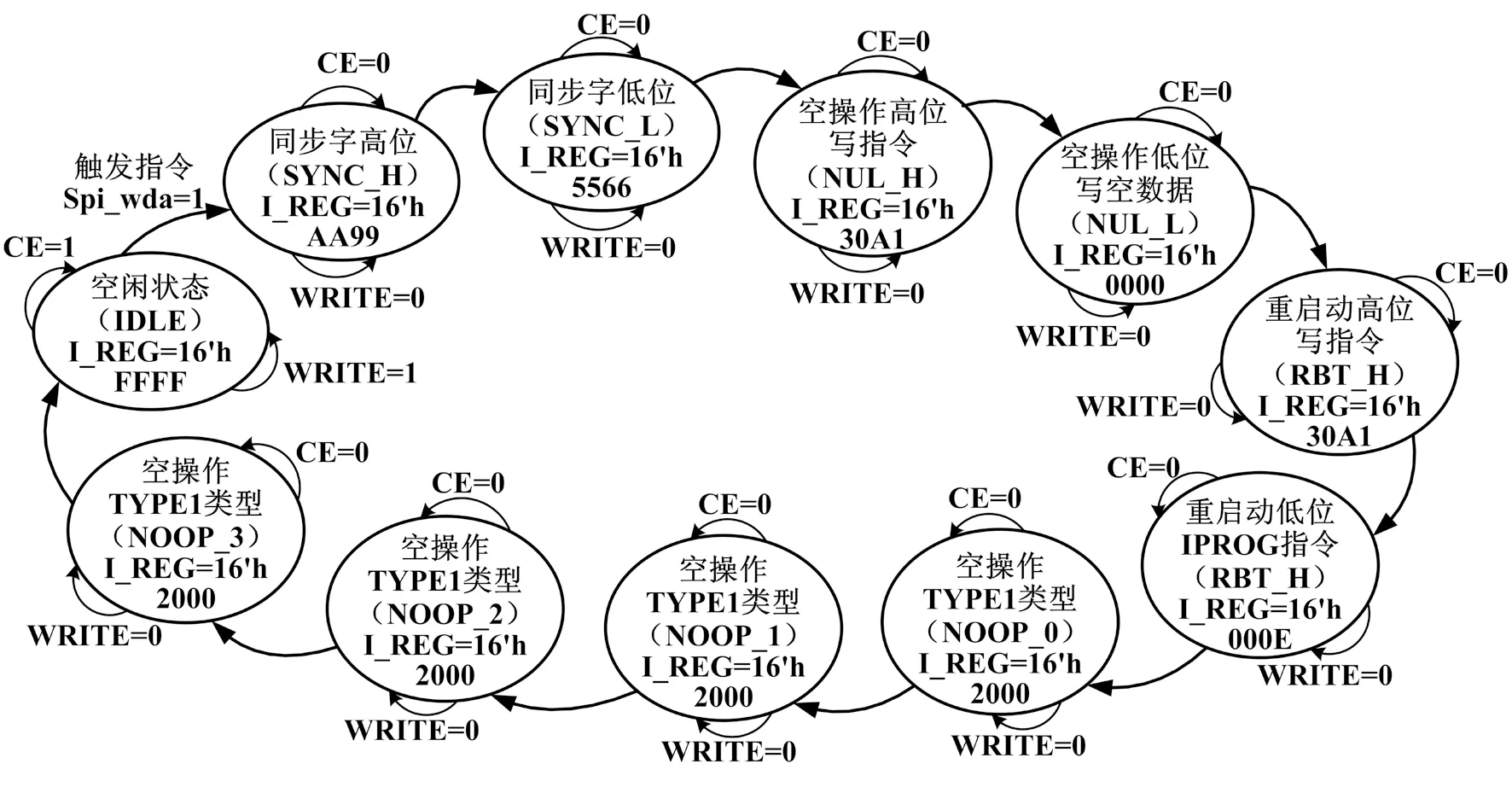

按照Xilinx Spartan-6指令对内部相关寄存器的规则,通过状态机完成表2中序号1→2→8→11→12→13的6个指令ICAP赋值,生成IPROG指令。ICAP_SPARTAN6数据总线宽度为16 bit,需要把引用的6个32 bit指令数据依次拆分为16 bit数据,以主备程序内Flash写入完成标识Spi_wda=1为触发信号,实现主备程序在线更新后按照运行流程自动重启对FPGA重新配置。写IPROG指令状态机如图7所示。

图7 写IPROG指令状态机Fig.7 Write IPROG instruction state machine

在状态机发送IPROG指令数据到ICAP核的过程中,需要先将16 bit位宽度数据分为高低各8 bit位宽字,在每8 bit位宽字内进行一次位转换(Bit Swapping)操作,确保ICAP_SPARTAN6核接收到位转换后的正确指令。位转换操作参照如下Verilog语句:

wire [15∶0] I; ∥进行Swap之后的有效数据

reg [15∶0] I_REG; ∥进行Swap前的I寄存数据

assign I = {I_REG[8], I_REG[9], I_REG[10], I_REG[11], I_REG[12], I_REG[13], I_REG[14], I_REG[15], I_REG[0], I_REG[1], I_REG[2], I_REG[3], I_REG[4], I_REG[5], I_REG[6], I_REG[7]}; ∥Flash主SPI模式下,数据需要按照每8 bit进行一次Swap操作(即每个字8个Bit数据进行高低位互换)。

同理,按照上述方法,增加外部触发信号,参照表2中所有指令数据,增加、修改图8状态机流程,则可以在MultiBoot控制模块中根据内部触发、外部触发信号输出给ICAP核不同数据,实现系统FPGA被动和主动两种不同的热启动重新配置方式。

4 生成固化文件

Xilinx Spartan-6系列的FPGA需要将后缀名为mcs的内存镜像文件固化到外部配置存储器中,上电后FPGA自动加载并完成配置。本文的mcs文件包含3个比特流文件和2个HEX文件,在整合到mcs文件的过程中,需要指定每个比特流、HEX文件在Flash中存放的物理地址,且必须与系统程序设计内有关Flash擦除、写入、读取等指令设置的起始地址相同,这样FPGA才能根据地址找到对应的程序和数据。

采用Xilinx ISE平台完成主备两个程序的工程项目文件设计后,通过软件的Generate Programming File生成主程序MultiBoot.bit和备程序Golden.bit。把相关文件放在同一目录下,使用ISE平台内的命令行窗口ISE Design Suite 32/64 Bit Command Prompt工具[10],按照以下步骤完成Flash存储芯片中初始可烧录的内存镜像(mcs)文件。

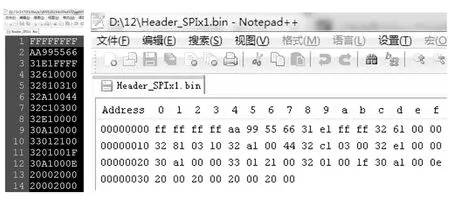

(1)promgen -p bin -r Header_SPIx1.hex -o Header_SPIx1.bin。如图8所示,把编写后的Header配置文件进行格式转换。

图8 Header配置文件格式转换Fig.8 Header configuration file format conversion

(2)promgen -w -p mcs -spi -s 2048 -data file up 000000 Header_SPIx1.bin -u 000044 Golden.bit -data file up 080000 Config.hex -u 100000 MultiBoot.bit -data file up 180000 Config.hex -o D:/H_M_G.mcs。

命令中各参数说明:

-spi:生成的mcs文件要固化到SPI Flash中;

-p mcs:生成文件的格式是mcs格式;

-s 2048:定义外部存储器的容量,2 048 kbytes×8/1 024=16 Mbit;

-data_file up 000000 Header_SPIx1.bin:名字为Header_SPIx1的BIN文件在Flash的起始地址为0x0;

-u 000044Golden.bit:名字为Golden的比特率文件在Flash的起始地址为0x44;

-u 100000MultiBoot.bit:名字为MultiBoot的比特率文件在Flash的起始地址为0x100000;

-data_file up 080000 Config.hex:名字为Config的HEX文件在Flash的起始地址为0x80000;

-data_file up 180000 Config.hex:名字为Config的HEX文件在Flash的起始地址为0x180000;

-o D∶/H_M_G.mcs:合成后的文件名和保存的目录。

合并完成mcs文件后,通过ISE设计平台中IMPACT软件将mcs文件固化到SPI Flash中。

5 测试分析与结果

通过ISE平台中集成的Simulation软件对设计进行仿真,通过添加Test Bench,模拟激励信号为升级程序写完Flash的标识信号Spi_wda,对MultiBoot控制模块进行仿真。图9是Flash重新加载时对ICAP核输入信号的仿真结果,可以看到,状态机成功生成了IPROG命令,并将位转换后的数据发送给ICAP模块。

图9 ICAP_SPARTAN6 IPROG命令仿真Fig.9 ICAP_SPARTAN6 IPROG command simulation

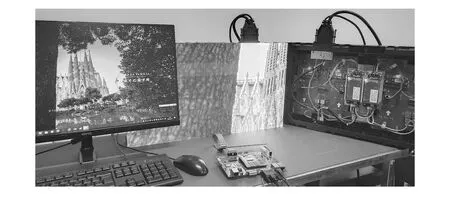

如图10所示,本设计通过LED显示平台进行主备升级程序的测试。测试过程及结果如下:

升级程序格式转换为HEX文件,由上位机软件通过网络传输升级指令和程序数据,分别发送给LED控制系统的发送卡、接收卡。通过修改程序HEX文件内数据和在上位机传输数据过程中拔掉网线、掉电,模拟升级过程中出现的突发情况,对发送卡、接收卡进行独立的测试。通过LED显示屏能否正常显示图像和系统指示灯状态观测FPGA是否正确加载配置。

图10 LED显示平台(软件、控制系统、显示屏)Fig.10 LED display platform (software, control system, display)

系统主备程序的显示功能一致,显示配置文件一致,主程序工作状态指示灯闪烁频率是备程序的2倍。在系统主程序正常工作时,模拟主程序升级故障,观测到板卡自动重启后系统指示灯从高频变为低频闪烁,LED显示屏显示正常,确认板卡备程序自动启用;此时正常进行程序升级,观测到板卡自动重启后系统指示灯由低频变为高频闪烁,LED显示屏显示正常,确认板卡主程序升级成功并自动启用;当备程序已经启用,模拟升级故障时,观测到板卡自动重启后系统指示灯维持低频闪烁状态,LED显示屏显示正常,确认板卡主程序升级失败,自动保持启用备程序。

6 结 论

本文LED显示控制系统的发送卡、接收卡程序采用主备程序热启动设计,在LED显示屏使用过程中极大地保障了系统在线升级的安全性和时效性。同时,显示程序文件与显示配置文件分区存储、灵活调用,通过上位机软件对Flash擦除、写入显示配置时,既满足不同LED显示屏需要灵活配置,又规避了对显示程序直接操作的风险。在Xilinx Spartan-6 FPGA系统设计中编写状态机调用ICAP核,通过内部、外部触发信号可以控制FPGA重新配置。该设计方法灵活方便,易于操作,可分时复用提高编程资源的利用率和系统稳定性,在工程应用中有很高的应用价值。