WiFi芯片的高速SDIO接口设计与验证

2020-03-23刘衡祁

刘衡祁

摘 要:近年来,随着互联网技术的发展,WiFi技术具有较强的稳定性,而且具备数据传输速度快、功能消耗较低等优点,目前在无线通信中已经具有十分重要的作用。随着时代发展进步,对WiFi芯片的要求越来越高,对研发者来说,快速高效拓展WiFi芯片外部功能是当前面临的主要问题。文章提出外部拓展接口,即SDIO接口,可在WiFi芯片架构中集成,能够为该芯片提供快速信息传输接口,阐述了该芯片总体架构,分析了SDIO Host仿真模型搭建仿真平台,能够完成相應的仿真验证,最后通过芯片测试表明该SDIO接口不同的子功能,设计合理,具有较强的可操作性。

关键词:WiFi芯片;高速;安全数字输入输出卡;接口;设计;验证

近年来,随着深亚微米技术的发展,集成电路芯片的功能越来越丰富,芯片是IC的重要核心原件,一个系统芯片可集成多种功能模块,包括CPU储存器、模拟单元等,该技术可将原有多芯片实现的功能集成到同一芯片,提高系统集成度、降低研发成本、提高芯片应用性。在当前电子产品逐渐推陈出新的过程中,为满足人们对产品的需求,市场倾向于接口丰富且拓展功能性强的芯片,在芯片中集成多种可通用接口,不仅可快速突破功能要求和成本,同时也能为芯片升级、功能拓展提供帮助。目前传输接口存在多种样式,本研究主要以安全数字输入输出卡(Secure Digital Input and Output,SDIO)接口作为WiFi信息高效传输接口进行阐述。

1 WiFi芯片

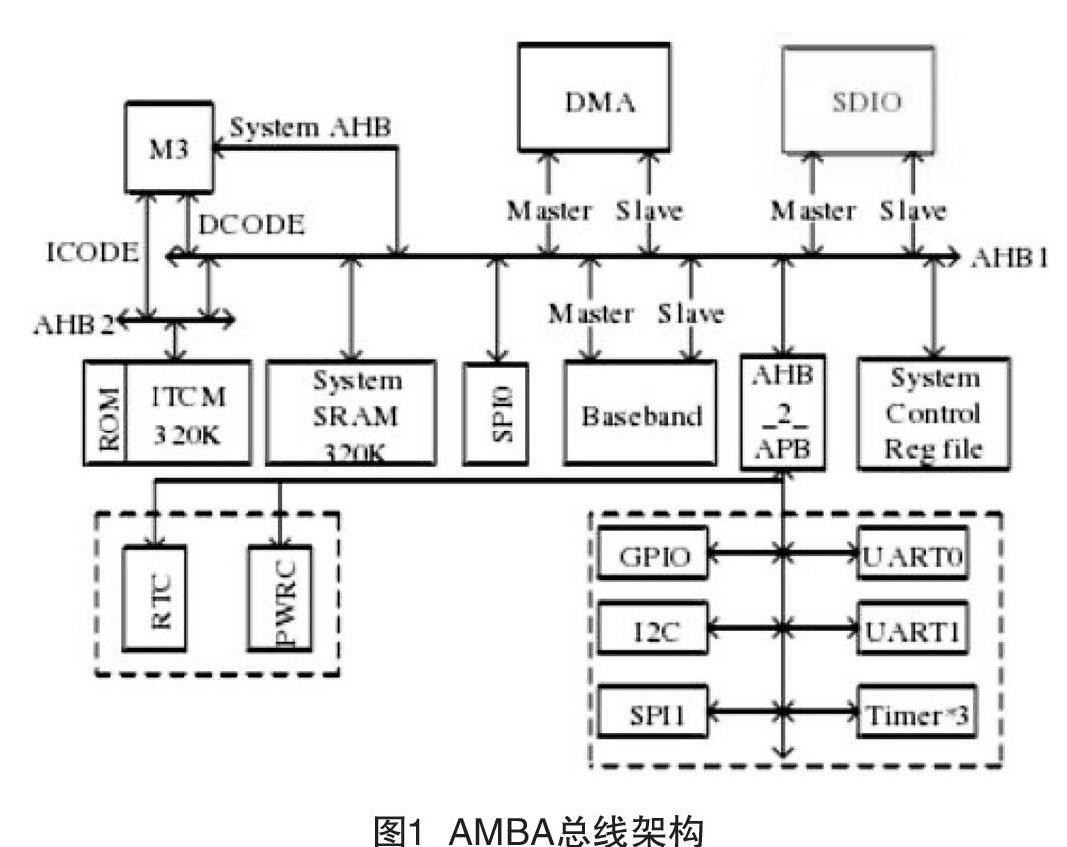

WiFi芯片架构是目前无线领域传输速度较快的产品,笔者研究的WiFi芯片是基于802.11n标准协议,可实现320 Mbps的传输速度,在芯片架构上选择AMBA总线架构,具体结构如图1所示。

该总线是一种多层总线结构,可定义多种功能总线,其中,系统总线(Advanced High performance Bus,AHB)可解决高性能的设计需求。AHB是外围总线,实现高带宽总线,为低带宽设备间提供信息桥梁,具有结构简单、功能消耗低等特点。该芯片采用一层外围总线(Advanced Peripheral Bus,APB)和双层AHB共同构成芯片相互连接的系统,其中AHB总线能够提供高带宽接口并完成大量数据传输。在AHB总线互联上,该系统包含多个master同时在AHB总线中,master数量不能高于16个。master传输时可提供HADDR和HWRITE,控制信息系统中包含多个slave,可实现master发出的传输信号响应,并将结果返回给master,系统需要包含Arbiter,同时多个master申请占用总线时,通过特殊机制允许优先最高master获得总线占有权。此外,每个AHB互联的系统都包含一个dcoder对传输结果进行编码,同时根据编码结果生成slave所需要的信号。在AHB总线传输过程中,传输前AHB master需要向Arbiter发出信号请求,如果MACR被允许占用总线后才能够开始信号传输,整个过程包括一个addiss phase和多个data phase。前者持续一个时钟周期,所有slave需要在该时间段内进行信号采集,如果在这一时间段内没有采集到有效信息,将会使传输信号失败,而后者包含多个时钟周期,通过拉低信号可插入等待周期,进一步延长数据采集周期,为设备获得充足的数据采集时间。

2 SDIO总线协议

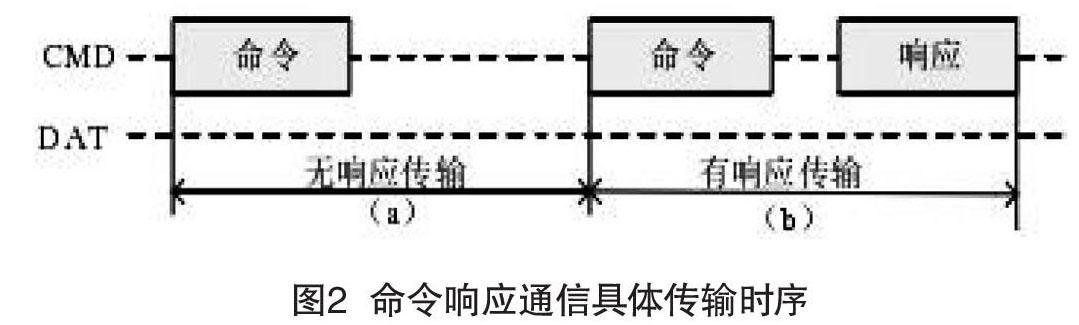

芯片SDIO接口是基于SD总线协议逐渐发展而来的,这两种主线在兼容性上主要体现于软件、机械信号等多个方面,除能够与SD总线时间兼容之外,SDIO接口还具有独特性。首先,较强的可拓展性,可支持多个I/O功能模块,可面向移动和固定设备运用;其次,SDIO接口能够像SDIO Host返回信号中断;最后,其工作过程中电压较低,信息传输速度快,能够为移动设备提供高效传输且功率消耗低的I/O接口,从类型上可将SDIO卡分为高速卡、低速卡两种,高速卡可实现SPI,SDI和SD4这3种模式运行,最高信息传输速率可达到200 Mbps;低速卡可实现SPI和SDI两种模式运行,传输速度相对较低,传输速率仅为400 kbps。在处于不同运行模式下,各管脚功能存在差异。从其传输持续上来看,总线通信是通过命令响应数据传输进一步实现的总线设备,可通过相互兼容的方式使技术标准传输时序实现,在传输时期中,SD总线包含两种基本传输,即写数据传输和读数据传输。在基本函数中,整个过程包含的命令响应通信具体传输时序如图2所示。

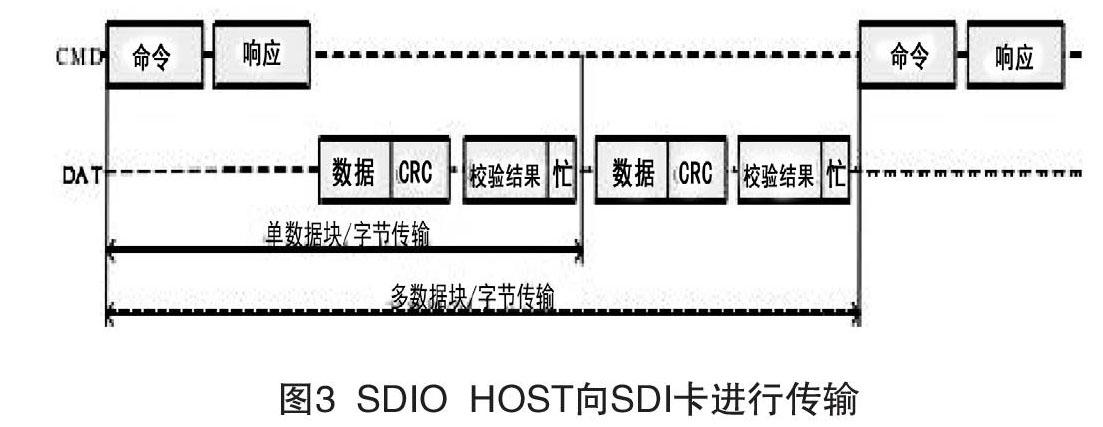

在该图中,基本传输过程包含无响应和有响应两种传输操作,整个传输时可借助CMD线实现,不需要通过数据总线DAT参与信息传输过程,在写数据传输过程中,该过程包含命令响应数据通信,数据的传输是由SDIO HOST向SDI卡进行传输,具体传输实际图如图3所示。

在该数据传输中,写数据传输共包含单数据和多数据块字节传输两种方式,完成每单位数据传输后,SDIO卡需要对通讯数据进行校验,结果会自动返回至SDIO HOST中。在读数据传输中,整个过程包含命令响应数据通讯,其传输方式为由SDIO卡发至SDIO HOST中,具体的传输时序如图4所示。

根据图4可知,读数据传输是与写数据传输方式基本一致,每单位数据传输完成后,需要由SDIO HOST对通信数据进行校验,并将结果决定是否保留接收数据作为最终的有效数据。

3 SDIO接口设计和实现

基于上述设计需求特点,研究SDIO接口硬件结构设计,如图5所示。

在该模块中,SDIO接口结合不同的功能需求由命令解析、循环冗余、校验生成、SD接口、AHB接口、数据控制等多个功能构成,SD接口和AHB接口是总线接口,在不同时钟域下两个接口工作,对设计SDIO接口来说是异步的,异步处理模块对两者信息通信实现一步操作,比如命令解析模块,该模块主要实现采样CMD线命令,正确进行命令参数信息体系可将对应参数转为有效信号,进而能够显示SDIO接口操作,在本设计中可以使用有限状态机(Finite State Machine,FSM)实现命令的接收功能,具体状态机实现如图6所示。

在响应产生模块设计过程中,可根据其他模块返回的信息正确向主设备返回卡的操作环境,检验结果卡状态信息具体功能,实现状态机如图7所示。

通过图7可发现,响应产生状态期主要包含空闲、SD模式、等待、有效数据响应位、响应CRC等工作状态。当硬件上软件复位后,状态机则处于SIDLE状态中。在数据控制模块中,当SDIO HOST发起数据传输命令之后,能够对相应数据进行缓存、转换以及多路选择等操作,确保数据在传输过程中不会丢失,并能够严格按照协议进行持续传输[1]。数据控制模塊可实现读写操作的一系列流程,为降低模块设计复杂性,需要合理进行数据控制,将模块功能分割为多个子模块,实现所有功能,数据控制模块的结构如图8所示。

图8中,方框部分为数据控制模块,该模块被划分为字节计数、数据接收、发送、选择这4个功能模块,右侧读写模块是对传输数据实现同步操作。

AHB接口模块,能够高效处理SDIO接口传输的信息,同时将SDIO接口集成到芯片架构中,整个接口模块,主要由AHB从设备和主设备两种功能模块构成。在同设备中,整个设计可实现SDIO接口与CPU的交互,通过CPU对SDIO接口寄存器完成读写,同时SDIO接口可将读写过程中断并返回至相应的CPU,并且使CPU实时监控SDIO接口的数据传输情况。在芯片设计架构中,SDIO接口的机制为0x4000xxxx.,在SDIO接口实现数据传输时,需要CPU对功能寄存器完成正确配置,同时实时检查状态寄存器的运行情况,确保数据可实现正常传输。对于AHB主设备来说,该模块可实现SDIO接口数据协议转换并完成标准SD总线形式数据和标准AHB总线数据之间的转换,当利用SDIO HOST进行大量数据传输时,采用传统的输入指令或者中断方式来有效控制信息传输过程,最终会使CPU被长时间占用,导致部分数据丢失。采用DAM的传输方式可以减少CPU所占用的时间,进一步提高信息处理能力,在AHB总线中进行SDIO集成设计可以使用AHB主设备传输方式,进而实现DMA信号传输。SD总线在传输速度上有一定限制,为确保数据能够快速传输,该模块需要支持的Burst,类型可以在标准协议传输中进行筛选[2]。

4 仿真与验证分析

在整个验证中,功能仿真式的主要内容是分析所设计的RTL逻辑性,确保RTL可满足相应的应用需求。功能仿真无需考虑时序问题,且仿真速度快,可通过所输出的文件波形快速进行结果分析,为全面检测SDIO接口功能和搭建下列测试平台。完成测试平台中不同功能模块设计后,应按照相应流程进行仿真测试,在具体方针中要求仿真具有高效性,能够在短时间内进行错误纠正。同时还需要具备一定完备性,在设计中存在错误要求仿真可达到功能覆盖率。通过测试,发现所设计的SDIO接口各功能可实现正常运行,且处于SD4运行模式下能够支持的最高时钟频率可达到70 MHz,最稳定的数据传输效率最大可达到280 Mbps。

5 结语

本文主要分析了WiFi芯片架构,对系统总线AHB协议进行分析,阐述AHB在Burst传输过程的具体情况,为后续SDIO接口实现数据批量传输奠定基础。阐述了SDIO总线接口特点功能,根据协议需求设计相应的SDIO接口结构,在WiFi芯片上集成SDIO接口并能够完成相应的测试,最终表明SDIO接口在WiFi芯片上可实现正常运行,最快传输率可达到280 Mbps。

[参考文献]

[1]刘雨沁,郭元兴,刘继平.基于FPGA的SDIO通信接口的设计实现[J].通信技术,2017(11):248-252.

[2]邰雪凤.基于WiFi的振动信号采集仪的研究与实现[D].天津:天津工业大学,2017.

Abstract:In recent years, with the development of internet technology, WiFi technology has strong stability, fast data transmission speed, low function consumption, etc. The advantages have already played a very important role in wireless communication. With the development of the times, advancements of WiFi chips are increasingly demanding. At present, it is a major problem for developers to quickly and efficiently expand the external functions of WiFi chips. In this paper, an external expansion interface, namely the SDIO interface, can be integrated in the WiFi chip architecture, which can provide a fast information transmission interface for the chip. This study describes the overall architecture of the chip, analyzes the SDIO HOST simulation model to build a simulation platform, and can complete the corresponding simulation verification. Finally, the chip test shows that the SDIO interface has different subfunctions, is reasonable in design, and has strong operability.

Key words:WiFi chip; high speed; secure digital input and output; interface; design; verification