Si掺杂化学共沉淀法制备氧化锌压敏电阻

2020-02-03马雪丽王月茜刘成

马雪丽 王月茜 刘成

(西安市西无二电子信息集团有限公司 陕西省西安市 710015)

1 引言

氧化锌压敏电阻片由于其良好的非线性在近几十年得到了飞速发展[1,2]。其体积小、保护水平高被广泛应用于各种电子电路系统[3]。氧化锌压敏电阻通过在氧化锌中添加其他的金属氧化物(如Bi2O3,Sb2O3,Co3O4等),经过球磨混合、成型后在隧道炉进行高温烧结,形成多晶半导体陶瓷[4,5]。平时呈开路状态,当外加电压达到一定数值时阻迅速导通,起到对电路进行保护的目的。配方、生产工艺对压敏电阻性能的好坏有着决定性影响[6]。本文在配方方面,用Si 掺杂代替Cr,在工艺上采用化学共沉淀法制备成Bi、Sb、Ni,Co,Mn 纳米复合粉体材料,通过配方调整和工艺改进,梯度由原来的(200~220)V/mm 由提高到(350~380)V/mm。烧结温度降低50℃。有效提高了性能,降低了生产成本。

2 实验目的

用传统方法和化学共沉淀法复合粉体材料分别制备氧化锌压敏电阻,通过8/20 波形冲击对比其通流能力,分析制作工艺对压敏电阻的影响,并研究其影响机理。

3 试验方法

按照传统工艺的配方精准算出化学共沉淀法中所需的金属的量,将金属块铋、锑、镍、钴、锰五种金属按照一定的质量投入到浓硝酸中,加入纯水,硝酸温度升高,进而溶解金属。配备成硝酸铋、硝酸锑、硝酸镍、硝酸钴、硝酸锰的混合溶液,在配备好的混合硝酸盐溶液中,加入适量比重为1.02 的草酸铵溶液进行沉淀(草酸铵为沉淀剂),沉淀过程中通过滴管吸取少量液体滴在滤纸上,根据滤纸背面颜色判断是否完全反应,完全反应后滤液透明。对完全反应后的草酸盐混合液,采用循环水式真空泵进行过滤,草酸盐沉淀留在滤纸上。为了得到纯净的草酸盐,用纯水进行反复洗剂和过滤。将洗剂后的纯净的草酸盐放入烘箱,在280℃进行煅烧并过筛,最后获得纳米级复合粉体材料。

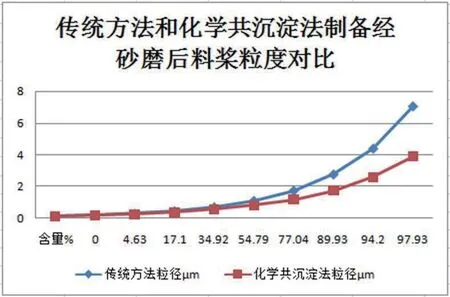

把化学共沉淀法制备的纳米复合粉体材料加入Al(NO3)3•9H2O、SiO2、硼酸、PV、磷酸三丁酯、分散剂、纯水,在球磨罐中球磨16 小时后,和氧化锌一起放入砂磨机砂磨3 小时,同时对传统方法配备的材料Bi2O3、Sb2O3、Ni2O3、Co3O4、MnCO3、Cr2O3、Al(NO3)3•9H2O、硼酸、PV、磷酸三丁酯、分散剂、纯水,球磨16 小时后和氧化锌一起砂磨3 小时,分别取料桨用百特粒度仪测其粒度,数据如图1所示。

通过图1 看到,传统方法砂磨3 小时后,99.98%的颗粒粒径小于7.057μm,用化学共沉淀法制备的纳米粉体材料砂磨3 小时后,99.98%的颗粒粒径小于3.882μm,化学共沉淀法制备的纳米复合粉体材料砂磨的料桨粒径更小,颗粒更细。砂磨后的料桨通过喷雾造粒,成型、排胶、烧结、涂银、烧银、焊引线、包封,制作成氧化锌压敏电阻器。

4 实验结果和数据分析

图1:传统方法和化学共沉淀法制备的料桨经砂磨后粒度对比

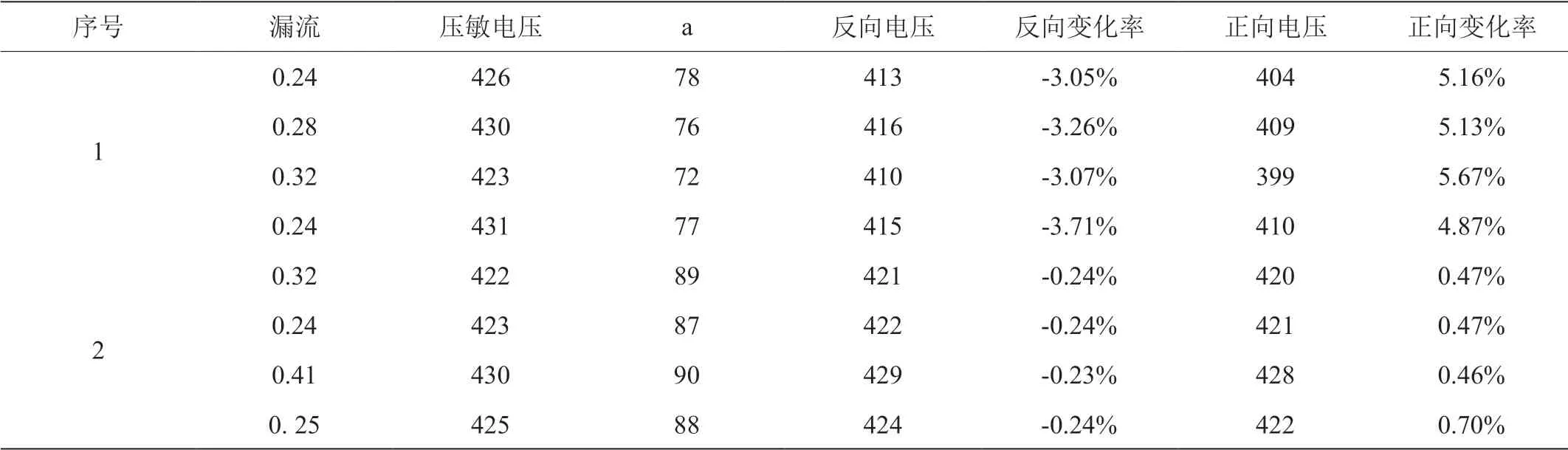

对传统工艺制作的压敏电阻片1号(片径10mm,梯度(200~220)V/mm)和化学共沉淀法纳米复合粉体材料制备的压敏电阻2 号(片径10mm,梯度(340~360)V/mm)通过8/20 波形在3500A 下冲击两次的正反向变化率,并取绝对值较大的方向进行比较,实验数据如表1所示。

根据表1 中数据,可以看到在8/20 波形3500A 下对两种工艺制作的压敏电阻进行1 次冲击试验,化学共沉淀法制备的纳米粉体复合材料制做的2 号压敏电阻通流能力更好,变化率小于1%。而传统方法制备的压敏电阻,变化率达到5%左右。通过实验数据对比,化学共沉淀法制备的纳米复合粉体材料制作的氧化锌压敏,电阻性能有很大提高。

5 实验机理分析

本实验所用的氧化锌是由间接法制备的多晶体,纯的氧化锌非线性很小,掺入杂质Bi、Sb、Ni、Co、Mn、Sn 等材料后,会偏析于氧化锌晶粒的边界,形成晶界,使得压敏电阻具有很高的非线性,这些添加剂控制着压敏电阻器的晶粒尺寸、非线性特征和电气性能。Bi 离子半径大,在烧结过程中随着ZnO 晶粒的长大偏析于晶界,形成绝缘性富铋相晶界层,因此Bi2O3在压敏陶瓷中形成了良好的非线性[8,9]。Sb2O3的掺杂能够控制ZnO 晶粒的生长,提高陶瓷的可靠性[10],Co2O3和MnCO3是受主型添加剂,在烧结过程中会俘获晶粒中的自由电子使价态发生变化,在晶界处形成受主态,从而提高晶界势垒高度。Cr2O3是一种常见的压敏陶瓷改性添加剂,它的掺杂不仅能提高ZnO 压敏陶瓷晶界受主型缺陷浓度,而且对晶粒生长有一定的控制作用,并使陶瓷晶粒尺寸分散均匀,从而提高压敏电压和通流能力。SiO2由Si 和O 原子组成的n 型宽能隙半导体,在压敏电阻配方中掺杂Si,烧结过程中,SiO2与ZnO 反应形成Zn2SiO4尖晶石相,起到与Cr2O3同样的作用。因此本文用SiO2代替Cr2O3,既满足了环保要求,又提高了压敏电阻的电气性能。另外,Zn2SiO4钉扎在晶界处能够抑制晶粒生长,减小晶粒尺寸,提高了压敏电阻梯度。Si 作为双电离施主提供导带电子,获得了更高的电子载流子浓度,ZnO 掺杂Si 后,提高了电导率。通过表2实验数据可以看到,si 掺杂后,梯度由传统配方的(200~220)V/mm 由提高到(340~360)V/mm。由于梯度提高,减少了材料的用量,添加剂总质量减少到40%,降低材料成本约35%。

表1:在3500A 下进行1 次冲击的变化率

另外,共沉淀法是所有制备粉体的湿化学方法中,工艺最简单、成本最低并且最终能制备出优良性能的粉体的方法。可重复性好,有利于工业化,制备条件易于控制、合成周期短等优点,已成为目前研究最多的制备方法。并且通过溶液中的各种化学反应直接得到化学成分均一的纳米粉体材料,容易制备粒度小而且分布均匀的纳米粉体材。在烧结过程中,粒度小,易于均匀混合,因此烧结温度降低了50℃。化学共沉淀法可以将复合粉体细度做的很小,使得影响纳米生长的各种成分能够均匀分布在晶粒的周围。晶粒尺寸减小,晶粒势垒高度的空间分布窄、分散性减小,从而提改了元件抗击浪涌电流冲击的能力。通过表1 数据可以看到,同样型号的产品,使用3500A 下的8/20 波形冲击,传统产品变化率达到5%左右,而化学共沉淀法制作的产品变化率不到1%。由于复合纳米添加剂的纳米效应,使得粉体的表面活性增大,烧结过程中液相传质出现较早,起到了主导作用,有利于早期气孔的排出,提高了元件性能。另外,添加剂的均匀性也使共沉淀方法制备的元件晶界势垒分散性相比传统固相要小,有利于提高元件非线性系数。复合添加剂粉体颗粒的细化,元件晶粒尺寸变小。宏观上提高了压敏电压,进而提高了压敏电压梯度。

6 结论

(1)在压敏电阻配方中掺杂Si,SiO2与ZnO 反应形成Zn2SiO4尖晶石相,Zn2SnO4 钉扎在晶界处能够抑制晶粒生长,减小晶粒尺寸,提高了压敏电阻梯度。

(2)在烧结过程中,粒度小,易于均匀混合,因此烧结温度降低50℃。

(3)晶粒尺寸减小,晶粒势垒高度的空间分布窄、分散性减小,从而提改了元件抗击浪涌电流冲击的能力。

(4)复合添加剂粉体颗粒的细化,元件晶粒尺寸变小。宏观上提高了压敏电压,进而提高了压敏电压梯度。