基于DDS的声光调制器驱动电路研制

2020-02-03李子金

李子金

(上海电机学院 上海市 201306)

1 绪论

1.1 绪论

世界上第一台磁选态铯原子钟于 1955年研制成功,其后经过了数十年的发展。上个世纪七十年代,有人提出了光抽运光检测的方式来代替磁选态,以增加原子的利用率和检测效率,提高Ramsey 谱线的信噪比[1]。

与磁选态铯束原子钟相比较而言,光抽运铯束原子钟将能态制备和能态探测从 A、B 磁铁换成了锁定在不同跃迁上的激光。与磁选态铯束原子钟相比较而言,光抽运铯束原子钟将能态制备和能态探测从 A、B 磁铁换成了锁定在不同跃迁上的激光。这样从制备上看,光抽运原子钟将所有原子都利用上了,提高了原子的使用效率,这样有利于提高铯束原子钟的信噪比,从而提高原子钟的的短期稳定度。而又由于简化了铯束管的结构,使得微波腔附近的磁场可以非常均匀,消除了不均匀磁场产生的Majorana 跃迁,这有利于提高原子钟的准确度。从检测的角度上来看,光抽运原子钟利用激光和光电探测器探测原子能态,由于使用了循环跃迁能级提高了探测效率,减少了背景噪声的影响,同样有利于提高原子钟的信噪比。另外,由于磁选态铯钟中存在较大的不均匀磁场,会对谱线造成频移,影响钟的准确度。

当然新的机制也会带来新的考验。由于光抽运利用了锁定在跃迁线上的激光器,激光器工作的好坏直接影响到原子钟的性能的优劣。本论文主要介绍了用于移频的声光调制器驱动电路的设计。

1.2 激光稳频方案

光抽运铯束原子钟利用一束激光作为抽运光,另外一束激光作为检测光来获 得 Ramsey 条纹。

在铯束管的检测区,原子束可以认为是准直的。调节检测激光与铯原子束垂直,可在荧光收集器上收集到原子和激光共振发出的荧光信号,利用光电探测器转换为电压信号。扫描激光频率,可以观察到束谱。可以直接利用原子束荧光谱作为激光频率参考。由于振子强度的不同[2],且并非循环跃迁线,可以看到62S1/2,F=4 →62P3/2,F=4 线的强度很低,而62S1/2,F=4 →62P3/2,F=5循环跃迁线强度高,信噪比优秀。因此用束谱来锁定探测光(4-5)线是可行的。

利用探测区的铯原子束谱来锁定探测光,并利用声光调制器将激光频移 251.4MHz 到铯原子 62S1/2,F=4 →62P3/2,F=4 跃迁线作为抽运光。同时可以通过AOM 的功率和频率控制电路实现抽运光的功率和频率调节。这样可以减少一个激光器和其相应的电路,大大简化了整个稳频光路系统。

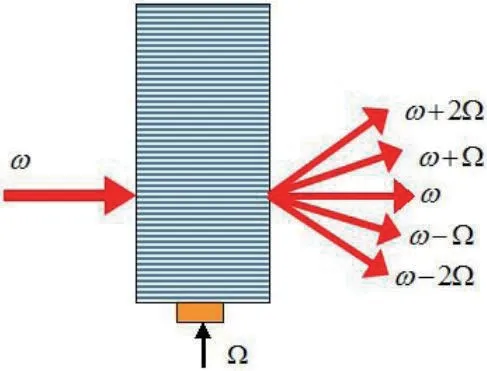

图1:声光调制器原理

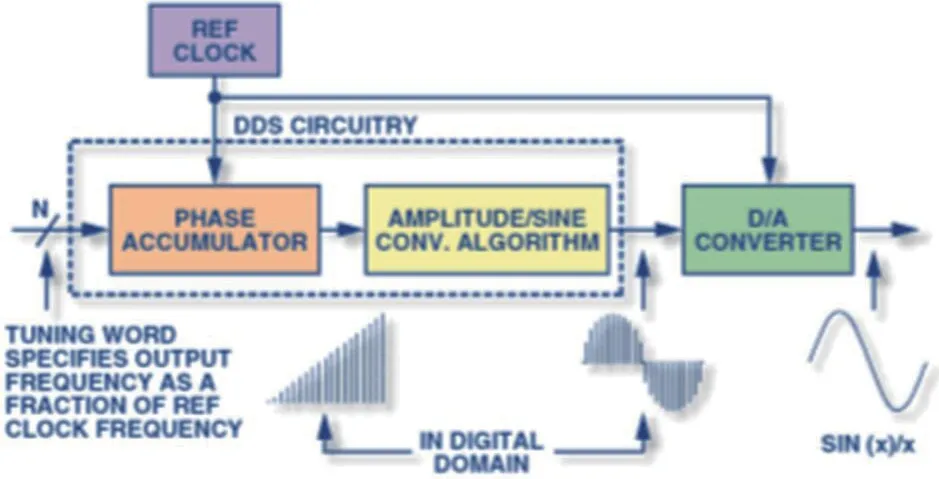

图2:DDS 原理框图

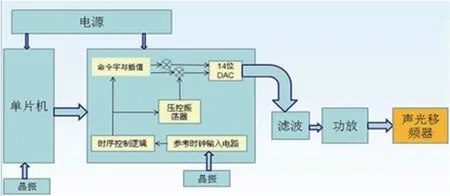

图3:AD9957 大致原理框图

图4:DDS 电路原理框图

这样一来,需要一个能够输出251.4MHz 正弦波信号用来驱动声光调制器的电路。声光调制器驱动电路的性能将直接影响抽运光的频率稳定度,进而对Ramsey信噪比产生影响。设计一个高稳定性、低温漂,且方便调节的AOM 驱动电路就变得尤为重要。

2 声光调制器驱动电路研制

2.1 声光调制器(AOM)和直接数字频率合成(DDS)原理

2.1.1 声光调制器原理

用于移频的声光调制器(Acousto-optics modulator,AOM)是一种外调制器件,在实验中既可以利用声光调制器实现激光的移频,又可以用来调节激光的光功率。原理是利用声光晶体的特性,将微波入射到声光晶体中,使其密度改变,进而使其折射率改变,形成折射率光栅,激光通过的时候发生衍射,并导致发生频率改变。如图1所示。

想要得到特定的激光失谐量,只需要输入相应频率的射频信号即可得到。声光调制器的驱动和控制直接影响激光频率,相位,强度,在激光控制方面有重要的应用。

2.1.2 直接数字频率合成原理

由前文可知,目前的光抽运铯钟采用单激光加AOM 结构,抽运光频率由检测光经AOM 移频得到,AOM 驱动电路的性能严重影响到抽运光的频率稳定性和准确度,进而影响抽运效率和Ramsey 信号信噪比。DDS 电路作为AOM 驱动较之原先的方式频率稳定性高,温漂较小,而且方便调节,有利于原子钟长期稳定。

直接数字式频率综合器 DDS(Direct Digital Synthesizer),本质上是一种分频器的实现:通过编程频率控制字来分频系统时钟以产生所需要的频率。在频率改变与调节时,DDS 能够保持相位连续,因此很容易实现频率、相位和幅度调制。此外DDS 还具有可编程控制的突出优点。目前,DDS 专用芯片已经逐渐普及,如今已成为电子系统及设备中频率源的首选[3]。

2.2 DDS芯片的选择和主要性能

需要的频率输出达到了251.4MHz,由于奈奎斯特采样极限的限制,DDS 芯片的系统时钟至少要达到500MHz 以上。为了尽量消除DAC 输出谐波的影响,应选择系统工作时钟能够达到1GHz的高速DAC 芯片。

最终在设计的驱动电路中采用了ADI 公司的产品AD9957。AD9957 是美国模拟器件公司(Analog Devices,Inc) 生产的内置了14位数模转换器的直接数字频率合成器(DDS)的集成电路,基本框图如图3所示。

根据我们的需求,只需要AD9957 在单音模式下工作,芯片用作正弦波发生器,通过 DDS 直接驱动DAC。

AD9957 采用4 组电源,分别为模拟电源1.8V 和3.3V,数字电源1.8V 和3.3V。AD9957 采用内建PLL 倍频模块,可将外部输入的频率进行倍频到1GHz 的系统时钟,从而可达到400Mhz 模拟输出[4]。

2.3 DDS电路的设计

图5:VCO 工作频率范围

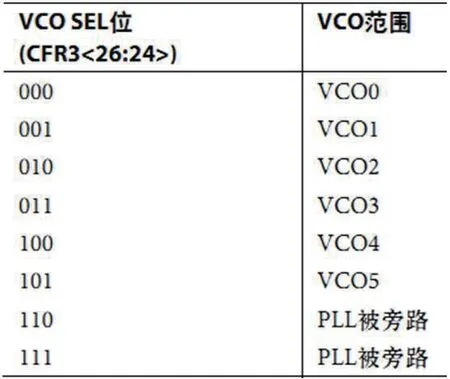

图6:VCOSEL 位选择

图7:电荷泵电流设置

根据驱动电路的需求,该电路需要几个模块组成,电源模块向单片机和AD9957 芯片进行供电,单片机模块和AD 芯片模块分别需要晶振向其输入一个外部时钟信号,AD 模块最后经数模转后输出的电压经过滤波、功放后最后进入声光调制器。示意图如图4所示。

由于功放部分散热需求较大,不适合集成到电路中,该电路输出的频率信号会通过一个单独的功放模块进行功率放大。

2.3.1 参考时钟

AD9957 内置了基准时钟乘法器,可以仅仅输入25MHz 的参考时钟产生1GHz 的内部系统时钟。基准时钟乘法器是一个可编程的,内置基于锁相环(PLL)的参考时钟倍乘器,输入的时钟可以是差分和单端,也可以是有源和无源。通过内部VCO,PLL 输出频率范围(fSYSCLK)限定在420MHz 至1GHz 之间。设置PLL 包括以下步骤。

图8:PLL 环路滤波器简图

图9:输出端低通滤波器

图10:1.8V 电源电路

图11:3.3V 电源电路

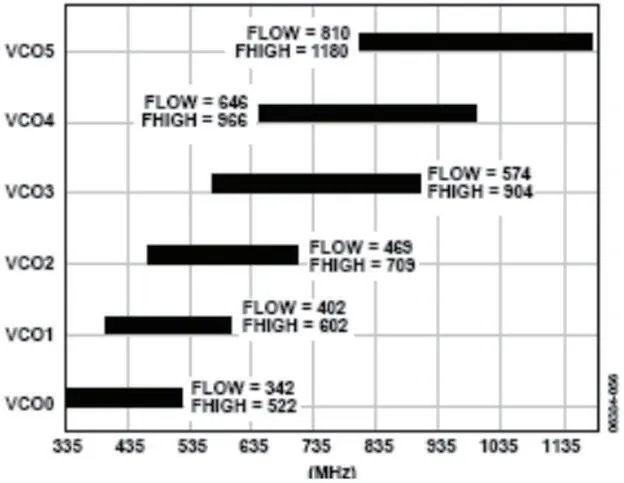

(1)VCO 设置。对VCO 进行编程,需要从六个工作频率范围中选择使得fSYSCLK处在范围内。

根据所设定的系统时钟的范围,根据奈奎斯特采样定理,输出250MHz,系统时钟需要1GHz 左右。设定为25MHz 晶振时钟经40倍频,故选择VCO5。设置控制字如图5、图6所示,CFR<26:24>为101。

(2)电荷泵电流设置。电荷泵电流(ICP)也需编程控制,下表列出了位设置和标称电荷泵电流之间的关系。如图7所示。

考虑到下文提到的环路滤波器设置,电荷泵电流(ICP)为337μA。

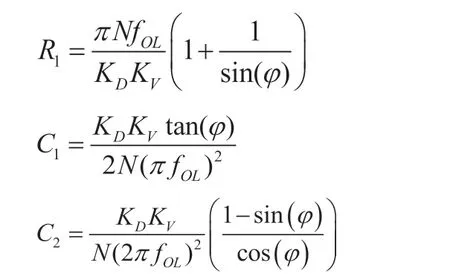

(3)外部环路滤波器设计。PLL_LOOP_FILTER 引脚提供了外部环路滤波器元件连接接口。

其中,fOL表示开环带宽,φ 表示相位余量,N 表示反馈分频系数,鉴相器增益KD等于ICP的编程值,Kv 可以通过VCO 设置表查询对应值。

图12:有杂散的输出频谱

图13:1GHz 时钟输出频谱

图14:875MHz 输出频谱

PLL 环路滤波电路如图8所示。

2.3.2 输出端滤波

经过内部余弦DAC输出的扫频信号不可避免地含有高频噪声,所以信号输出端口需外接低通滤波器抑制高频干扰。该设计采用七阶椭园函数滤波器,设计截至频率为400Mhz 的低通滤波器。电路图如图9所示。

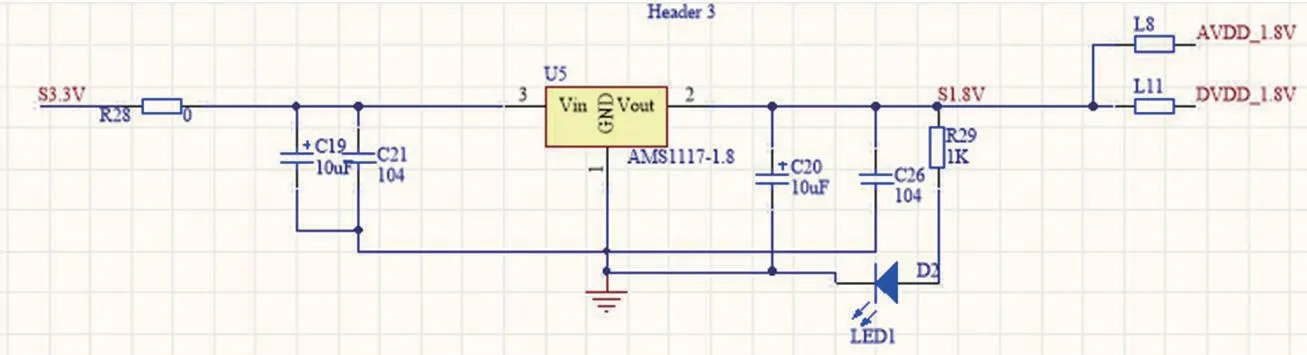

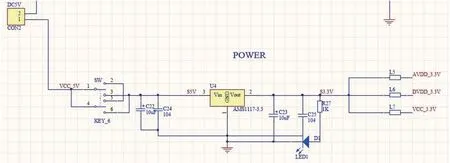

2.3.3 电源部分

电源的设计是电路中非常重要的部分,直接关系到整个驱动的运行和功耗等问题。AD9957 采用3.3V 与1.8V 供电,在单音模式下功耗最高可能达到800mW,1.8V 电源达近2A 的电流,3.3V 电源最大1A 的电流。因此,考虑到功耗损失较大,起初采用DC-DC芯片FR9888 进行电压转换。然而DDS 芯片对电源纹波噪声要求较高,FR9888 输出的电源中存在约350KHz 的交流噪声信号,会耦合到DDS 输出,严重影响频谱性能(见后节),因此在后来的设计中改用了LDO 芯片进行电压转换。本系统采用5V 输入,经LDO芯片AMS1117-3.3V 将5V 转为3.3V,尔后经AMS1117-1.8V 转换为1.8V。模拟与数字用电感隔开。电源电路设计如图10、图11所示。

2.4 单片机软件控制

本系统中采用STC12LE5A60S2 单片机作为控制,它的主要任务是完成与AD9957 的串口通信,程序采用C 语言编写。该单片机为单时钟周期,指令代码完全兼容传统8051,低压3.3V 供电,具有8 路高速10 位A/D 转换。

对DDS 器件的控制是通过向DDS 器件写命令控制字实现的。需要在AD9957 初始化后依次设置CFR1、CFR2、CFR3 三个控制字寄存器,然后设置Porfile0 寄存器作为DDS 频率和幅度控制字。

2.5 声光调制器驱动电路的调试与测量

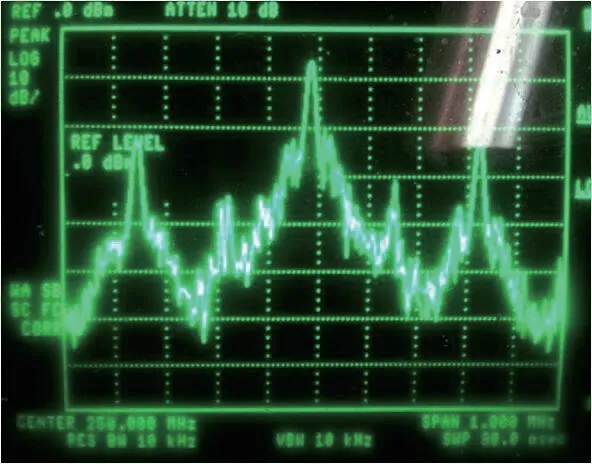

由串口对单片机程序烧写,设置AD9957 工作在单音模式,25MHz 晶振时钟经倍频40 倍后作为系统时钟,设置251.4MHz 输出,由频谱仪检测输出频谱。开始时频谱上有明显的杂散频率,如图12所示(显示范围1MHz)。

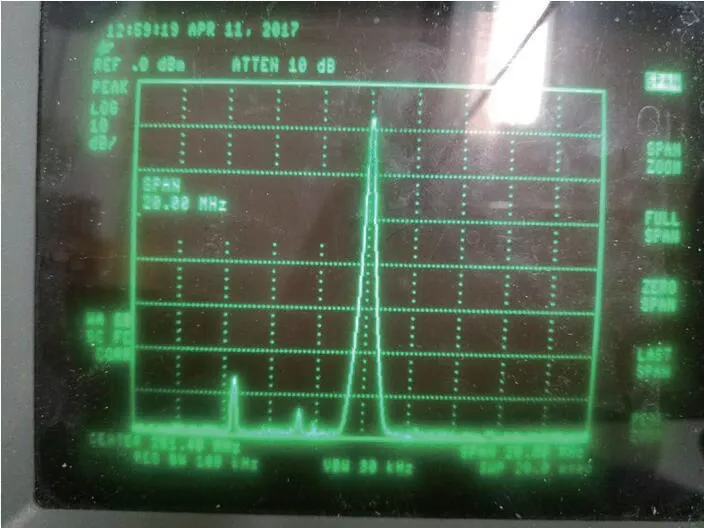

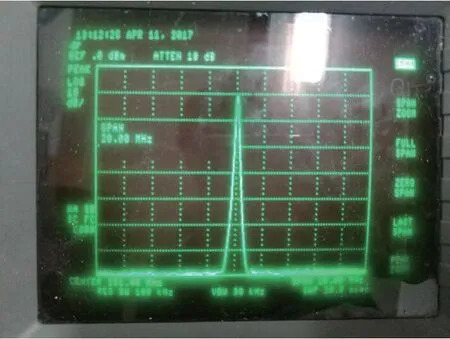

经分析杂散来源于电源噪声的耦合,DC-DC 电源芯片FR9888中包含了350KHz 左右的周期信号,严重地影响了输出频谱性能。替换为LDO 电源重新制板焊接后测试,频谱如下分别为系统时钟为1GHz 和系统时钟为875MHz 时输出251.4M 的频谱(显示范围20MHz)。

DAC 输出将不可避免的包含高次谐波。系统时钟为Fsysclk,输出信号频率为fout,则谐波将出现在2fout、3fout、4fout……以及Fsysclkfout,Fsysclk-2fout,Fsysclk-3fout……等频率处。因此当系统时钟为1GHz输出251.4MHz 时,将会在距离较近处(245.8MHz)出现谐波,将会影响到声光调制器的移频效果。为使输出频率(fout)尽量远离Fsysclk-3fout与Fsysclk-4fout谐波,选定时钟频率接近3.5 倍输出频率,即875MHz。此时频谱性能良好,经外接功率放大模块后满足声光调制器的需求。

3 总结

设计并制作用于驱动声光调制器(AOM)的DDS 数字频率合成电路。目前的光抽运铯钟采用检测光束谱稳频方案,为了降低原子钟复杂度和体积,采用了单激光加AOM 结构完成抽运光和检测光的同时锁定,抽运光频率由检测光经AOM 移频得到。采用了直接数字合成(DDS)作为声光调制器驱动电路解决方案。DDS 电路作为AOM 驱动较之原先的方式频率稳定性高,温漂较小,而且方便调节,有利于原子钟长期稳定。