一种航空电子模块电压采集方法设计及应用

2019-06-11刘红伟范永坤

文/刘红伟 范永坤

1 引言

为解决航空电子系统不标准的问题,北大西洋公约组织(NATO)成立了联合标准航空电子系统结构委员会(Allied Standard Avionics Architecture Concil, ASSAAC)。 目前,ASSAAC标准已经发布了5个标准:软件标准、封装标准、通信及网络标准、通用功能模块标准及系统相关问题指南标准。同时,ASSAAC定义了通用功能模块和通用处理模块两种标准硬件类型。为进一步降低成本,模块由一系列的通用标准电路单元集进行构造,如图1所示。这些通用标准单元集包 括MSU(Module Support Unit)、PSU(Power Supply Unit)、RU(Routing Unit)、NIU(Network Interface Unit)、PU(Processing Unit),模 块 物理接口是电源的输入接口和网络的输入输出接口。其中MSU负责监视和控制模块运行,提供模块BIT检测、初始化配置、维护测试等功能,完成模块健康状态检测和模块故障管理的数据采集输入。

模块内部芯片的供电电压的状态是模块健康状态的重要检测指标,是故障管理的重要数据输入。本专利提出了一种通用功能模块和通用处理模块的电压采集方法,来监控模块内部芯片的供电电压5V、3.3V、2.5V、1.8V、1.2V、1.05V、1.0V等的电压状态,并通过MSU进行检测结果采集。

目前的航空电子模块内部电压的检测多根据自身模块的特点采用的电压采集方法也不同:或利用模块中集成模数转换功能的DSP来采集模块内的电压,或利用模块中集成模数转换功能的高性能FPGA来采集模块内的电压,或采用多个单路的模数转换芯片来采集模块内的电压。同一个系统中也无法形成统一标准的电压采集方法。

国内在研的模数转换芯片多是单通道的模数转换器,一片芯片只能采集一路电压信号,用在模块内部进行电压采集就需要多片芯片,需要的数字接口的数量也会随着芯片数量成倍增加,不利于高集成度航空电子模块的设计。

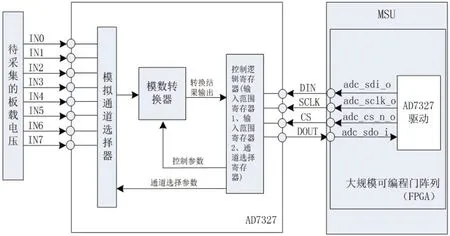

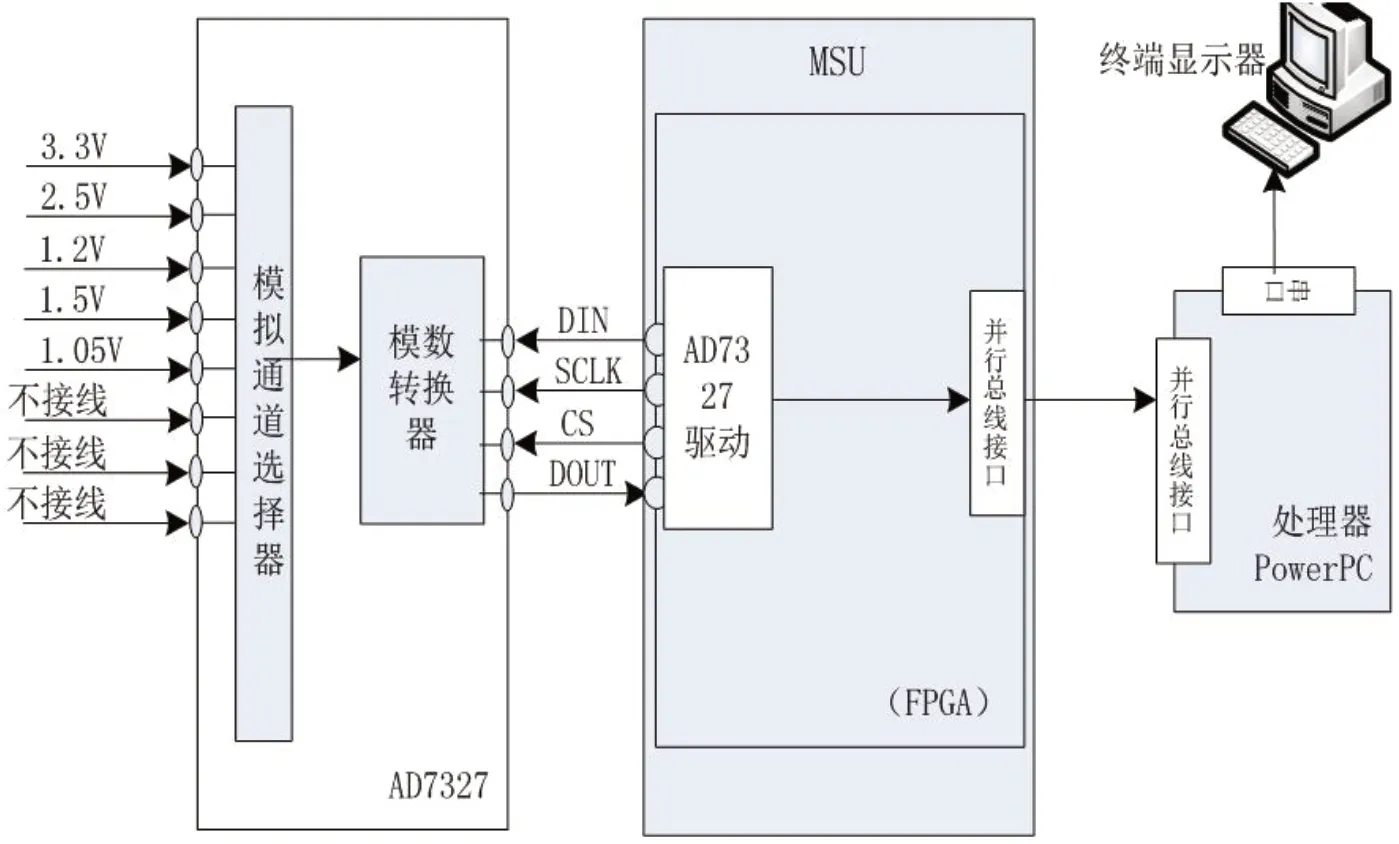

图2:多通道电压采集的硬件框图

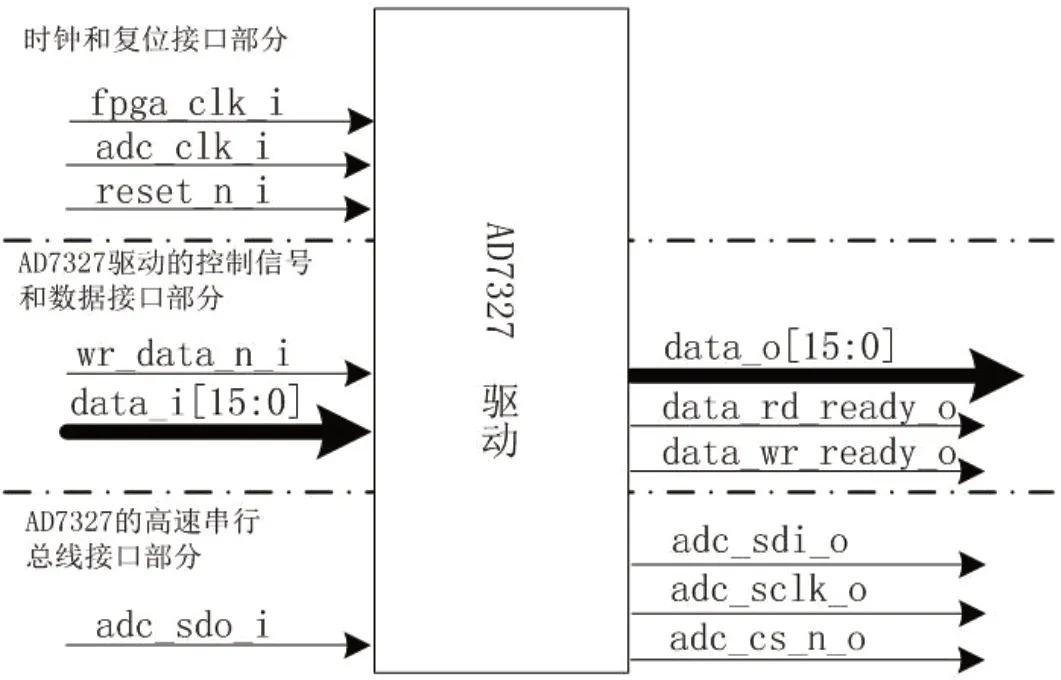

图3:AD7327驱动接口框图

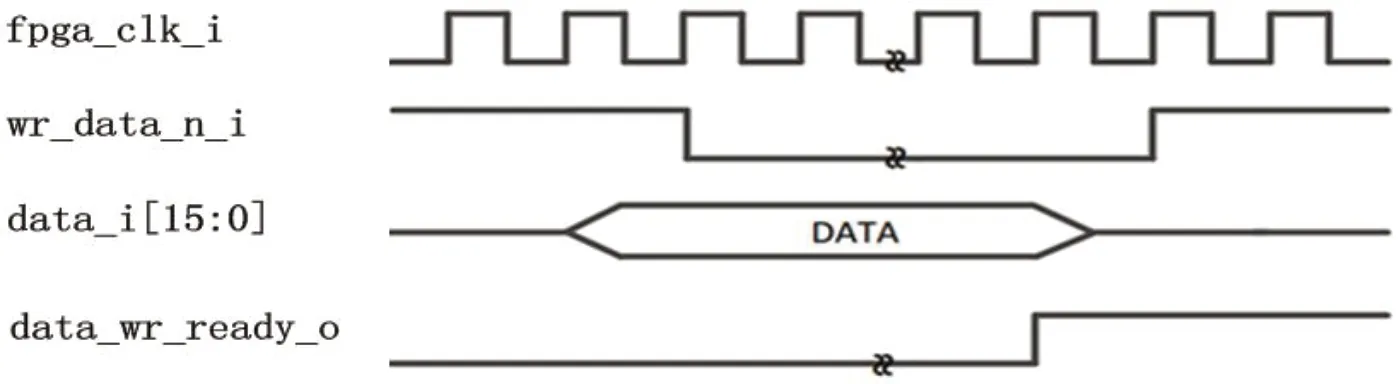

图4:AD7327驱动的读时序图

TI公司生产的AD7327是一款8通道12位采样率为500kSPS的模数转换芯片,检测电压范围可以软件配置成四种:-10V~+10V,-5V~+5V,-2.5V~+2.5V,0V~10V,数字输出接口为高速串行外设接口(Serial Peripheral Interface,SPI)。目前,限于通用功能模块和通用处理模块的MSU单元多使用没有集成模数转换功能的大规模可编程门阵列(FPGA),模块的健康状态检测结果多需要在没有集成模数转换功能的FPGA内部转换成并行数据进行上报,因此,需要对FPGA扩充SPI接口,并转换成并行数据进行上报电压检测结果。

SPI通信作为一种串行总线通信方式,有简单、高速、全双工传输等优点,广泛应用于数据通信、数据处理、航空电子、消费电子产品等领域,通过FPGA来进行SPI总线的协议解析、转换是常用的数据处理方式。

2 硬件设计部分

电压采集的硬件框图如图2所示。待采集的板载电压,例如3.3V、2.5V、1.8V、1.1V、1.0V等模拟信号通过AD7327的IN0~IN7管脚输入到模拟通道选择器,模拟通道选择器根据通道选择信号依次选择IN0至IN7先后输出到模数转换器进行模数转换,转换结果输出到控制逻辑寄存器,控制逻辑寄存器(包含输入范围寄存器1、输入范围寄存器2、通道选择寄存器)输出控制参数(如输入电压范围为0~10V的选择参数、参考电压为内部参考的选择参数、选择编码格式为补码格式的选择参数等)到模数转换器,控制逻辑寄存器输出通道选择参数到模拟通道选择器来选择IN0~IN7通道中的一个输入通道作为模数转化器的输入。同时控制逻辑寄存器列化出高数串行总线至管脚,分别为DIN、SCLK、CS、DOUT,其中DIN为高速串行总线的输入数据管脚、SCLK为高速串行总线的时钟输入管脚、CS为高速串行总线的片选管脚、DOUT为高速串行总线的数据输出管脚。DIN、SCLK、CS、DOUT通过包含于MSU的大规模可编程门阵列(FPGA)的普通输入输出管脚分别连接至AD7327驱动 的adc_sdo_i、ad_sclk_o、adc_cs_n_o、ad_sdi_o四个信号接口。

3 软件设计部分

3.1 AD7327驱动接口设计

AD7327驱动的接口信号图如图3所示,分为时钟和复位接口部分、AD7327驱动的控制信号和数据接口部分、AD7327的高速串行总线接口部分三部分。时钟和复位接口部分信号定义和功能如下:fpga_clk_i为AD7327的主时钟,由FPGA内部产生的100MHz时钟提供;adc_clk_i为输入给AD7327高速串行时钟的时钟源,由FPGA的100MHz时钟分频提供;reset_n_i为AD7327驱动的复位信号,复位AD7327驱动中的信号量的初始值,信号为低有效。AD7327驱动的控制信号和数据接口部分信号定义和功能如下:wr_data_n_i为写入AD7327寄存器的使能信号,信号为低有效;data_i[15:0]为写入AD7327寄存器的16位数据;data_o[15:0]为AD7327驱动输出的模数转换结果的并行数据;data_rd_ready_o为AD7327驱动输出信号,当电平为高时,可以从data_o[15:0]读出模数转换结果;data_wr_ready_o为AD7327驱动输出信号,当电平为高时,写入AD7327的寄存器操作完成,具备再次写入的状态。AD7327的高速串行总线接口部分信号定义和功能如下:adc_sdo_i为AD7327驱动的串行数据输入信号;ad_sdi_o为AD7327驱动的串行数据输出信号;ad_sclk_o为AD7327驱动的串行时钟输出信号;adc_cs_n_o为AD7327驱动的片选输出信号,为低电平有效。

图5:AD7327驱动的写时序图

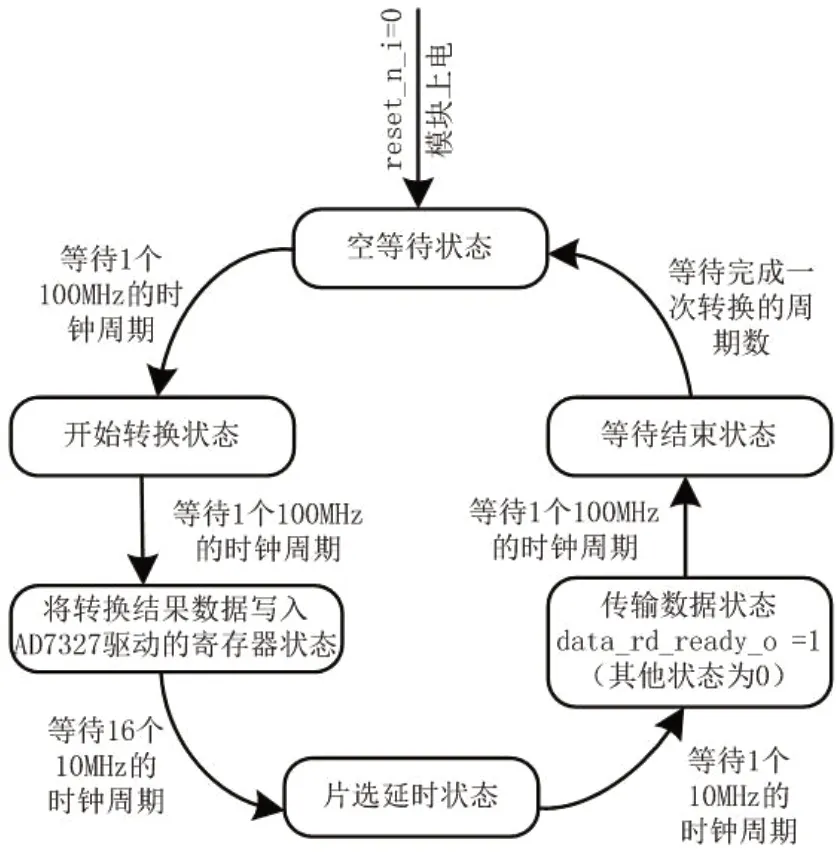

图6:AD7327驱动内部的状态机转换图

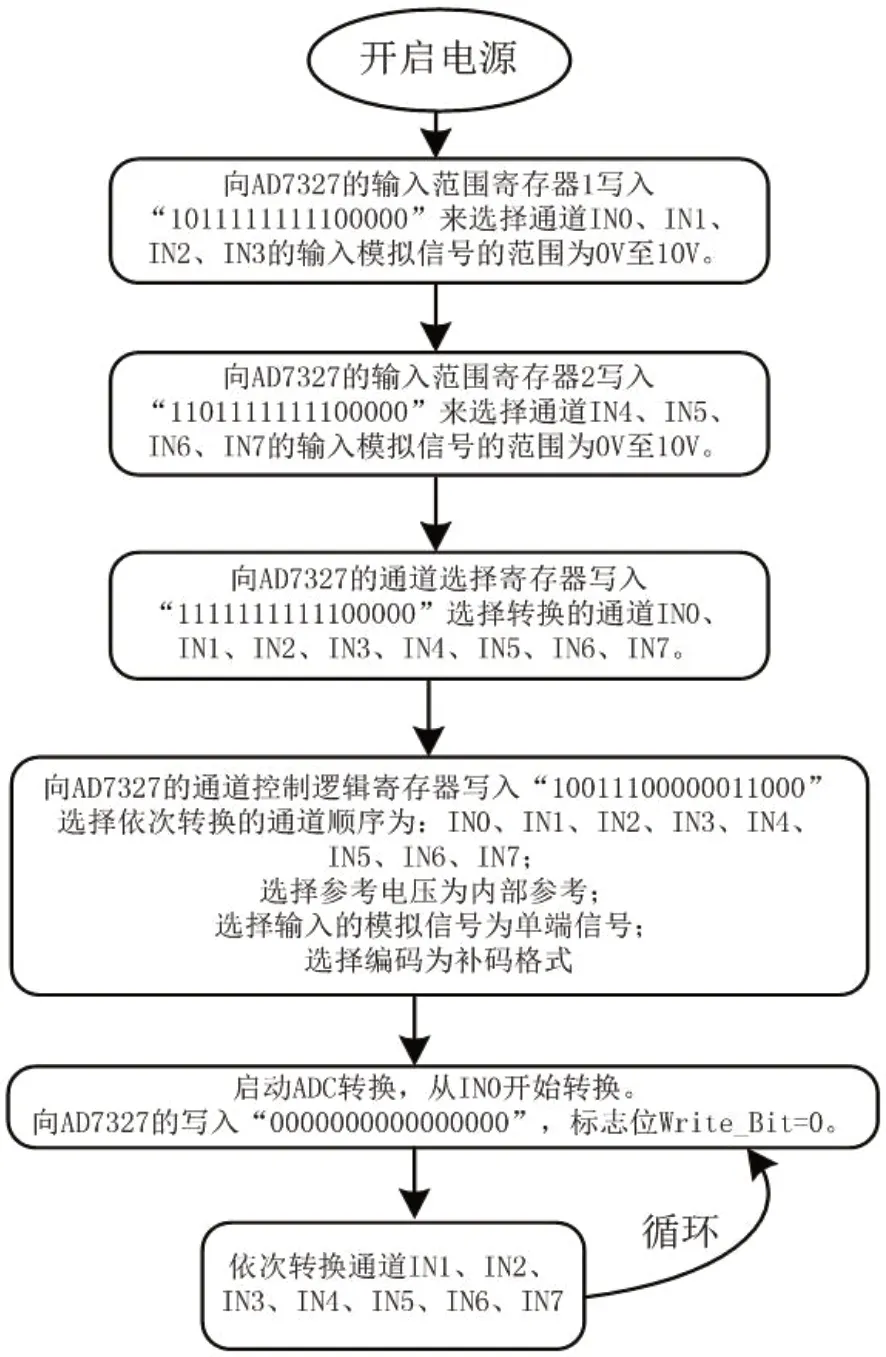

图7:全通道模数转换流程图

图8:测试平台框图

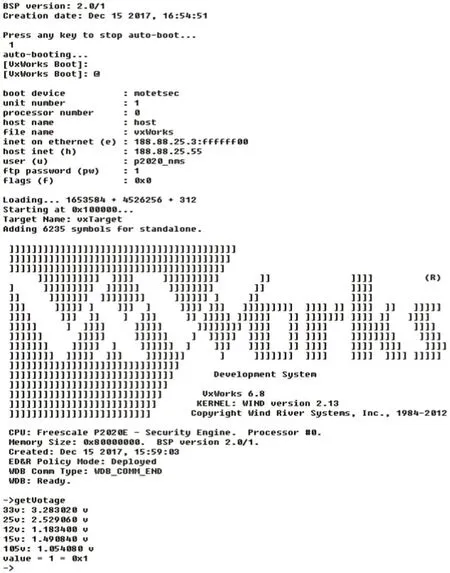

图9:测试结果输出

3.2 AD7327的读写时序设计

AD7327驱动的读时序图如图4。以100MHz的时钟信号fpga_clk_i作为读时序的时钟源,在表征数据可读的状态信号data_rd_ready_o为高时,通道转换结果的数据data_o[15:0]有效,可以读取其中的高3位作为通道编码:“000”为IN0通道,“001”为IN1通道,依次类推,IN0~IN7各通道编码唯一,data_o[15:0]的低12位作为该通道的输出结果。

AD7327驱动的写时序图如图5。以100MHz的时钟信号fpga_clk_i作为读时序的时钟源,在表征数据可写入的状态信号wr_data_n_i下降沿时开始将已经提前1个时钟周期准备好的数据data_i[15:0]写入不同的AD7327控制逻辑寄存器,其中data_i[15:0]的高3位作为寄存器编码:“101”表征输入范围寄存器1、“110”表征输入范围寄存器2、“111”表征通道选择寄存器;低12位为写入该寄存器的值。当写入寄存器操作完成时,表征完成写操作的信号wr_data_ready_o变高。

3.3 AD7327驱动状态机设计

采用状态机的软件架构使得AD7327驱动程序流程更具层次化,增强了软件的可读性和规范性。AD7327驱动内部的状态机主要由空等待状态、开始转换状态、将转换结果数据写入AD7327驱动的寄存器状态、片选延时状态、传输数据状态、等待结束状态共6个状态组成。模块上电、FPGA程序加载完成后,FPGA产生复位信号reset_n_i=0使得状态机处于空等待状态,复位信号reset_n_i=1变为高电平时,复位结束,等待1个100MHz的时钟周期,状态机进入AD7327开始转换状态,芯片开始进行预定通道的模数转换;等待1个100MHz的时钟周期后状态机进入将转换结果数据写入AD7327驱动的寄存器状态,该状态持续16个周期的10MHz的时钟周期,之后状态机进入片选延时状态,确保AD7327驱动内表征转换结果数据的寄存器稳定;等待1个10MHz的时钟周期之后进入传输数据状态,此时data_rd_ready_o=1(其他状态为0),此时data_o[15:0]有效,可以读出对应通道的模数转换结果;等待1个100MHz的时钟周期后状态机进入等待结束状态,该状态持续等待完成一次转换的周期数(完成1次转换的周期数是198个100MHz的时钟周期数);之后状态机又进入空等待状态,完成一次模数转换的循环。AD7327驱动内部的状态机如图6所示。

3.4 全通道电压采集流程设计

AD7327全通道模数转换流程图如图7所示。首先开启电源,AD7327供电稳定,大规模可编程门阵列(FPGA)供电正常,加载程序成功并正常工作;第二步,FPGA中的AD7327驱动向AD7327的输入范围寄存器1写入“1011111111100000”来选择通 道IN0、IN1、IN2、IN3的 输 入 模 拟 信号的范围为0V至10V;第三步,FPGA中的AD7327驱动向AD7327的输入范围寄存器2写入“1101111111100000”来选择通道IN4、IN5、IN6、IN7的输入模拟信号的范围为0V至10V;第四步,FPGA中的AD7327驱动向AD7327的通道选择寄存器写入“1111111111100000”选择转换的通道IN0、IN1、IN2、IN3、IN4、IN5、IN6、IN7;第五步,FPGA中的AD7327驱动向AD7327的通道控制逻辑寄存器写入“10011100000011000”来选择依次转换的顺序为:通道IN0、IN1、IN2、IN3、IN4、IN5、IN6、IN7,选 择 参考电压为内部参考,选择输入的模拟信号为单端信号,选择编码为补码格式;第六步,FPGA中的AD7327驱动向AD7327的写入“0000000000000000”,标志位Write_Bit=0,启动ADC转换,从IN0开始转换;第七步,依次转换通道IN1、IN2、IN3、IN4、IN5、IN6、IN7。循环至第六步开启下一次的ADC转换。

4 达到技术指标及工程验证

4.1 达到技术指标

该多通道电压采集方法已成功应用于某航空电子系统,并达到如下性能指标:

(1)最多采集电压通道数:8路。

(2)输入电压范围可变:可软件配置选择电压输入范围-10V~+10V;-5V~+5V;-2.5V~+2.5V;0V~+10V四种电压输入范围。

(3)采样率:500kSPS。

(4)每个通道的信噪比:大于72dB。

(5)单通道数据精度:0.61mV/LSB(最大输入范围差为5V);1.22mV/LSB(最大输入范围差为10V);2.441mV/LSB(最大输入范围差为20V)

(6)单AD7327的最大功耗:17mW。

4.2 工程测试平台及验证

某通用模块测试平台框图如图 8所示。板载的电压3.3V、2.5V、1.2V、1.5V、1.05V分别接入AD7327芯片的IN0~IN4通道,经AD7327模数转换,通过SPI总线将结果传输给FPGA,FPGA内的AD7327驱动完成串行SPI总线协议到16位数据线的并行总线的协议转换并传输,处理器PowerPC通过并行总线接口将转换结果接收并解析并行协议,并通过串口输出结果。

处理器PowerPC上运行嵌入式VxWorks操作系统,并输出板载电压的输出,如图 9所示。

5 结束语

本文针对航空电子系统中通用功能模块和通用处理模块的健康状态检测,提供了一种多通道电压同时采集的电压采集方法,降低了航空电子模块中多种电压采集时电路设计的复杂性,并在工程中得到实现和验证,可以满足航空电子系统模块对电压的采集的健康管理需求。