功耗性能兼顾

2019-03-25

源于“胶水”的多核心

现在我们都知道,在绝大多数情况下处理器的性能与核心数量成正比,多核“吊打”单核就是天经地义。然而,如何在1颗芯片里塞进(通过封装技术)更多核心?这个问题曾一度困扰着整个半导体行业。

将时间的指针拨回到1995年Pentium Pro的诞生前夜,受当年落后制程工艺(350nm~500nm)的拖累,别说在1颗芯片内实现双核设计,就连高速二级缓存单元都无法同时与运算核心在1颗晶圆颗粒内共存。因此,当时英特尔的解决思路是使用2颗晶圆颗粒,分别用于制造运算核心与高速二级缓存(L2),再将它们一起封装进1块CPU的基板上,最终造出了Pentium Pro(图1)。而这种将双晶圆“胶合”在一起的设计,就是“胶水双核”概念的最早来源。

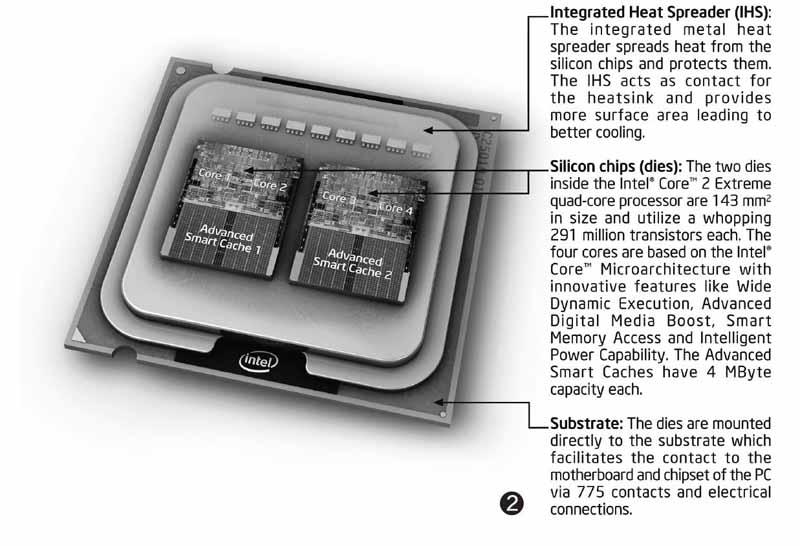

在未来的时间里,英特尔将“ 胶水”设计进一步发扬光大—— 先是将2个单核心整合封装的“奔腾D”(Penti um D)双核处理器,再到将2个双核心整合封装的Core 2 Quad四核处理器(图2),“胶水”的工艺和配方不断成熟,这种“胶合”在一起的多核处理器的表现也有所改善。

当然,这种由胶水粘贴出来的多核处理器依旧饱受争议,在当年曾一度掀起了“真假双核”和“真假四核”的讨论,大体结论是“真多核”性能大多領先“假多核”,以至于一提到“胶水多核”大家就一脸鄙夷。

时至今日,类似的“胶水”技术仍在处理器领域混得风生水起,只是它已经不仅限于单纯的CPU运算单元,而是可以“胶合”更多模块。

“胶水”技术再度兴盛

所谓的“胶水”,主要指的就是MCM(Multichip Module,多芯片模块)技术,它能将多颗芯片和其他单元组装在同一块多层互连基板上,然后进行封装,从而形成高密度和高可靠性的微电子组件。

继Pentium Pro、PentiumD和Core 2 Quad之后,英特尔还利用MCM技术先后将CPU和GPU(图3)、CPU和PCH(图4)、CPU和eDRAM缓存(图5)打包组合。

AMD也没闲着。进入Zen架构时代之后,AMD在Ry zen锐龙及EPYC霄龙处理器上也引入了MCM技术(官方称为CCX多核架构),它们可以在一块基板上封装多个CPU Die,每个CPU Die最多可集成8核心16线程的CPU和32MB三级缓存等单元。想拥有更多的物理核心和性能,只需搭配不同数量的CPU Die即可(图6)。类似的“胶水多核”还见于英特尔最新的Cascade Lake-AP 48核处理器,其本质是由两个24核的Cascade Lake处理器通过MCM技术组合而来,也并非原生48核。

虽然在历史上“胶水多核”的名声非常不好,但这项技术在今天却有着浴火重生的态势。究其原因,还是摩尔定律逐渐失效,提升频率和增加核心之路变得越发艰难。

理论上讲,将CPU、GPU、缓存、I/O等控制器打包到同一块晶圆芯片上(单片电路)最是完美(图7),但在半导体工艺逐渐逼近物理极限的情况下,既想要更多的核心,还要更高的主频,集成包括CPU、PCH、I/O单元、DDR内存控制器、PCIe控制器和IF控制器在内的所有常见功能模块,成本还不能太高——纯属做梦!

因此,在现有工艺的水平上,最经济可行的解决方案,唯有异构MCM之路。然而,处理器基板的面积有限,表面多颗芯片之间的通讯还存在延迟的隐患,这就需要处理器厂商优化封装技术,并引入更高速的总线接口。

封装技术的立体演进

想将不同的功能模块单元胶合在同一块基板上看起来很容易,但现实情况却是困难重重(图8)。比如,不是所有功能模块都需要最先进的工艺,CPU和GPU用7nm,内存控制器14nm就足够了。但是,想将这些不同工艺的芯片融合在一起,还要降低成本和保证良品率,这可不是传统2D封装技术能搞定的,于是就有了2.5D封装技术。

在2. 5D封装技术上,知名的方案主要以台积电的“InFO”(整合型扇出)和英特尔“EMIB”(嵌入式多芯片互连桥接)为主,前者能以较低成本的有机封装来连接芯片,但在密度上不如EMI B。此外。AMD曾在Fur y X显卡首次商业化的HBM显存技术将GPU核心与H B M 核心整合在一个底座上,新一代锐龙处理器采用的7nmCPU Die和14nm I/O Die单元分离设计(图9),也都是利用了2.5D封装技术。

我们可以将以英特尔EMIB为代表的2.5D封装技术理解为“平面版”的乐高积木,可以在一个固定大小的平面上,横向固定不同样式和大小的积木块。在处理器领域,这些积木块就变成了由不同工艺打造的不同功能模块,比如7nm工艺的CPU、10nm的GPU、14nm的I/O单元、22nm的通讯单元等等。EM I B的意义就在于能将不同制程的芯片组合在同一基板的封装之中,同时它还具有正常的封装良品率、不需要额外的工艺、设计简单等优点(图10)。英特尔和AMD携手打造的“KabyLake-G”平台处理器(整合Cof fe e Lake-H架构的C PU、AMD Ve ga架构的GPU以及4GBHBM2显存)以及Stratix 10 FPGA就是EMIB技术的首次预演。

问题来了,2. 5D封装技术可以容纳多少功能模块取决于基板大小,对于绝大多数处理器的芯片尺寸而言,空间总是不够用的。此时,就需要一种类似“立体版”的乐高积木了,可以像盖楼一般将所有需要的功能模块一层层地纵向叠加累积起来。

引领未来的3D封装技术

提起芯片的堆叠,可能很多朋友都会想到智能手机——几乎所有的新款手机都会选择将内存芯片覆盖在处理器芯片上以节省主板空间(图11),叠放还能让处理器和内存间的引线长度最短,从而降低线路噪音、访问延迟、电力损耗。手机领域的这种内存和处理器“叠罗汉”的设计即PoP(元件堆叠装配),它属于最初级的3D封装技术,属于一种在多成品芯片之间的“堆叠”+焊接。

真正的“3D封装”,应该是一种晶圆对晶圆(Wafer-On-Wafer)无凸起的键合(Bonding)3DIC制程技术。目前符合这一标准的技术,主要以台积电旗下的“SoIC”,以及英特尔主推的“Foveros”的3D封装技术为主。

先来看看台积电的SoIC技术,它是基于CoWoS与多晶圆堆叠技术开发的新一代创新封装技术,利用硅穿孔(TSV)技术将多种不同性质的临近芯片整合在一起(图12),用于结合的机密材料(号称价值十亿美元)能直接透过微小的孔隙沟通多层的芯片,在减小厚度的同时还能增加多倍以上的性能。

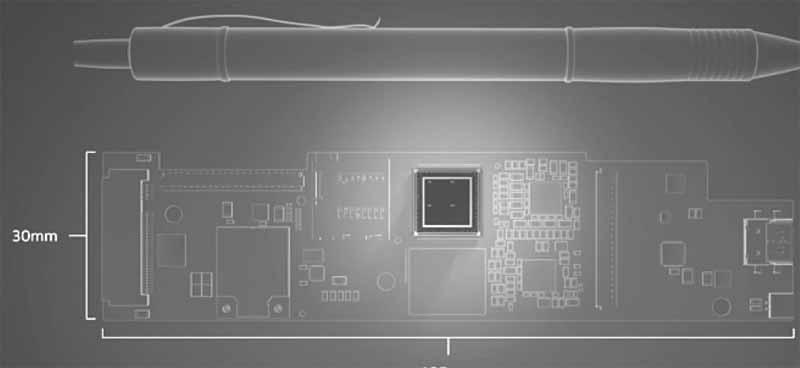

英特尔Foveros技术的原理是通过TSV和微凸块(Micro-Bumps)技术,堆叠其他的晶圆芯片和微芯片。它可以让只能在EMIB封装技术中以平面分布的功能模块纵向立体地摞在一起,在牺牲一点点厚度的前提下就可进一步压缩处理器基板的尺寸(图13)。以引言中提到的Lakefield处理器为例,它在12mm×12mm的面积里就集成了1个10nm制程的SunnyCove架构CPU大核、4个10nm制程的Tremont架构CPU小核、以及LPD DR4内存控制器、L2和L3缓存以及Gen11 GPU单元(图14)。

作为目前最高级的“胶水”,3D封装技术能在更小尺寸的芯片里就整合更多的功能模块。然而,在制程工艺已逼近物理极限,异构计算大行其道,更多不同类型的芯片需要集成在一起的大环境下,无论SoIC还是Foveros似乎都还有所不足。

为了实现基于封装技术就能在更小尺寸的基板上打造出集成多类型小芯片的SoC系统级单芯片的梦想,英特尔祭出了“终极胶水”——将2 . 5D封裝EMI B和3D封装Foveros技术优势集于一身的“Co-EMIB”方案(图15),它能在将多芯片横向拼接的同时,还能在任意芯片的表面继续“盖高楼”,并通过全方位互连(ODI)技术、裸片间接口(MDIO)技术和硅通孔(TSV)技术解决多芯片矩阵之间互联通讯和延迟等问题。

总之,在异构计算时代,“胶水多核”已经不再是招人嘲笑的对象,而是一种符合历史发展潮流的必然选择。只是,借助封装技术将更多芯片灵活地“打包”后,需要面临更为严苛的散热问题,开发人员需要更加精心地考虑系统的结构(甚至影响系统的物理结构和芯片的核心架构),以适应、调整各个热点。

英特尔的大小核战略

回到正题上来,前文提到的Lakef ield其实已经不再是单纯的处理器,而是一套完整的SoC,在指甲盖大小的芯片里就融合了过去需要布满整块主板的功能模块。除了成就这一辉煌的Foveros 3D封装技术,Lakef i eld全新的大小核架构也值得引起我们的关注。

提起“ 大小核”,相信很多读者朋友都会想到ARM领域的Big. Little技术。为了让智能手机的处理器(准确来说也是SoC)可同时兼顾高性能和低功耗的特性,ARM于2011年提出了Big.Little概念,允许SoC采用一组高性能“大”(Big)CPU集群和一组高效率“小”(Lit tle)CPU集群的组合,三星在CES2013大会上发布的Exynos5Octa(4×Cortex-A15+4×Cor tex-A7)就是首款基于Big.Lit tle技术设计的八核处理器。

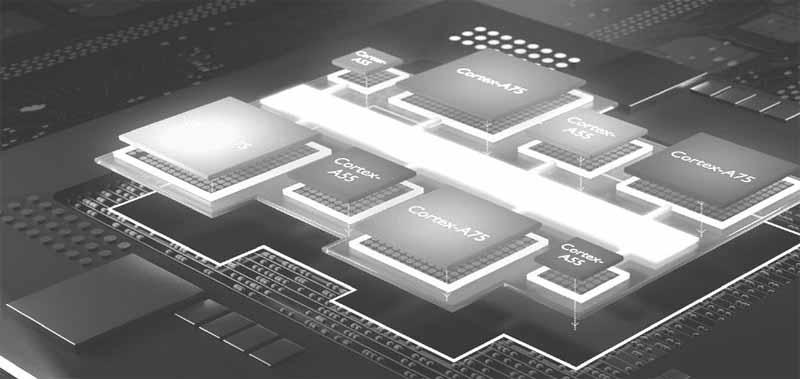

2017年,ARM在发布COrtex-A75和CO rtex-A55架构的同时再度祭出了DynamIQ技术,作为Big.Little的补充,它允许芯片厂根据需求和成本预算进行更为灵活的核心搭配,实现2+6、1+7等不同的核心配置方式,可以充分发挥芯片厂的想象力(图16)。比如,高通骁龙855采用了1+3+4、麒麟990采用了2+2+4的三丛CPU集群,玩大型游戏大核出力、主流游戏中核参与、日常操作小核足矣,从而实现了趋于完美的能效比表现。

PC领域的X86架构处理器其实也总在想办法平衡性能与功耗之间的矛盾,只是长期以来的解决思路都是通过TDP加以调节,并辅以灵活的主频升降机制(图17)。比如,面向台式机的酷睿i7-970 0主打顶级性能,拥有65W的TDP,基础频率就高达3.0GHz,睿频加速频率更是可以达到4.7GHz。面向二合一设备的Y系列酷睿i7-10510Y的TDP只有7W,将基础频率降到1. 2G Hz以节省功耗,并通过4.5GHz睿频加速来应对短时间内的高负载工作环境。

然而,这种调节机制的表现并不经济。还是以i7-10510Y为例,它运行在1.2GHz的主频时性能骤降,浪费了太多的性能和资源;加速到4.5GHz时的瞬间功耗可能会突破40W,发热和功耗将难以控制,最终妥协的结果就是只能在最高主频下坚持几秒左右。

于是,英特尔LakefieldSoC借着最新10nm制程工艺以及Foveros 3D封装技术,开展了X86架构处理器的“大小核”之旅,在一个晶圆芯片内就集成了1颗Sunny Cove架构(与第十代酷睿Ice Lake平台处理器同源)的大核,以及4颗Tremont架构的小核,成为了英特尔历史上第一款5 核混合架构的Big.Little处理器(图18)。

Sunny Cove是英特尔目前最先进的核心架构,这一点从10nm版的第十代酷睿处理器的实际表现就已得到了证明,哪怕只有单核心也足以应对日常较高负载的办公和娱乐环境。Tremont則是昔日“Atom”(凌动)家族的后裔(图19),最近几年主要被英特尔用于奔腾和赛扬品牌,主打足够的性能和更低的功耗。

和上代Goldmont Plus架构相比,Tremont架构在ISA(指令集架构)、微架构、安全性、电量管理等方面均有所提升,其中IPC(每周期指令数)性能更是提升了30%。Tremont独特的6路前置集群(双3路集群)乱序执行处理单元可以更高效地为后端提供高吞吐量,每个核心都内配备独立的1.5MB二级缓存,并新增三级缓存,整数和矢量单元执行效率也大大提升。

换句话说,LakefieId SoC中的Sunny Cove核心就是移动处理器中的Cortex-A77,而Tremont核心就是COrtex-A55。

小结

作为第一批武装英特尔Lakefield SoC的设备,微软Sur face Neo和三星Galaxy Book S都属于极致轻薄的偏概念型的产品(图20),本身也不是专注于发烧级性能的存在,而是帮助用户进行一场“说走就走的旅行”。Lakef ieldSoC超小的尺寸可以帮设备进一步瘦身,其特色的“大小核”架构也能更好地兼顾性能和功耗,在满足轻度娱乐和中度办公之余获得更少的发热和更持久的续航,而这些,不恰好就是3D封装和大小核技术的终极目标吗?