基于Verilog的SCMA系统编码器和译码器设计

2018-11-30熊兴中

王 甜,熊兴中

(四川理工学院 自动化与信息工程学院,四川 自贡 643000)

0 引 言

码分多址CDMA(Code Division Multiple Access)作为一种正交多址接入技术,由于其接入用户数与正交资源成正比,因此不能满足5G大容量、海量连接、低延时接入等需求[1],非正交多址接入NOMA(Non-Orthogonal Multiple Access)技术就成为当下5G多址接入的研究重点[2-4]。以稀疏码多址接入SCMA(Sparse Code Multiple Access)为代表的码域非正交多址接入技术将多个用户的数据进行码域扩频和非正交叠加后,在相同的时域、频域以及空间资源里发送,接收端通过线性解扩和干扰消除操作解调出各个用户的信息。由华为公司和电子科技大学提出的SCMA[5-6]就是应5G需求设计产生的一种NOMA技术[7]。SCMA技术不仅是一种频谱效率接近最优化的NOMA技术,并且适用于海量连接的场景。SCMA技术的基础是CDMA,它利用CDMA的一种扩频序列LDS[8-9]的稀疏性,即低密度扩频码,同时将CDMA比特流的调制映射模块和扩频模块结合在一起,直接将比特流映射到SCMA多维码字上,并由此获得成形增益,这也是用户容量大幅度提升的主要来源。这种稀疏特性的优点主要是可以使接收端采用复杂度较低的消息传递算法 MPA(Message Passing Algorithm)[10-11]和多用户联合迭代法,从而实现近似多用户最大似然解码。

相比4G的正交频分多址接入OFDMA(Orthogonal Frequency-Division Multiple Access)技术,SCMA可以实现在同等资源数量条件下,同时服务更多用户,从而有效提升系统整体容量。SCMA与OFDMA相比能同时服务更多用户的原因是:OFDMA每个用户占用一个不同的子载波,解调时用不同的子载波区分不同的用户。而SCMA中每个子载波上可以叠加两个用户的数据,但同时每个用户又不止占用一个子载波。其实SCMA区分不同用户的主要方法是用码本,即每个用户分配一个码本,码本包括用户占用的子载波以及在每个子载波上的调制方式。

综上所述,SCMA技术的优势在于:提高了用户连接数目,提高了链路性能;适合海量连接场景;低复杂度最大似然译码;和现有技术的兼容性。

1 SCMA编码器的设计原理

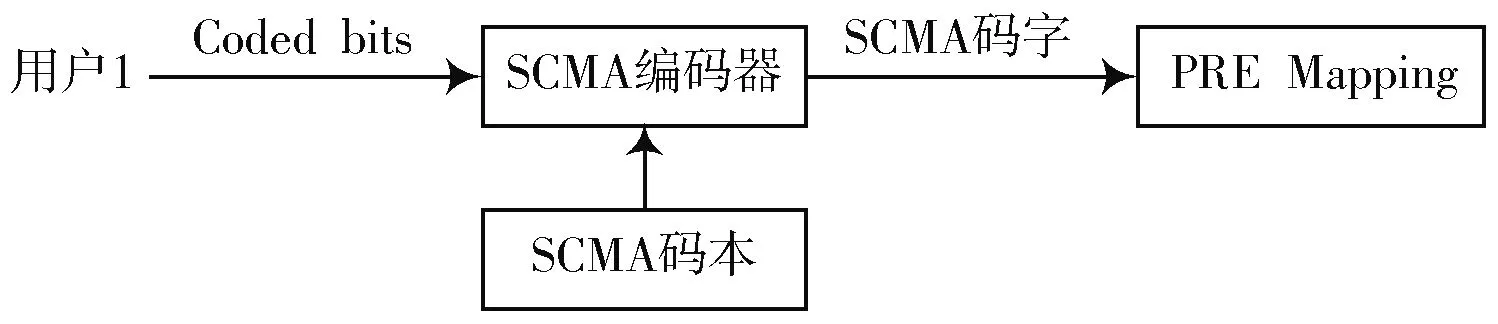

图1是一个用户进行SCMA编码的情形,其他用户与之类似。经过编码后的信息比特直接通过SCMA多维码本的编码就实现了调制和扩频双过程。所以SCMA编码器相当于兼顾了调制和扩频。SCMA编码器的关键部分是SCMA码本[12],从大量参考文献可知,码本的设计涉及多维星座图的设计,而多维星座图的设计又是个很复杂的问题,所以本文并未进行码本设计部分的研究。华为在2015年亚洲创新设计大赛5G专题竞赛中公开了一个SCMA码本[13]。这就是本文后续仿真中所要用到的码本。本文讨论的是6个用户和4个子载波的情形,当6个用户都编码结束后,每个用户输出的码字会进行叠加,然后映射到对应的物理层上。叠加的方式如图2所示。

图1 SCMA编码器原理图Fig.1 Schematic diagram of SCMA encoder

2 SCMA译码器的设计原理

本文设计的系统结构如图3所示,设计采用的译码算法是改进过的MPA,即最大值的对数域消息传递算法(Max-log-MPA)[14]。译码器的工作流程是:当接收到带有高斯噪声的信号r后,首先通过f(⋅)函数计算条件概率进行初始化,然后功能节点FN与变量节点VN沿着相连的边进行信息迭代更新,满足最大迭代次数后,变量节点输出信息比特的似然比,SCMA译码完成。整个过程主要由以下几部分完成[15]。

图2 SCMA码字叠加图Fig.2 Diagram of SCMA codon overlay

图3 SCMA译码器结构Fig.3 Structure of SCMA decoder

2.1 初始化条件概率

给出用户k在资源n的信道增益h_n=1,变量节点k在资源节点n上发送码字m_k的符号CB(k,n)(mk),噪声功率Nn可以用fn(⋅)函数计算包含各种可能性的残余信号。其中,M=4,F=4。令fn(⋅)=fn(rn,m1,m2,m3,Nn,hn,k),则:

采用Jacobi算法将考察变量都转换到对数域,去掉指数运算,即Max-log-MPA的SCMA译码,则式(1)变成:

认为先验概率相等,发送每个码字的概率相等,则有:

2.2 功能节点更新(FNU)

FNU不仅具有完成功能节点更新的功能,同时具有完成数据输入输出的功能。初始化阶段,中间信息存储器Message RAM中存储的数据为Ivg的初始值1M。功能节点通过其相邻的变量节点传递的外信息更新应用式(2),如图4所示,以一个功能节点g为例,FNU的表达式为:

依次类推,可知Igv2和Igv3的表达式为:

一个功能节点连接3个变量节点。每做一次FNU运算,需要输入3个用户的码本以及接收信号用来计算残留信号f,残留信号f与相连的变量节点传来的外信息Ivg求和进行FNU,在Max-log-MPA下,找到输出的最大值作为一次FNU结束,输出的Igv输入到Message RAM进行存储,并作为VNU的一个输入。

2.3 变量节点更新(VNU)

VNU具有完成变量节点的更新功能,把数据输出到Message RAM中,并从Message RAM输入由功能节点传送来的消息。变量节点通过其相邻的功能节点传递的外信息进行更新,这里一个变量节点连接2个功能节点,所以可以看作在变量节点上信息的交换。应用式(2),如图4所示,以一个变量节点v为例,VNU的表达式为:

式中:normalize使每个变量节点发送各个码字的概率和为1;apv(m)为先验概率。

VNU模块进行信息交换输出完成一次变量节点更新,输出的值Ivg输入到Message RAM进行存储,并作为FNU下一次迭代的输入。

图4 FNU与VNU消息传递图Fig.4 Message transitive diagram between FNU and VNU

2.4 对数似然比(LLR)的输出

应用式(2),一定的迭代次数之后变量v处LLR输出的表达式如下:

这样可以得到每个比特的对数似然比LLR,即可得到译码结果。

应用式(2)实现简化的SCMA系统,进行Max-log-MPA仿真。Matlab仿真条件为:6个用户,每个用户发送帧数为10帧,每帧1 024 bit,SCMA译码迭代次数为5次,turbo译码迭代次数为5次,码率为1 2。得到的SCMA在两种不同译码算法条件下的BER-SNR性能仿真曲线如图5所示。

图5 SCMA不同译码算法的误码率性能曲线Fig.5 Performance curves of BER of different decoding algorithms for SCMA

从图5可以看出,MPA与Max-log-MPA相比,性能要更好些,在信噪比比较小时,两者的误码率相差不大,但随着信噪比的增加越来越明显,然而都控制在1 dB以内。考虑到硬件实现条件、运行时间和算法复杂度的问题,综合考虑选择Max-log-MPA算法。

3 SCMA编码器和译码器的仿真

3.1 SCMA编码器的仿真

图6为SCMA系统发送端仿真波形。图中的输出相对于输入有一个周期的延迟,并且硬件语言Verilog语言无法识别负小数,所以本文将原始数据扩大128倍后取整进行运算。从图中可以看出:输入r分别有00,01,10,11,根据这4个值,用户结合自己的码本选择输出码字,6个用户非正交叠加输出信号y在4个信道上。其中00对应的输出为 18+30i,95-40i,95-40i,18+30i;01对应的输出为-8-117i,-48-138i,-48-138i,-8-117i;10对应的输出为 8+117i,48+138i,48+138i,8+117i;11对应的输出为-18-30i,-95+40i,-95+40i,-18-30i。

图6 SCMA系统发送端仿真波形Fig.6 Simulation waveforms of SCMA system sending end

3.2 SCMA译码器的仿真

从前面对SCMA译码器设计原理的介绍可知,首先进行功能节点更新输出Igv,输出的Igv作为VNU的输入。第一次迭代时,功能节点进行更新,从中间寄存器读取的Ivg是初始化的值,即1 4,和前面一样扩大128倍后就成了32。从源数据存储单元Src_Mem读取接收信号,由前面的编码器可知,这里的接收信号有4种情形,下面的仿真都只选取了第三种情形,用读取的接收信号和相关用户的码本计算相应的残留信号f,f再与从中间寄存器读取的Ivg一起根据Max-log-MPA的原则计算出Igv,并输入到中间寄存器Message RAM,以便VNU计算时从中间寄存器读取。注意到以下FNU模块仿真图中的数值都是扩大了128倍的结果,而最后译码结果的输出值因为是经过对数似然比后的输出,扩大的128倍会被约去,所以得到的是原始值。

FNU计算出来的值Igv供下一次VNU迭代使用,VNU计算出来的值Ivg再次给FNU迭代使用。这样反复进行5次之后,即前面所述最大迭代次数为5,将最后一次FNU输出的值Igv输入到LLR单元。在LLR单元中会计算出最终的译码结果,并将译码结果out输入到运算结果存储单元Result_Mem中。其中迭代次数以及FNU和VNU的工作顺序由控制单元Control控制。其中FNU第5次迭代的输出仿真图如图7所示,最后译码结果的输入就是来自于此图中的Igv。

其中I_g1v2_0表示功能节点g1到变量节点v2的信息,因为每次传递时有4个值,所以此处用0~3表示,后面的0表示第一个值。

最后SCMA译码器的输出结果应与编码器的输入一致。但是由于噪声和误差的影响,会有一定的失真。选取5作为迭代次数进行验证。图8~图10分别是迭代1次、3次和5次后FNU输出的值Igv输入到LLR单元后,计算出的最终译码结果。从图8中明显可以看出,只经过1次迭代的输出失真非常严重。而第3次和第5次失真情况相当,而且失真是在允许的范围内。每多做1次迭代运算,消耗的硬件资源就会相应增多。因此综合考虑,只进行5次迭代运算就输出译码结果。

图 8~图 10 中的 out1=data_Rx_bin[1][0],out2=data_Rx_bin[1][1],即表示用户1的两个比特的信息,依次类推,out3~out12表示用户2~6相应的比特信息。因为SCMA编码器部分,每个用户就是输入的两个比特的信息。在图8中可以看到,out1~out12分别为010100010110,而根据给出的输入信号,对应着编码器部分的输入为10的输出,所以最后的译码结果理论值应为010101010101。由此可以算出只经过1次迭代就输出译码结果的误码率为0.007 8。依次类推,可以算出迭代3次和5次后的输出误码率。从它们各自的仿真图9和图10可以得出,迭代3次和5次的输出结果分别为010110010101和010100010101,计算出的误码率分别为0.005 2和0.002 6,这些误码率都在允许的范围内。

图7 SCMA译码器的FNU单元第5次迭代的输出仿真图Fig.7 Output simulation diagram of the fifth iteration in FNU unit of SCMA decoder

图8 SCMA译码器经过1次迭代的译码结果仿真图Fig.8 Simulation diagram of decoding result of SCMA decoder after one iteration

图9 SCMA译码器经过3次迭代的译码结果仿真图Fig.9 Simulation diagram of decoding results of SCMA decoder after three iterations

图10 SCMA译码器经过5次迭代的译码结果仿真图Fig.10 Simulation diagram of decoding results of SCMA decoder after five iterations

4 结 语

本文对SCMA系统进行仿真设计,与CDMA相比,SCMA同样是码域应用的非正交多址接入技术,不同的是它采用的扩频码是一种可以使接收端复杂度降低的消息传递算法和多用户联合迭代法的稀疏码。同时SCMA还辅以F-OFDM时频资源分配的自适应方式,可以灵活地调整时频承载资源单元的大小,不仅可以适应系统空口接入众多业务中的各种需求,还能够在一定程度上提高系统的频谱容量和多址接入效率。从仿真验证结果来看,基于Verilog的SCMA系统的编码器和译码器实现功能完备,满足设计要求,系统性能在实际应用中是可以接受的。