面向5G新空口技术的LDPC码标准化研究进展

2018-10-19林峻良李莹莹陈前斌

柴 蓉,林峻良,李莹莹,陈前斌

(重庆邮电大学 移动通信技术重点实验室,重庆 400065)

0 引 言

随着移动通信技术的发展和智能终端的普及,第4代移动通信系统(4th generation mobile communication system, 4G)已无法满足日益增长的移动业务量需求。第5代移动通信系统(5th generation mobile communication system, 5G)应需而生,并成为通信业界及学术界的重要研究课题。5G将与其他无线移动通信技术密切结合,构建以用户为中心的信息生态系统[1],为用户提供低时延、高带宽、超可靠性等更加多样化的极限业务体验。

近年来,国内外各通信组织和机构均积极致力于5G相关研发。2012年,欧盟正式启动面向2020信息社会的移动及无线通信技术(mobile and wireless communications enablers for the twenty-twenty information society, METIS)项目[2],着手5G 的研究。2013年,中韩两国分别成立IMT-2020(5G)推进组及5G技术论坛,推进5G技术的发展。2014年,第3代合作伙伴计划(the 3rd generation partnership project, 3GPP)提出Re1ease14标准工作项目并对5G需求进行明确规范[3]。同年,国际电信联盟无线电通信组(international telecommunication union-radio communications sector, ITU-R)明确定义了5G的3大典型业务场景[4],分别为增强移动宽带业务(enhanced mobile broadband, eMBB),大规模机器类通信业务(massive machine type communication, mMTC)以及超可靠性与低时延业务(ultra-reliable and low latency communication, URLLC)。其中,eMBB通信场景主要指高峰值速率、高流量密度的移动业务,mMTC业务为具有低功耗、高连接密度的物联网业务,而URLLC则对应如车联网、无人驾驶等需要低时延、高可靠连接的业务。

5G中业务需求的多样性以及各类业务场景的典型特性均给传统移动通信技术,特别是信道编码技术带来新的困难及挑战。作为已商用的4G空口信道编码方案,Turbo码存在译码时延大、复杂度高、难以进行精确理论分析等缺点,难以有效满足5G eMBB业务场景下高速率、大数据量的性能需求。近年来,国内外研究人员针对5G信道编码技术开展研究,并已达成部分共识。低密度奇偶校验(low-density parity-check, LDPC)码因较大的灵活性和接近香农理论极限的性能受到业界公司重视,并成为5G新空口(new radio, NR)中编码技术的候选方案。在2016年11月召开的3GPP RAN1#87次会议上,LDPC码编码方案以较大优势战胜Turbo码与Polar码编码方案,被确定为5G eMBB场景数据信道的编码方案,这也意味着LDPC码成为了NR编码技术的研究重点。本文首先对LDPC码进行概述,进而针对近年来国内外研究人员围绕LDPC码开展的标准化工作进行分析综述。

1 LDPC码概述

LDPC码是一种基于稀疏奇偶校验矩阵的分组码,由麻省理工学院的Gallager博士于1963年首次提出[5],然而限于当时计算机处理性能及信道编码理论基础,LDPC码并未得到广泛重视。1981年,Tanner提出基于图论的观点对LDPC码进行全新阐释,采用二部图,也即Tanner图来表示校验矩阵的约束关系[6]。直至20世纪90年代,Mackay和Neal等对LDPC码进行研究并展示LDPC 码具有逼近香农限的优异性能[7],LDPC码才重回研究人员的视线,并成为信道编码领域的研究热点。

LDPC码可由稀疏校验矩阵唯一确定,这种矩阵结构决定LDPC码可并行译码并能降低译码时延。LDPC码的校验矩阵可用H=[hi,j](n-k)×n表示,其中,n为码长,k为信息位数,m=n-k为校验位数。根据LDPC码稀疏矩阵中每行或每列1的个数是否相同,可将LDPC码划分为规则码和非规则码[8]。若校验矩阵中每行和每列元素1的个数(行重、列重)相同,对应的LDPC码称为规则码,否则,称为非规则码。

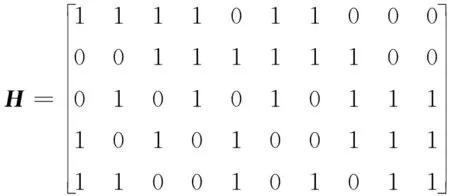

除用校验矩阵表示外,还可使用Tanner图表示LDPC码。Tanner图是一种双向图,用G={(V,E)}描述。其中,V是节点的集合,V=Vb∪Vc,Vb=(b1,b2,…,bn)称为变量节点集合,对应校验矩阵的列及码字中的信息比特;Vc=(c1,c2,…,cm)称为校验节点,对应校验矩阵的行及校验方程;E是变量节点和校验节点间相连的边的集合,E⊆Vb×Vc。当校验矩阵中hi,j=1时,节点ci与bj间有一条边相连;与节点相连的边的数目称为节点的度(degree),由某个节点出发经过若干条边又回到该节点的路径称为环(cycle),经过边的条数称为环长,最短环长称为Tanner图的围长(girth)。若给定LDPC码校验矩阵如(1)式所示,图1给出了该校验矩阵对应的Tanner图[6]。

(1)

图1 (1)式中校验矩阵对应的Tanner图Fig.1 Corresponding Tanner graph for the parity-check matrix in (1)

近年来,LDPC码因其优越性能受到通信业界及学术界的广泛关注,特别地,多家公司针对5G新空口场景下LDPC的标准化工作开展深入研究,并已取得阶段性成果。

2 LDPC码设计标准进展

本节将对面向5G NR的LDPC编码的码设计标准进展进行概述。

2.1 LDPC码设计概述

LDPC码的结构和性能均由其校验矩阵决定,因此,设计的关键是构造其校验矩阵。现有LDPC码构造方法根据校验矩阵构造方式的不同,主要可以分为两大类:随机化构造法和结构化构造法,其中,随机化构造方法在给定构造准则的前提下,通过计算机随机搜索构造校验矩阵,具有纠错性能好、译码存储复杂度高的特点;而结构化构造法采用几何、代数和组合设计等方法构造校验矩阵。由于其校验矩阵具有特殊结构,可显著降低硬件复杂度,能够解决编码器硬件实现困难的问题。目前,一些学者针对准循环LDPC(quasi-cyclic LDPC, QC-LDPC)码的设计问题开展相关研究。文献[9]联合优化Tanner图中包括围长及短环数目在内的结构以提高QC-LDPC码的性能,对Tanner图采用子阵检测(sub-array detection)以降低了环的检测时延。此外,该文献还提出一种结合超前掩蔽(pre-masking)的局部最优搜索算法构建具有较大围长、较少短环以及可实现的任意度分布(degree distribution)的QC-LDPC码。文献[10]研究了围长为8的规则QC-LDPC码对称构造法。文献[11]提出一种基于群环(group rings)理论的QC-LDPC码构造方法。

为实现灵活编码、降低编译码时延及复杂度,3GPP考虑采用结构化的准循环构造法对LDPC码进行码设计。准循环构造法是指通过定义基矩阵及准循环置换矩阵,构建结构化LDPC码。用该方法构造的LPDC码称为QC-LDPC码[12]。具体地,QC-LDPC码定义了一类基矩阵,将基矩阵和扩展因子Z结合扩展得到准循环置换矩阵,进而构成校验矩阵,因而具有良好的结构特性、更优的硬件实现,已广泛应用IEEE 802.11n, IEEE 802.16e以及IEEE 802.11ad等系统中,也是目前5G LDPC码的研究重点。

一个码长为N=pL的QC-LDPC码的校验矩阵H可由p×p阶循环矩阵构成的J×L阶阵列表示为

(2)

(2)式中:I(pj,l)为p×p阶零矩阵或循环置换矩阵。若I(pj,l)为循环置换矩阵,pj,l代表该循环置换矩阵的偏移值,即扩展因子。I(0)代表p×p阶单位阵,I(pj,l)表示I(0)循环右移pj,l后得到的矩阵,该矩阵每行每列均只有一个1,其中,矩阵第r行的1在第(r+pj,l)modp列,0≤r≤p-1,该行的其他列为0,0≤j≤J-1;0≤l≤L-1。I(pj,l)的右移次数pj,l构成校验矩阵H的基矩阵B,表示为

(3)

通过对基矩阵的扩展,也即基矩阵维度的合理设计可得循环置换矩阵及校验矩阵,而采用不同扩展方案或扩展因子集合可获得支持不同码块大小的校验矩阵,因此,需研究基矩阵扩展方案。QC-LDPC码也可由二部图表示,其中,一组节点为对应于码字比特的变量节点;另一组节点为对应该码校验约束的校验节点。二部图可有效反映码的奇偶校验约束,也即校验矩阵H的特性。给定一组原始二部图,也称基图(base graph),可通过对进行复制、置换构建不同LDPC码。因此,基图的确定也是码设计部分研究的重点。

2.2 LDPC码编码设计标准提案

LDPC码设计标准提案主要涉及码结构设计、基矩阵扩展因子设计和基图方案选择等内容,以下分别进行简要介绍。

2.2.1 码结构设计

针对LDPC码结构设计问题,综合考虑码块灵活性及实现复杂度,多家公司给出了建议及具体方案。文献[13]中,ZTE等公司提出了LDPC码统一基矩阵架构。基于该架构,通过将不同粒度(granularity)扩展因子的选择与比特填充操作相结合实现码块的灵活性;继而截取统一基矩阵中不同数量的校验位列并加以打孔以实现灵活可变的码率。针对长码块(long block-length)的传输情形,文献[14-15]中,Huawei和Mediatek等公司综合考虑吞吐量、码性能、编码复杂度、行并行(row-parallel)及块并行(block-parallel)译码器硬件实现等因素,提出具有准行正交(quasi row orthogonality, QRO)结构的QC-LDPC码,该结构由核心矩阵和扩展部分构成,如图2所示。

图2 准行正交QC-LDPC码结构Fig.2 QC-LDPC code with QRO structure

文献[16]中,Qualcomm公司提出高码率核心图和低码率扩展部分相结合的LDPC内嵌式基图结构。其中,高码率部分用于数据比特的初次传输(initial transmission)以获得高吞吐量,低码率部分用于重传(retransmission)以获得较高编码增益,其结构如图3所示。

图3 基图内嵌式LDPC码结构Fig.3 LDPC code with nested base graphs

2.2.2 基矩阵扩展因子设计

对QC-LDPC码的基矩阵采用不同扩展因子Z进行扩展,可获得支持不同码块大小的奇偶校验矩阵。针对基矩阵采用不同扩展因子形式,RAN1#88bis会议达成协议,LDPC编码器支持的最大信息块列数kmax及对应的最大扩展因子Z分别为{8 448,384},对应基矩阵最大信息块列数kb,max=22;支持kmax的扩展因子应具备Z=a×2j的形式,其中,a∈{2,3,5,7,9,11,13,15},j∈{0,1,2,3,4,5,6,7}[17]。

2.2.3 基图方案选择

综合考虑信息块长度、码率覆盖范围的合理性及性能等因素,研究人员对LDPC码的基图选择提出相关方案及建议。RAN1#88bis次会议中建议基图设计包含3种方案,分别为Alt1,Alt1a和Alt2方案。其中,Alt1方案为单基图;Alt1a方案为内嵌式(nested)双基图;Alt2方案为非内嵌双基图,每类基图方案均定义了所支持的码块长度范围和码率范围。各公司从系统鲁棒性、误块率(block error rate, BLER)、硬件实现和吞吐量等角度展开研究及评估,文献[18-19]中,Intel和Nokia等公司支持Alt2方案,建议将码率范围划分成为2部分,每一部分采用单独的基图,进而分别对各基图进行优化。Nokia公司所提出的设计方案尽量避免短环出现,通过重用移位网络实现行正交的灵活性,以达到降低时延、提高硬件实现效率的目的。文献[20]中,Samsung公司同样支持Alt2方案,并建议两类基图的界限应该根据误块率性能划定。

文献[21]中,ZTE公司建议采用Alt1方案,认为单基图的方案具有统一和简单的优点,适合行并行译码器的设计。相比选用2个基图的方案,Alt1方案所需ROM存储空间小,不会增加硬件实现复杂度。文献[22]中,Mediatek公司从实现的角度分析,认为Alt1a方案及Alt2方案各有优势。若采用行并行LDPC译码器,Alt1a方案可以减少复杂度;对于块并行LDPC译码器,可考虑设计一个新的控制器以减少时延,提供一定设计灵活性。

3 LDPC码译码算法标准进展

LDPC码的译码算法对信息的有效与可靠传输具有极其重要的作用[23-25],本节在对LDPC码的译码算法进行概述的基础上对算法标准进展进行介绍。

3.1 LDPC码译码算法概述

根据判决方式的不同,LDPC码的译码算法可分为硬判决译码算法和概率软判决译码算法,两者各有优缺点。

硬判决译码算法主要包括比特翻转(bit flipping, BF)译码算法、加权比特翻转(weighted bit flipping, WBF)译码算法[26]及改进算法[27-29],算法主要根据收到码字所生成的校验向量翻转原码字,再通过翻转后的码字产生新的校验向量,判断新的校验向量是否为零,实现迭代译码。这类算法优点是计算复杂度较低,实用性较强,缺点是译码精度较低。文献[30]提出一种改进的随机译码(stochastic decoding)算法的译码器架构,该架构主要由基于校验节点至变量节点(check to variable,C2V)传递信息的节点概率跟踪器构成。译码器采用节点概率跟踪器跟踪变量节点的概率,可实现更高译码精度以及与归一化最小和(normalized min-sum, NMS)译码算法相当的误块率性能。仿真结果显示,所提译码器可实现目前已知研究随机译码器的文献中最大的吞吐量-区域比(throughput-area ratio)。

概率软判决译码算法主要包括BP译码算法、对BP算法进行简化的MS译码算法以及一些改进算法[31-33],其核心思想在于通过消息传播,把当前节点的概率分布状态传递给相邻的节点,从而影响相邻节点的概率分布状态,经过一定次数的迭代,使得每个节点的概率分布将收敛于一个稳态。概率软判决译码算法较硬判决译码算法性能更优,但计算复杂度较高。文献[34]针对译码复杂度高的问题,提出一种基于边的低复杂度调度机制,该机制依据变量节点和校验节点运行时的可靠度更新Tanner图的边,新消息的更新只沿着不可靠的边进行传播。由于每次译码迭代过程只计算部分消息的更新,BP算法的译码复杂度得到降低。此外,限制消息更新的流动能避免短环的产生,有助于保持校验节点和变量节点的独立性。

3.2 LDPC码译码算法标准提案

近年来,多家公司针对5G eMMB场景中LDPC码的译码算法开展研究,已提出多种译码算法以及译码器架构设计方案,旨在实现硬判决译码算法性能提升或降低软判决译码算法的计算复杂度。综合考虑5G的业务特性及码的性能表现等因素,研究人员对LDPC码的译码算法进行分析。Samsung公司在文献[35]中提出采用饱和最小和(saturated min-sum, SMS)算法作为eMBB场景下LDPC码译码算法,通过在SMS译码器中增加尽可能多的饱和比特以达到准最大似然(quasi-maximum likelihood, QML)译码算法的性能。文献[36]中,ZTE公司提出一种含查找表(look-up-table, LUT)的对数域BP算法,利用查找表实现校验节点的更新以提高算法的性能。此外,该公司还提出依据最小对数域BP(min log-BP)算法及盒加对数域BP(box-plus log-BP)算法的校验节点更新方法。文献[37]中,Nokia公司评估了采用列表译码(list decoding, LD)、分阶统计译码(ordered statistics decoding, OSD)算法等QML译码算法作为LDPC码译码算法的有效性。

上述研究重点评估LDPC码译码算法的性能,也有研究对LDPC码与其他类型信道编码的译码算法进行性能分析对比。文献[38]中Ericsson公司分析对比低码率环境下的咬尾Turbo码(tail-biting turbo code, TBTC)采用极大对数域最大后验概率(maximum-logarithm-maximum a posteriori probability, max-log-MAP)译码算法与LDPC码采用SP及NMS 2种译码算法的性能,仿真结果显示,TBTC在较低码率及短码块(short block-length)条件下性能优于LDPC码。

目前也有一些研究针对译码算法的硬件实现进行分析及改进。文献[39]中,Qualcomm公司针对SP译码器硬件存储复杂度高以及MS译码器在某些速率下性能恶化的问题开展研究,提出了一种修正的最小和(adjusted min-sum, AMS)译码算法,并证实该译码器存储复杂度与MS译码器类似,且在所有码率及码长范围内的性能接近SP译码器。此外,该公司也提出采用分层译码器(layered decoder)可提高LDPC码译码速度,且加入具有尺度不变(scale invariant)性的预处理步骤可使译码器忽略未知尺度因子及对数似然比(log-likelihood ratio, LLR)消息的错配,从而提高LDPC译码性能。

4 LDPC码速率匹配标准进展

速率匹配是移动通信系统中不可或缺的组成部分,对系统的纠错能力影响显著。本节首先对速率匹配研究进行概述,进而对面向5G新空口的LDPC码速率匹配相关内容进行介绍。

4.1 速率匹配概述

速率匹配是指信道编码后的比特流速率应与信道传输速率相一致。在不同的时间间隔内,传输信道的数据量大小并不是一成不变,但所配置的物理信道的时频资源却是固定的,因此,需要将比特流进行一定的调整从而符合物理信道的承载能力。

速率匹配可通过对信道编码后的比特流进行打孔或重复来实现。若输入比特流的数据量大于物理信道所能承载的数据量时,需要对比特流进行打孔操作;反之,需要进行重复操作。打孔具体是指依据预设码率,将某些比特从母码字比特序列中移除,将其后的比特前移;而重复则是在当前比特与之后相邻比特间插入一个当前比特。若发送端执行速率匹配,则接收端应实现与速率匹配过程相反的解速率匹配过程,从而恢复被打孔的比特或删去重复的比特。

LDPC码速率匹配相关研究还涉及到增量冗余混合自动重传(incremental redundancy-hybrid automatic repeat request, IR-HARQ)机制、冗余版本(redundancy version, RV)及包含速率匹配的LDPC码编码链(coding chain)设计的相关问题等。

4.2 LDPC码速率匹配标准提案

在近期RAN1会议中,一些公司针对5G eMMB应用场景需求,对LDPC码速率匹配、重传机制及编码链设计等问题开展研究。文献[40]研究了LDPC码循环缓存器中比特的放置顺序及有限缓存速率匹配(limited buffer rate matching, LBRM)的问题,提出应对系统比特在初始传输时给予最高的传输优先级,校验比特1次之,校验比特2的优先级最低,同时应打孔一部分校验比特2以保证LBRM的最差性能。

参考Turbo码速率匹配过程,文献[41]中,Ericsson公司对5G中LDPC码速率匹配进行改进。Ericsson认为速率匹配过程除包括打孔及重复外还应包括缩短(shortening)的操作,即在缩短的比特位置上填充零比特。该文献还对固定RV序列(fixed RV set)重传、增加RV的重传以及按序重传3种重传机制进行比较,并建议5G新空口采用与LTE相似的固定4个RV序列的重传机制。

文献[42]给出了基于循环缓存器的重传机制,Huawei公司认为针对IR-HARQ机制,采用按序重传优于固定RV序列的重传方式,且按序重传机制能够避免在采用固定RV序列[0,2,3,1]传输时可能会出现的跳跃打孔导致性能下降问题。此外,考虑到系统的鲁棒性及RV指示信令开销问题,Huawei给出增加RV数目的折中解决方案。文献[43]中,CATT公司提出3种LDPC码IR-HARQ重传机制的方案,所提方案中冗余版本对应的比特起始位置固定,各方案中,各次传输的比特信息不同,对应不同误块率与信噪比性能曲线。经方案对比,CATT公司认为LDPC码的HARQ机制应该支持重传系统打孔位的比特,以获得更优的误块率性能。

一些公司也针对LDPC码的特点研究设计编码链结构等问题。文献[44]中,ZTE公司参照标准中指定的Turbo码的编码链结构,提出LDPC码编码链的构成,并讨论链中各过程的功能及设计思路。文献[45]中,Intel公司基于RAN1#88bis会议所达成的协定,讨论了包括循环冗余校验添加(CRC attachment)、码块分段(code block segmentation)及零比特填充(zero padding)等过程在内的编码链参数设定等问题。

5 LDPC码性能评估标准进展

LDPC 码因具有错误平层(error floor)低、译码复杂度低等性能优点成为近年来纠错编码领域的研究热点[46]。本节分别对LDPC码性能评估理论研究,标准化工作中基于译码算法、基图方案和硬件实现等方面的性能评估进行介绍。

5.1 LDPC码性能评估研究

错误平层表现为误码率曲线中从中等信噪比瀑布区域(waterfall region)到高信噪比错误平层区域,曲线由陡峭变得平缓。诱捕集(trapping set, TS)是 LDPC 码出现错误平层的重要原因。为减少错误平层现象,需在评估码性能时需考虑对其进行优化。文献[47]针对诱捕集引起的码结构缺陷问题,提出了一种新型重点抽样(importance sampling, IS)方法评估瑞利衰落信道中LDPC码性能,该机制采用参数缩放(parameter scaling, PS)和均值平移(mean translation, MT)的方法分别对TS中数据比特和噪声的分布进行偏置,能提供更精确的估计性能和更高的仿真执行效率。文献[48-49]研究了误块率曲线中低信噪比瀑布区域性能,提出一种在不过多牺牲瀑布区域性能的情况下减少错误平层现象的算法。

此外,密度进化(density evolution, DE)[50]、高斯近似(Gaussian approximation, GA)[51]和外部信息转移图(extrinsic information transfer chart, EXIT chart)[52]是评估LDPC码性能的几种重要方法。其中,DE跟踪迭代译码过程中得到逼近香农极限的度分布对和码集的噪声门限值,其准确度高但计算量大;GA是DE的一维近似,在性能及复杂度上取得较好折中;EXIT图同样可看作DE的简化方案,拥有计算量小、鲁棒性好等特点。文献[53]针对AWGN信道中LDPC码DE性能的问题展开研究,通过对3种单参数GA模型精度分析,提出一种具有更高精确度的混合密度进化(hybrid-DE)近似方法。该方法不仅避免了使用GA法在前期译码迭代中过于理想的对称性假设,还减少了采用DE法评估LDPC码噪声门限值所需的计算时延。

5.2 LDPC码性能评估标准提案

近年来,LDPC码性能评估及仿真研究受到标准化组织和国内外各公司的重视。文献[54]给出了ZTE公司所提LDPC码与Samsung公司所提LDPC码的性能比较,如图4所示,仿真中译码装置采用洪泛BP(flooding BP)译码器。通过性能仿真对比,ZTE认为2家公司所提的LDPC码性能相近,且都没有出现错误平层的现象。文献[55]中,Huawei公司对Samsung,Qualcomm等多家公司提出的LDPC码进行性能评估及对比,在不同码率、信息块长度及偏移值条件下,分别采用洪泛BP及分层偏移(layered offset)MS译码器进行译码。Huawei认为所提具有非冲突准行正交特性(non-conflict quasi row orthogonality, NC-QRO)的LDPC码在不同码率范围内优于其他公司所提LDPC码,在误块率为10-4时无错误平层现象产生。

此外,也有研究对LDPC码与其他几类编码机制的性能进行分析对比。文献[56]中,Ericsson公司评估了各类码及译码算法的性能,分别考虑采用OSD和SPA译码的该公司所提LDPC码、采用max-log-MAP译码的TBTC、采用列表-维特比(list-Viterbi, LV)译码的咬尾卷积码(tail-biting conventional code, TBCC)及采用连续列表删除(successive cancellation list, SCL)译码的Polar码等几种编译码机制。基于仿真结果,该文献认为对于短码块采用OSD译码的LDPC码性能优于采用SPA译码的LDPC码。

图4 误块率为10-2时所需信噪比与信息位长度曲线Fig.4 Required SNR vs. information size at BLER=10-2

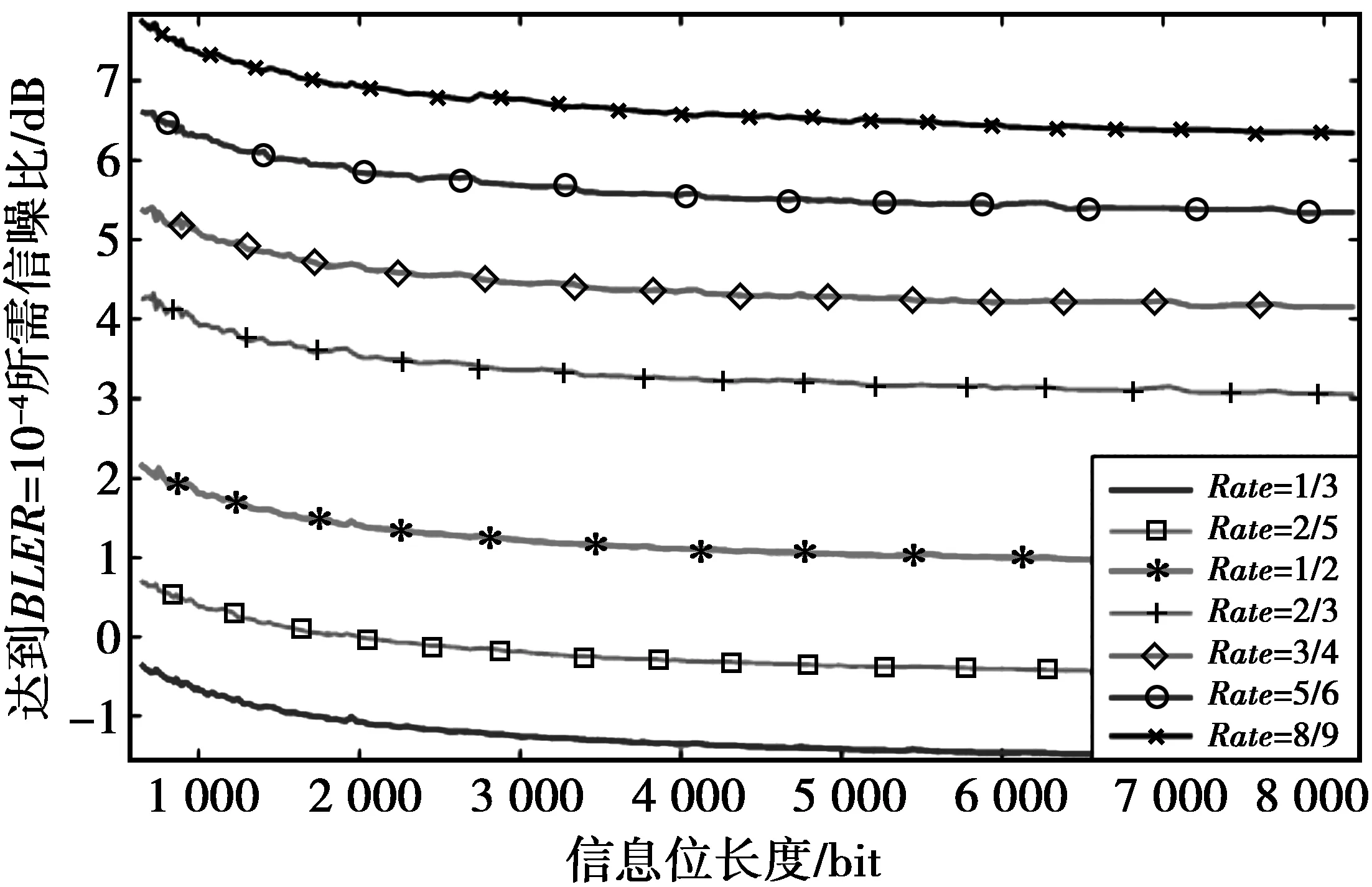

部分公司重点关注采用不同基图方案的LDPC码的性能差异。文献[57]中Huawei公司对采用Alt1a及Alt2基图方案的LDPC码性能分别进行评估,如图5所示。在误块率分别为10-2及10-4的条件下,Alt1a,Alt2基图方案得到的LDPC码误块率性能曲线平滑,无错误平层现象产生。此外,通过性能分析对比可知,在短信息块场景下,双基图方案能提供更优性能增益。

图5 误块率为10-4时的信噪比性能Fig.5 Performance of SNR at BLER=10-4

另一些公司则从硬件实现的角度对所提LDPC码进行性能分析,文献[58]中,Nokia等公司基于给定不同码率、译码算法及信息块长度的假设,对所设计的LDPC码进行性能评估,认为其所提短码块奇偶校验矩阵在较广的码率范围内性能优良,长码块奇偶校验矩阵能够提供较好的硬件实现增益。

6 结束语

针对5G中各类业务场景的性能需求,业界研究人员对LDPC信道编码技术开展研究,并已取得重要进展。本文在对LDPC码研究进行概述的基础上,对3GPP RAN1各次会议中业界针对LDPC码的标准化工作进行探讨,并从LDPC码设计、译码算法、速率匹配以及编码性能评估及对比等多方面进行总结阐述,以期对LDPC码后续标准化工作及理论研究提供基础支持。