Xilinx FPGA多bit文件加载方法研究及VHDL实现

2018-08-07中国空空导弹研究院樊宏伦

中国空空导弹研究院 樊宏伦

引言

FPGA(现场可编程门阵列)由于其资源丰富、设计周期短和风险小、使用灵活等优点,已广泛应用于信号处理和控制领域。FPGA大多采用SRAM工艺,掉电后内部配置数据丢失,再次上电后需要重新对其进行配置,因此在FPGA外部多采用非易失性存储器(称为FPGA的配置PROM或配置Flash)来存储配置数据以方便每次加电后对其进行自动配置。

在复杂系统设计中,如果系统所有功能都在一个bit文件来实现的话,器件资源可能不够用或裕量不足,FPGA会出现时序问题。我们可以将系统功能中相对独立的部分提取出来用另外的bit文件实现以解决上述问题,这就涉及到FPGA的多bit文件切换加载功能。

本文以Xilinx Virtex5 XC5VLX110T FPGA及其配置Flash XCF128X为例,介绍了一种FPGA多bit文件加载方法并进行了VHDL实现,试验证明该方法能可靠实现两个bit文件的切换加载, 为后续需要进行独立功能切换的应用提供了设计依据。

1.硬件设计

XCF128X是一款专门为Vitrex5系列FPGA配置设计的Flash,其采用低功耗CMOS NOR-Flash工艺,容量为128Mb。XC5VLX110T FPGA采用XCF128X作为配置Flash的电路如图1所示。本文以主SelectMap模式为例介绍FPGA的多bit文件切换加载功能,其它配置模式与此类似,不再赘述。在主SelectMap配置模式下地址总线23位、数据总线16位,配置时钟由FPGA的CCLK管脚提供,CCLK时钟频率可在ISE开发环境的配置选项中的“配置速率”(-g Con figRate)中进行设置。

图1 FPGA主SelectMap配置电路

需要注意:Flash的地址最高位A22连接到FPGA的RS1管脚上,并接1k上拉电阻;Flash的地址次高位A21连接到FPGA的RS0管脚上,并接1k下拉电阻。

XC5VLX110 FPGA的上电配置过程如下:

1)上电,FPGA清除内部配置存储器,将INIT_B管脚驱动为低电平(对应Flash的管脚为低进行复位);在复位时Flash将其RDY_WAIT管脚驱动为低电平(对应FPGA PROGRAM_B管脚为低);

2)FPGA和Flash分别释放各自的INIT_B管脚和RDY_WAIT管脚,外部上拉电阻将INIT_B和RDY_WAIT(PROGRAM_B)分别拉为高电平;

3)在INIT_B上升沿采样M2:M0管脚,确定其配置模式为主SelectMap配置模式;

4)Flash初始读地址由地址总线A[22:0]上的上下拉电阻确定为0x400000(即加载的bit文件首地址为Flash地址0x400000),Flash将初始读地址锁存到内部地址计数器,输出数据总线DQ[15:0]上的16位配置数据;

5)配置数据在CCLK时钟下被同步送到FPGA中,然后Flash增加其内部地址计数器,并输出数据总线DQ[15:0]上下一个16位置配置数据到FPGA,依次类推;

6)配置成功后,FPGA将Done信号驱动为高电平。

2.Flash文件准备

本文将两个实现不同功能的bit文件(bit1和bit2)分别存放在Flash地址0x000000和0x400000起始的地址空间内,XC5VLX110T FPGA的纯配置文件大小为31118848b(占用的字节地址空间为0x1DAD60),两个bit文件在Flash中存放的示意图如图2所示,需要注意的是生成的bit文件含有部分冗余头(bit生成时间,bit文件名等信息),因此占用的地址空间比纯配置文件要大,冗余头在生成mcs文件的过程中会被移除。

设置好地址后通过Xilinx iMPACT工具软件生成.mcs文件,然后使用JTAG下载器将mcs文件烧写到XCF128X Flash中,在烧写的时候需要注意,RS[1:0]需要选择地址22:21,如图3所示。

图2 bit文件地址空间占用示意图

图3 Flash烧写时RS选择示意图

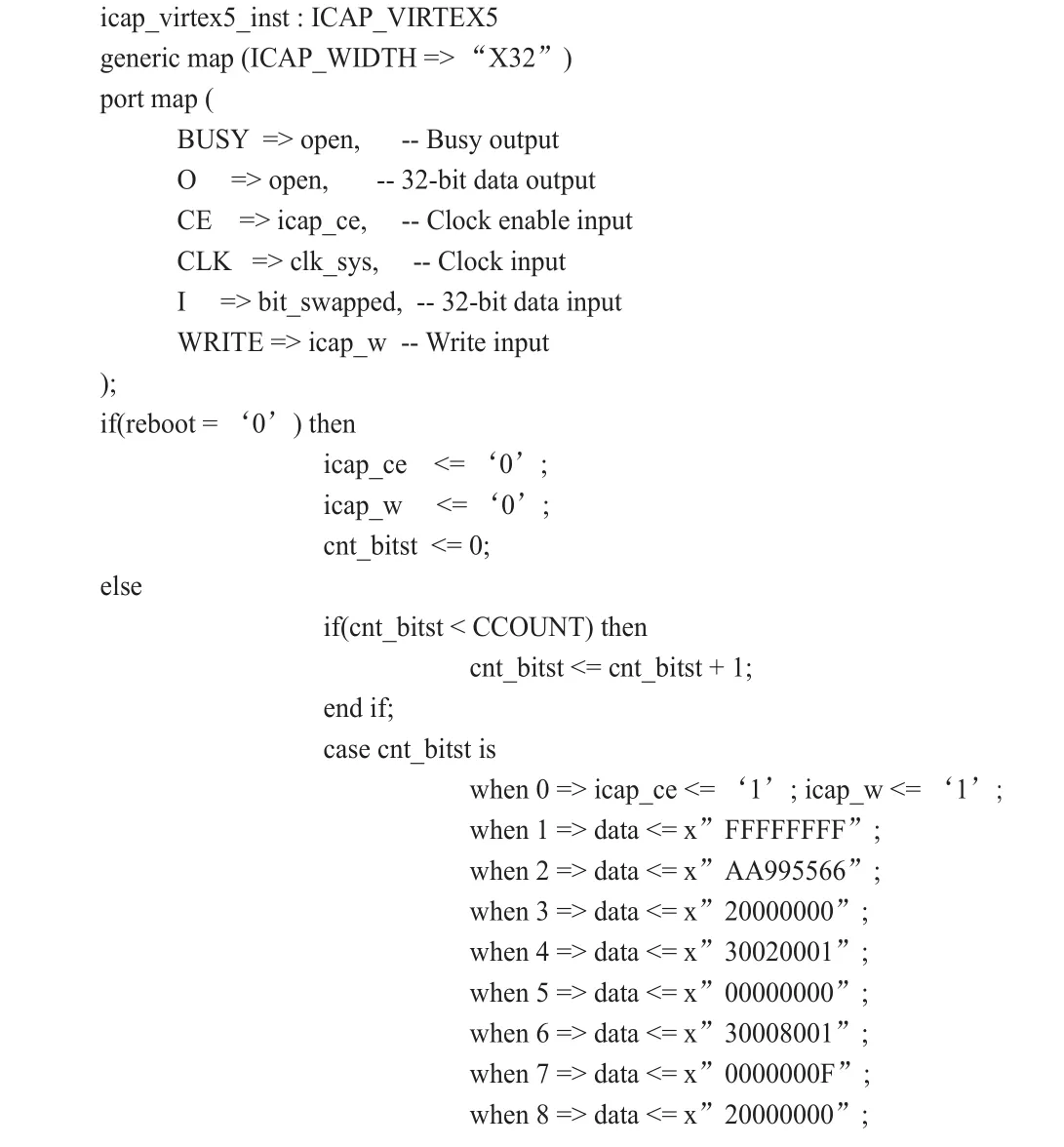

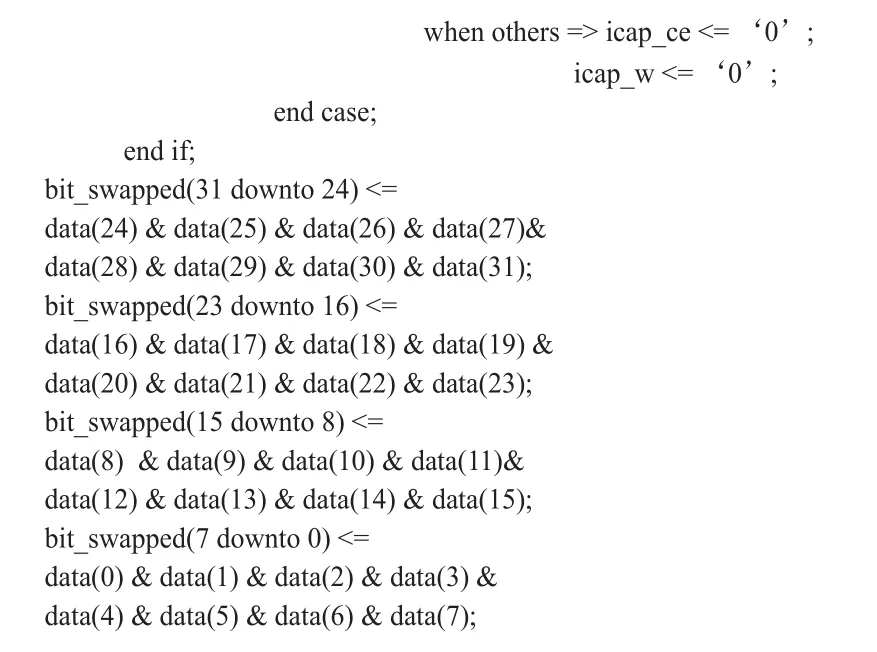

3.多bit文件切换加载VHDL实现

上电后,FPGA先从Flash地址0x400000将bit2文件加载,在bit2中可通过原语ICAP_VIRTEX5实现bit1文件的加载。VHDL的具体实现如下所示。

4.结论

本文以Xilinx Virtex5 XC5VLX110T FPGA及其配置Flash XCF128X为例,介绍了一种FPGA多bit文件加载方法并进行了VHDL实现,试验证明该方法能可靠实现两个bit文件的切换加载,为后续需要进行独立功能切换的应用提供了设计依据。