基于FPGA的中子发生器系统集成IC的设计方法与实现*

2018-03-15尹德有

张 伟 张 建 尹德有

(丹东东方测控技术股份有限公司)

现今随着电子技术的不断发展,现场编程门阵列(FPGA)的技术不断进步,其运算速度和存储空间都有了很大的提高,功能变得更加强大,而成本的不断减低,也使得FPGA的应用领域越来越广。

一般的FPGA的设计是根据外围设备编写不同的功能模块,这些模块结构设计不统一,接口设计多样化,不适合系统级整体设计,可重构性和可移植性差,使得产品开发周期大大增加。为此,提出的多模块化集成IC设计方法,具有通用的接口设计,方便的数据读写操作,能够很大程度上提高设计的可重构性和可移植性,减少产品的设计周期。

1 设计原理

在多模块集成IC设计原理中,最重要的是通用接口设计。如图1所示,在通用接口设计中,通过与上位机通讯,在FPGA接口模块中分配数据,确定上位机需要访问的器件地址、寄存器地址、读写方式、数据控制等,通过译码器与锁存器将数据发送给模块,实现多个模块的独立控制。

图1 设计结构框图

2 SPI通讯接口设计

采用SPI从机总线实现与上位机通讯,8位数据传输,连续4个8位数据,每8位数据代表一个地址,第一个8位数据为控制器器件地址和读写信号,第二个8位数据为器件寄存器地址,第三、四个8位数据是16位数据值,同时第三、四个8位数据也可以为读数据。SPI从机通讯模块见图2。

图2 SPI从机通讯模块

3 数据锁存和地址分配

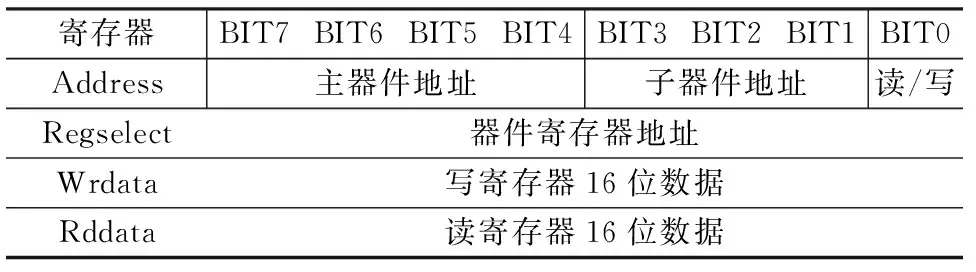

所有的数据包括地址数据Address,寄存器数据Regselect,写数据Wrdata,读数据Rddata都由锁存器74373锁存。Address地址高4位由74154译码器转换成16位主器件地址片选,BIT3~BIT1由74138译码器转换成8位子器件地址片选。即Address数据的地址可外接共16大类设备器件,每大类器件又可接8个相同模块。这样的地址设计方法也可以自行定义。接口说明见表1。

4 通用接口设计

模块集成IC设计是仿照传统集成芯片设计,其通用接口具有内部寄存器分配、片选接口、读写使能接口等。

表1 接口说明

(1)模块IC设计具有通用的传输接口,见表2。

表2 模块IC设计通用接口

(2)内部寄存器分配。内部寄存器分为控制寄存器和数据寄存器两种,并分配有不同的地址。控制寄存器用于使能模块和模块内部触发,中断等功能实现。数据寄存器则用于实现对系统外部设备数据的读写。这样设计,方便了对模块内部数据的检测,可以用于软件的调试。

(3)外设时序。针对不同的应用,每个外设的时序各不相同,在实现内部数据寄存器和控制寄存器的初始化后,按照基本的外设时序编写驱动功能。

5 FPGA软件设计

如图3所示4通道D/A接口模块,其中clk、rst接口为系统时钟和系统复位,模块的地址位0x30,是由Address地址数据经过译码器得到的,MA3代表主器件地址,SA0代表子器件地址,regvalue代表寄存器地址,读写信号由Address[0]确定,并通过非门形成互锁,datain[15..0]是数据输入,DA[15..0]是数据输出,其他是设备的接口。

图3 4通道D/A模块框图

FPGA通用接口设计软件如下:

∥写地址[1]

always @ (address)

begin

da1_value_reg_selected <= 0;

da2_value_reg_selected <= 0;

da3_value_reg_selected <= 0;

da4_value_reg_selected <= 0;

control_reg_selected <= 0;

case(address)

0:da1_value_reg_selected <= 1; ∥通道1电压输出

1:da2_value_reg_selected <= 1;∥通道2电压输出

2:da3_value_reg_selected <= 1;∥通道3电压输出

3:da4_value_reg_selected <= 1;∥通道4电压输出

4:control_reg_selected <= 1;∥控制寄存器

default:

begin

da1_value_reg_selected <= 0;

da2_value_reg_selected <= 0;

da3_value_reg_selected <= 0;

da4_value_reg_selected <= 0;

control_reg_selected <= 0;

end

endcase

end

∥写D/A通道电压输出数据

always @ (posedge clk or negedge reset_n)

begin

if(reset_n==1′b0)

begin

da1_value_reg=0;

da2_value_reg=0;

da3_value_reg=0;

da4_value_reg=0;

end

else

begin

if(write & !chipselect & da1_value_reg_selected)

begin

da1_value_reg <= writedata;

end

if(write & !chipselect & da2_value_reg_selected)

begin

da2_value_reg <= writedata;

end

if(write & !chipselect & da3_value_reg_selected)

begin

da3_value_reg <= writedata;

end

if(write & !chipselect & da4_value_reg_selected)

begin

da4_value_reg <= writedata;

end

end

end

∥写D/A控制寄存器值

always @ (posedge clk or negedge reset_n)

begin

if(reset_n==1'b0)

begin

control_reg = 0;

end

else

begin

if(write & !chipselect & control_reg_selected)

begin

control_reg <= writedata[0];∥使能

end

end

end

∥读数据

always @ (address or read or da1_value_reg_selected or

da2_value_reg_selected or da3_value_reg_selected or

da4_value_reg_selected or control_reg_selected)

∥always @ (posedge clk)

begin

if(read)

case(address)

0:readdata <= da1_value_reg;

1:readdata <= da2_value_reg;

2:readdata <= da3_value_reg;

3:readdata <= da4_value_reg;

4:readdata <= control_reg;

default:readdata<=16′h0000;

endcase

end

通用接口设计是所有外挂设备模块的重要部分,其他模块设计都可按照上述方法实现,这种设计方法高效简单,应用性强。设备接口驱动则按照不同模块的时序设计完成。

6 设计验证

在上述设计原理及软件结构的基础上,采用Altera公司FPGA,Cyclone E系列芯片EP4CE22,其逻辑单元22,320(LEs),嵌入式存储单元594(Kbits),本设计共8个大类,15个模块组成,包括SPI总结模块、LED模块、PWM模块、A/D模块、D/A模块等,约占80%的片上资源。通用接口modelsim仿真见图4,设备接口modelsim仿真见图5。

7 结 语

在FPGA设计中,多模块集成IC设计方法实现了将多个不用模块或多个相同模块的集成设计,每个模块具有通用的设计接口,简化了通讯接口设计,提高了模块的可移植性;灵活的地址分配设计,方便的多个模块的连接,形成了总线设备多元化设计;内部寄存器的设计,可以针对模块内部数据进行读写,方便调试。总之,多模块集成IC设计简化了模块接口设计,增加了软件设计的可重构性和可移植性,减少了产品设计开发周期。

图4 通用接口modelsim仿真

图5 设备接口modelsim仿真

[1] SANIR P.Verilog数字设计与综合[M].2版.北京:电子工业出版社,2009.