用于反熔丝型FPGA的多电平IO端口电路设计

2017-09-03蔺旭辉曹靓马金龙王栋

蔺旭辉,曹靓,马金龙,王栋

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

用于反熔丝型FPGA的多电平IO端口电路设计

蔺旭辉,曹靓,马金龙,王栋

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

设计了一种用于反熔丝型FPGA的多标准IO端口电路。通过端口电路,可将定义好的外部信号输入到FPGA内部用来实现用户需要的逻辑功能,并且将所需的内部信号输出到外部引脚。端口电路也实现芯片内部工作电平和外部工作电平之间的相互转换,驱动外部芯片,以及实现对电路功能的测试。用户在使用FPGA的过程中,可以根据实际需求来配置以实现不同的电平标准。每一个IO端口可以配置成输入、输出、三态输出或者双向输入输出。

反熔丝;FPGA;IO标准

1 引言

现场可编程门阵列FPGA(Field Programmable Gate Array)作为专用集成电路(ASIC)领域中的一种半定制电路,因其集成度高、灵活性强、开发成本低、开发周期短、风险低、可靠性高,在系统自主开发设计领域已逐步取代ASIC电路。目前,根据内部结构原理分类,主要存在SRAM型、反熔丝型和Flash型三种类型的FPGA。由于反熔丝单元结构的特异性,使得反熔丝型FPGA在编程、使用过程中具备了读取速度快、功耗低、应用温度范围广、抗辐射能力强、安全、保密性高等优势,被广泛应用于航天、航空、军事等高可靠性和复杂环境领域。

在反熔丝型FPGA领域,ACTEL公司是杰出领导者,其推出的多系列多款反熔丝FPGA产品已经被广泛应用于航空航天等复杂环境领域,性能和可靠性得到了全面验证[1]。本文是参考与借鉴ACTEL公司反熔丝FPGA的相关设计经验,设计了可适用于自主设计反熔丝FPGA多电平标准的IO端口电路。

2 IO端口电路结构设计

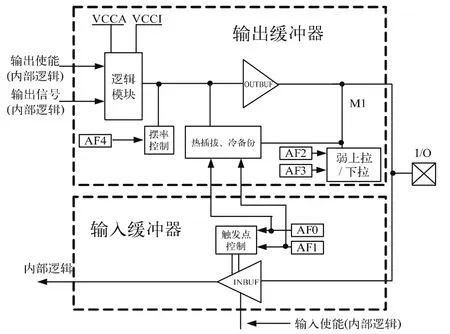

IO端口模块提供FPGA外部引脚与内部可编程逻辑资源的接口,芯片每一个通用输入/输出引脚对应一个IO,可实现FPGA电路内外信号的转换。主要由输入缓冲器和输出缓冲器两部分组成。可以配置成输入、输出、三态输出输入缓冲器,包括INBUF电路和触发点控制电路;输出缓冲器主要包括逻辑模块、OUTBUF电路、摆率控制、热插拔冷备份,以及弱上拉/下拉电路。其整体电路的功能框图如图1所示[1]。

图1 IO端口模块功能框图

3 多标准IO电路模块的实现

反熔丝型FPGA通过IO电路,为内部可编程逻辑电路提供输出驱动能力和输入驱动能力,如果没有IO电路,FPGA电路只输出一个电压标准,并且不能满足外部驱动能力的要求。随着FPGA规模的不断变大,所兼容的IO标准数量越多[2]。对于多标准接口,就是不同的接口标准对输出电压和输出电流的大小的要求不同,同时输入高低电平和输入的电流大小也不相同。为了满足不同种类的IO标准,FPGA多标准IO接口模块设计为接口转换电路,根据接口协议的电气参数特性的不同,完成FPGA内部信号与外部信号的转换。

3.1 输入缓冲器

通过输入缓冲器,可将芯片外部信号输入到芯片内部,接收的输入电平包括5 V CMOS、5 V PCI、5 V TTL、3.3 V PCI、3.3 V LVTTL五种电平标准,此功能的实现由触发点控制电路与INBUF电路结合一起完成。

INBUF模块包括使能控制电路,要求将来自芯片内部电平为VCCA的使能信号转换成电平为外部电平为VCCI的信号。INBUF电路要实现阈值可调,可以设计多条上拉支路或者多条下拉支路,并通过选择不同的支路开启与否,支路的选择由触发点控制电路实现。电路原理图如图2所示。

图2 输入缓冲器

电路中AF0、AF1是反熔丝配置信号,触发点控制电路是一个译码电路,将AF0、AF1信号转换成三个控制信号AF_TP1、AF_TP2和AF_TP3,这三个信号控制电路中的1、2、3、4支路的开启。表1给出了AF0、AF1不同组合下的工作支路,以不同的组合来实现不同的电平标准[3]。

表1 AF0、AF1对应的工作支路

使能控制电路,将来自芯片内部的幅值为VCCA的逻辑信号转换成幅值为VCCI的信号,控制输入缓冲器的工作。电路结构如图3所示。

图3 使能控制电路

输入缓冲器功能仿真:当使能信号为高电平时,输入缓冲器正常工作,使能信号为低电平时输入缓冲器输出高电平。仿真结果见图4,结果符合要求。

输入阈值仿真:分别对5种电平模式进行仿真,这里只列出了3.3 V PCI电平模式下的仿真波形,如图5所示。其他模式的仿真结果如表2所示。

仿真结果分析:可以看到每一种模式的设计值都要比规定值大,这是考虑到电路的应用环境,辐射总计量会减小NMOS的阈值电压,增大PMOS的阈值电压,所以这样设计是合理的。

图4 输入缓冲器功能仿真

图5 3.3 V PCI阈值仿真

3.2 输出缓冲器

输出缓冲器:将芯片内部逻辑传递到芯片外部,可输出的电平包括5 V CMOS、5 V PCI、5 V TTL、3.3 V PCI、3.3 V LVTTL,具有热插拔、冷备份以及5 V tolerant功能的选择性配置。在3.3 V PCI模式下不具备此功能,其他模式下具备此功能,由热插拔冷备份模块结合OUTBUF一起实现。具有输出摆率可调功能,由摆率控制模块实现。弱上拉/下拉模块在芯片内部上电过程中为输出端口提供一个可知的电平。

表2 仿真结果

PART_1:使能电路,配置信号OEJ和寄存器信号OEN控制OUTBUF的工作。

PART_2:电平转换,摆率调节,以及电荷泵信号控制输出状态。

PART_3和PART_4:热插拔、冷备份功能。

PART_5:弱上拉/下拉电阻电路。

图6 输出缓冲电路原理图

输出功能仿真:使能信号为高时,电路正常工作,使能为低时,电路输出低电平。当摆率控制信号为高时,输出的下降沿为高摆率,否则为低摆率。仿真结果如图7所示,符合要求。

冷备份功能仿真:冷备份仿真时,要求电源VCCI接地,PAD信号为正常波形,要求在PAD信号为高时,不存在大电流。仿真结果如图8所示,功能正常。

弱上拉/下拉电阻仿真:在芯片内核上电过程中,在输出PAD可以配置成高电平或低电平。要求弱上拉/下拉电阻在50 kΩ左右。电阻的仿真值如表3所示。

图7 输出功能仿真

图8 冷备份功能仿真

表3 弱上拉/下拉电阻值仿真

4 结束语

文章在研究分析国外主流FPGA多标准IO电路模块的架构和功能的基础上,设计了一种适用于自主正向反熔丝FPGA电路的多标准IO电路,使用设计、仿真工具对电路进行功能和时序上的仿真验证,然后经过优化设计。仿真结果显示,IO模块在各个电平模式下功能正常,参数符合要求。此电路的设计为后续设计大规模反熔丝FPGA多标准IO电路积累了经验。

[1]朱明程,熊元姣.ACTEL数字系统现场集成技术[M].北京:清华大学出版社,2004:7.

[2]杨常雷,朱明程.新型FPGA的I/O接口原理及关键技术[J].中国集成电路,2005,(05):40-43.

[3]郭滨.FPGA中的多标准IO端口设计[J].微处理机,2015, (1):7-9.

Design of Multi-Level IO Ports for Antifuse FPGA

LIN Xuhui,CAO Liang,MA Jinlong,WANG Dong

(China Electronics Technology Croup Corporation No.58 Research Institute,Wuxi 214072,China)

In the article,a multi-level IO ports module for antifuse FPGA is designed.Bu using the IO ports user defined signal is imported to realize expected function and the internal signal is exported to external pin.IO portsmodule also enables the conversion between internal voltage and the external,drives the external chip,and tests function of the FPGA.Level standards can be configured to meet specific needs.Each IO structure on FPGA can be configured asan input,output,tri-state outputor bidirectionalpin.

antifuse;FPGA;IOstandard

TN402

A

1681-1070(2017)08-0013-03

蔺旭辉(1990—),男,毕业于兰州大学,现主要从事于超大规模集成电路、反熔丝型FPGA等方向的研究和设计工作。

2017-3-31