基于PXI高速多通道AD采集卡的设计

2017-07-12刘亚斌张秀磊

伍 伟,刘亚斌,张秀磊

(北京航空航天大学 北京 100191)

基于PXI高速多通道AD采集卡的设计

伍 伟,刘亚斌,张秀磊

(北京航空航天大学 北京 100191)

为了实现高采样率、高精度的数据采集系统,介绍了一种基于FPGA和PXI总线的高速、4通道的并行数据采集系统的结构及实现。采用CycloneⅢ系列的EP3C40F484C8N作为控制器,ADI公司的AD9248作为模数转换器(ADC),PXI总线传输数据。设计了数据采集系统的硬件电路,包括4路AD采集电路,FPGA控制电路,PXI接口电路等,实现了对4路AD信号的并行采集。实际应用表明,该系统集成度高,抗干扰能力强,采集精确,性价比良好,达到了设计要求。

高速并行数据采集;FPGA;PXI;ADC

随着微电子技术的不断发展,数据采集系统在通信、网络、雷达系统等领域得到了广泛应用,由模拟系统向数字系统转变,A/D转换的多路扩展、高精度、低成本实时性显著等特点在ADC系统中越来越重要[1]。对于高速(采样速率≥1 MSPS)、高精度、多通道的数据采集问题要么难以实现,要么成本高,从而得到普遍应用比较困难。一般的信号采集系统,通常由单片机和DSP对A/D转换进行控制,单片机一般适用于低速数据中。DSP有高速的数据处理能力,而且接口灵活,通信能力强,在许多实际系统中得到应用,但是DSP存在易受干扰的弱点,而FPGA可以克服上述单片机跟DSP的缺点[2],FPGA内部可嵌软核,增强系统的数据处理能力;FPGA还具有时钟频率高、运行速度快、编程配置灵活、功耗低、设计费用低等诸多优势。FPGA集采样控制、数据处理、缓存、传输于一身,大大提高了系统的可靠性,降低了成本。

文中设计了一种基于FPGA和PXI总线的高速采集系统[3-6]。采用FPGA作为主控制器来实现对AD的控制,将ADC转换的数字信号存储到SRAM中,以实现对数据的方便读取和进一步的操作。处理后的数据送入PXI总线芯片中,最后经由PXI总线传输给上位机。

1 板卡总体设计

数据采集板卡的功能实现主要由前端信号调理模块[6-7]、14位的AD9248转换模块、FPGA控制模块及SDRM存储模块(如图1所示),其中心控制单元是ALTERA的CycloneⅢEP3C40F484C8N,它控制着数据的转换、存储、读取等过程。PLX公司的PCI9054是总线接口芯片,可以实现总线接口的控制,完成与上位机的数据传输。

图1 板卡总体结构图

2 高速AD采集电路设计

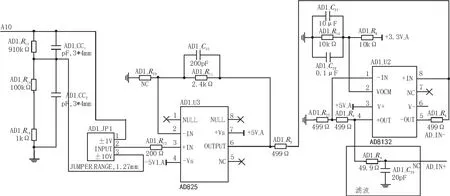

AD采集电路由前端信号调理部分和AD转换[7-9]部分组成。前端调理电路由高速运放器和模拟量驱动电路组成,模拟量输入经由大输入阻抗的高速运放器AD825放大送入高速差分运放器AD8132,为AD9248提供差分输入 (如图2所示)。选用AD825作为最前端模拟量输入的运放器是因为AD825的输入阻抗很大,相当于开路,与分压电阻并联之后等效电阻基本跟分压电阻阻值一样,这样可以保证精确的模拟量输入。再通过高速差分运放器AD8132放大驱动由单端变差分送入A/D转换器AD9248。

图2 前端信号调理电路

FPGA本身不具有AD采集功能,因此在FPGA控制电路之前必须有A/D转换电路把模拟量转化成可处理的数字量[10-12]。本文根据系统性能要求选用AD9248作为AD转换芯片。AD9248是一款双通道、14位、低功耗的逐次逼近型ADC,采用3 V单电源供电,具有20/40/65MSPS可选吞吐速率。AD9248采用先进技术,在高吞吐速率的情况下实现极低的功耗。在3 V电源供电下,吞吐量20MSPS时,典型功耗180 mW;吞吐量40 MSPS时,典型功耗330 mW;吞吐量60 MSPS时,典型功耗600 mW。

AD9248组成如图3所示,AD9248是一种基于流水线型的ADC,这种流水线型结构的特点是由一系列标志1级、2级等各级构成。每级的结构是相同的,包含一个采样保持电路(S/H)、一个子模数转换电路(ADC)和一个乘积数模转换器(MDAC)电路。AD9248的主要引脚的功能包括:VIN+、VIN-是模拟差分信号输入端;D0~D13是数据输出端;OEA、OEB分别是 A、B两通道数据输出使能位;PDWN_A、PDWN_B分别是两通道的Power-Down功能选择位,为0时,使能通道,为1时,关闭通道;DFS是输出数据格式选择位,为0时,数据输出格式为偏移的二进制,为1时,数据输出格式为二进制补码格式;OTR_A、OTR_B是两通道的溢出标志位;MUX_SELECT是数据复用模式选择位,该管脚接高电平时,则可保证两通道数据分别从各自通道输出,该管脚接时钟时,两通道数据将复用输出数据端口,此时数据输出速率是采样速率的两倍。

3 FPGA控制模块

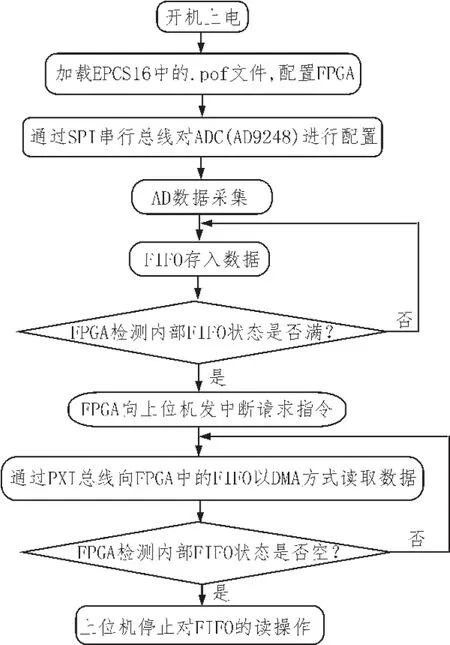

FPGA采用自顶向下的方法,模块设计采用Verilog语言编写[13-15]。当上位机启动数据采集后,FPGA通过SPI总线对AD9248进行初始化配置;当FIFO存储达到满(wrfull)状态时,PFGA产生一个低电平的外部中断请求信号,上位机响应中断后通过PXI总线读取FIFO中数据[16];当FPGA收到FIFO输出空(rdempty)信号后,再次通过PXI总线向上位机产生中断请求信号,响应中断后上位机查询中断源,检测到FIFO为空信号后,上位机停止通过总线读取FIFO数据,完成一次AD采集任务[17]。当完成一次采集后,上位机给FPGA写入复位信号,从而FPGA停止对AD9248的配置,这样AD转换过程也中止,控制过程如图4。

图3 AD9248组成

图4 FPGA模块控制流程图

4 实验测试及应用

在实验测试之前搭建实验平台,而该采集系统正要应用于某研究所的实际项目--舵机性能[18]评估测试系统,因此实验平台可以在此基础上搭建。用泰克的信号发生器作为模拟信号源。如图5所示。

图5 实验平台

信号发生器产生峰值为3 V,频率为200 kHz的正弦波信号作为输入信号,上位机设置AD采集卡为单个通道采集且采样频率为20 M/S。AD采集卡得到的数据上传给上位机,上位机把采样的点描绘成图像,如图 6,7。

图6 上位机采集的波形

图7 采集波形放大

可以看出上位机采集到的数据点描绘成图形与信号发生器的波形一致,图形横坐标表示采样点的个数,可以看出此波形一个周期AD采集卡供采集了100个数据点,满足输入波形200 kHz,采样频率20 MHz的关系。应用本文设计的AD采集卡完全可以达到采样速率为40 M/S,而且可以4个通道同时独立的采集数据,完全满足项目要求的高速AD采集的速率和精度的要求,此系统已经应用于实际工程项目。

5 结束语

该测试系统实现了高速、高精度以及连续采样,本文设计了一个基于PXI总线,以FPGA为控制核心的高速数据采集系统,该系统分为上位机和高速AD采集板卡部分[19]。文中硬件板卡的各个部分的硬件设计以及FPGA程序设计,同时基于项目搭建了实验平台进行实验测试。测试数据表明了软硬件设计的合理性和实用性。该测试系统已用于某型舵机的性能评估测试系统的工程项目,实际应用表明该测试系统具有测试准确、稳定可靠、人机界面友好等特点,达到了设计要求。

[1]郭云飞,赵冬娥,张斌.基于FPGA的高速AD采集设计[J].山西电子技术,2013(5):37-39.

[2]杨晓慧,杨旭.FPGA系统设计与实例[M].北京:人民邮电出版社,2010.

[3]EDA先锋工作室,王诚,蔡海宁.Altera FPGA/CPLD设计(基础篇)[M].北京:人民邮电出版社,2011.

[4]EDA先锋工作室,王诚,蔡海宁.Altera FPGA/CPLD设计(高级篇)[M].北京:人民邮电出版社,2015.

[5]覃春淼,王鑫,陈业伟,等.高速多通道并行AD采集卡的设计[J].计算机测量与控制,2014,22(12):4107-4110.

[6]黄现.基于PXI平台的FPGA高速自动化测试系统设计[D].上海:复旦大学,2012.

[7]Eric Bogatin.信号完整性与电源完整性分析[M].李玉山,刘洋,译.北京:电子工业出版社,2014.

[8]甘学温,赵宝瑛,陈中建,等.集成电路原理与设计[M].北京:北京大学出版社,2011.

[9]王祥.信号完整性在高速PCB设计中的应用[D].上海:复旦大学,2013.

[10]樊敏.高速AD接口技术—高速AD采集的设计与实现[J].科技创新导报,2015(5):41.

[11]吴越,严济鸿,何子述.多模式高速数据采集系统设计与实现[J].仪表技术与传感器,2013(3):50-53.

[12]李念强.数据采集技术及系统设计[M].北京:机械工业出版社,2013.

[13]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天出版社,2012.

[14]吴厚航.深入浅出玩转FPGA[M].北京:北京航空航天大学出版社,2012.

[15]刘轩.基于FPGA的多通道高速数据采集系统设计[D].北京:北京理工大学,2013.

[16]刘小杰,杜永清,张鹤平,等.基于LabVIEW与PLC的烧嘴试验台测控系统设计[J].火箭推进,2015(1):108.

[17]邱进.一种应用于多断口光控真空断路器的同步控制系统的设计与实现 [J].供用电,2015(5):69-73.

[18]刘占一,张魏静,杨建文,等.关键间隙对泵性能影响的研究[J].火箭推进,2015(1):56.

[19]张国飞,崔志胜,徐广鑫,等.基于瞬时无功功率理论的APF谐波补偿能力的仿真研究[J].陕西电力,2012(11):77-81.

Design of the high-speed and multi-channel parallel AD acquisition card based on PXI

WU Wei,LIU Ya-bin,ZHANG Xiu-lei

(Beihang University, Beijing 100191, China)

The construction and techno-realization of high-sample rate and high-accuracy data acquisition card are presented.The EP3C40F484C8N of CycloneⅢSeries FPGA is adopted to realize the design of high-speed and 4 channels hardware circuit,which includes 4 channels high-speed AD acquisition circuit(AD9248 is adopted to realize Analog to digital conversion ), PXI interface circuit, FPGA control circuit etc.The experimental result shows system has high integration degree,strong anti-interference ability, accurate acquisition and good performance, and meets the design requirements.

high-speed parallel data acquisition; FPGA; PXI; ADC

TN4

A

1674-6236(2017)12-0178-04

2016-05-02稿件编号:201605014

伍 伟(1990—),男,湖南冷水江人,硕士。研究方向:控制工程、嵌入式系统开发。