一种降抖动的位同步环路设计与实现

2017-07-12张盼,钟升,张琦,杨恒

张 盼,钟 升,张 琦,杨 恒

(1.西安微电子技术研究所 陕西 西安710054;2.西安通信学院 陕西 西安 710106)

一种降抖动的位同步环路设计与实现

张 盼1,钟 升1,张 琦1,杨 恒2

(1.西安微电子技术研究所 陕西 西安710054;2.西安通信学院 陕西 西安 710106)

针对通信系统中位定时环路自噪声过大的问题,改进了传统Gardner位同步环路,采用改进型Gardner算法与PSO算法优化的预滤波器相结合的方式,从定时误差检测和波形预处理两方面有效抑制了环路的定时误差抖动,提升了环路收敛速度。通过算法仿真,验证了该改进环路的正确性和有效性;通过FPGA验证,表明了该环路的可实现性和良好的工程应用价值。

位同步环路;改进型Gardner算法;PSO算法;定时误差抖动;FPGA

在数字通信系统中,为了实现正确的数据通信任务,需要实现多种同步功能。位同步是同步系统的关键,其质量的好坏直接影响整个通信系统的性能。因此,关于位同步的研究和算法层出不穷,其中Gardner算法[1]具有不受载波相偏影响、实现简单等优点,在数字同步通信系统中被广泛应用。然而传统Gardner算法的定时误差检测在环路收敛后仍存在较大的自噪声,造成定时误差抖动较大[2],继Gardner后的国内外学者提出了很多改进方法,主要分为两大类,算法改进类[3]和波形预处理类[4]。文中采用粒子群算法[5]和误差检测算法相结合的改进方案,有效抑制了传统环路自噪声较大的缺陷,明显减小了定时误差抖动,大大改善了位同步系统的性能。

1 传统位同步环路

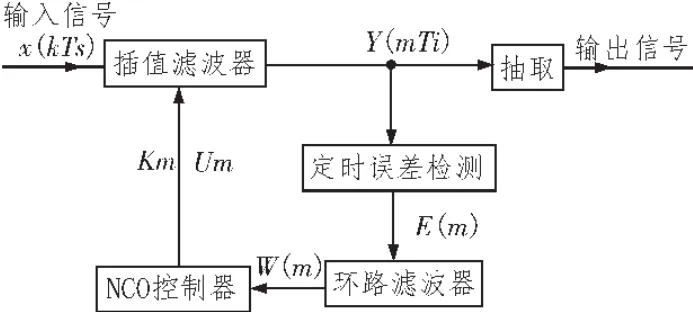

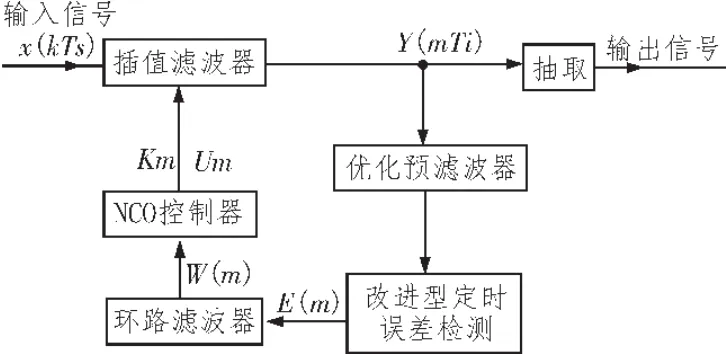

传统位同步环路采用数字锁相环[6]结构,包括内插滤波器、定时误差检测、环路滤波器和数控振荡器4个部分,其结构框图如图1所示。

图1 传统Gardner位同步环路结构框图

如图1所示,定时误差检测器估算出第m点信号经过插值滤波器输出的信号Y(mTi)的误差E(m),然后送入环路滤波器,去除干扰后,提取出平稳分量W(m),接着送入到NCO控制单元,产生内插基Km点和小数间隔Um,最后插值滤波器根据两个控制量进行插值运算调整m+1点的定时相位及频率的偏差,不断进行反馈调节,最终达到稳定。各模块设计详见文献[7-9]。

传统Gardner算法的定时误差检测为:

y(m)表示第 m 个码元值,y(m-1/2)表示位于第m个码元和第(m-1)个码元的中间时刻的样点值。该方法中定时误差检测是通过前后两个码元的样点极性差值来调整定时的方向,两个码元中间时刻的样点的值的大小来体现调整误差的大小。

传统Gardner位同步环路的定时误差时钟是固定的且是独立于码元周期的,由于其不需要反馈控制采样时钟,适合于高码率及多种调制方式的位同步。但是由于环路收敛后定时误差检测器仍存在较大的自噪声,将引起定时误差抖动,影响环路的稳定性,本文针对该问题,提出了改进方案,以减小定时误差抖动,提高环路的稳定性。

2 位同步环路的改进方案

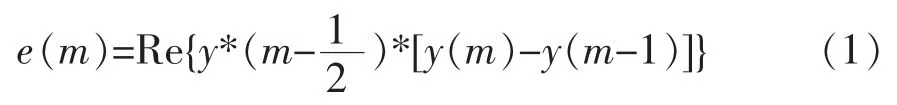

为了进一步降低定时误差对系统性能的影响,本文对传统环路进行了改进,其改进型环路结构如图2所示。

图2 改进位同步环路结构

如图2所示,文中采用改进型Gardner定时误差检测算法和优化预滤波相结合的位同步环路,从两方面更加有效的抑制环路噪声,提升环路的同步性能。

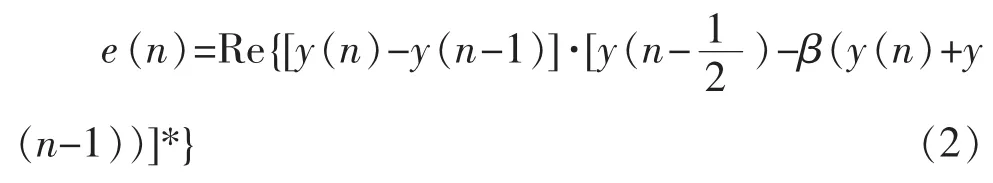

信号受到信道影响后,若存在相邻符号跳变,即使采样正确,其误差检测的输出也不为0,如文献[10]中所示,改进型Gardner定时误差检测输出可表示为:

应用改进型算法虽然在一定程度上降低了环路自噪声对信号的影响,但是由于只依靠环路滤波器滤除噪声能力有限,效果并不是很明显,很多学者提出了对信号进行波形预处理,即在定时误差检测前先对信号进行预滤波,以更有效地滤除环路自噪声,提升环路性能。传统FIR滤波器设计通常采用窗函数法和频率采样法,前者计算简单但不能较好折衷过渡带与幅频响应误差间的矛盾,后者从频域处理原理简单,但不易精确确定其阻带和通带的边界频率且使用传统查表法,不能保证数据最优[11]。为了更好地改善滤波器性能,文中采用计算量小,易于实现的粒子群优化算法设计滤波器,该算法通过搜寻使适应度函数最小的情况来得到最优滤波器,以更好的滤除绝大部分的带外噪声。

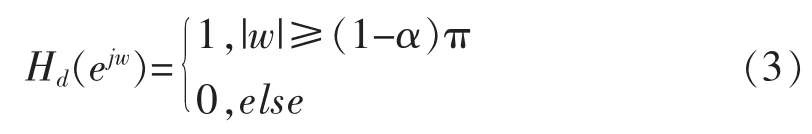

由文献[12]可知,定时误差检测器输出在频带-(1-α)π≤w≤(1-α)π 不存在定时误差信息,该部分为带外噪声,为了减少定时误差抖动方差,可在误差检测前加入高通滤波器,滤除不携带定时误差信息的噪声部分,减小定时误差抖动。则该滤波器理想的幅频响应为:

设N阶FIR滤波器的频率响应为:

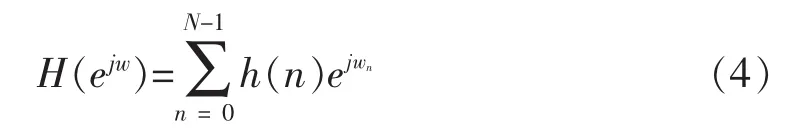

粒子群优化算法通过适应度来确定当前粒子位置的优劣性,搜寻全局最优解[13],若设FIR滤波器的理想频率响应为 Hd(ejw),则所设计的滤波器为 Hd(ejw)与理想滤波器的误差平方和为适应度函数F,则

由上式可知 F 函数是以滤波器系数 h(0),h(1),…h(N-1)为N个未知量的函数,实际滤波器的设计即是选取最优的滤波器系数值使目标函数F最小。

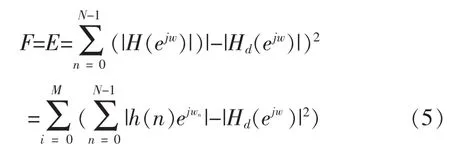

对于应用PSO算法求解hi,我们以hi表示当前粒子的位置,以vi表示对应的速度,来进行编码,按照下式来更新速度与位置:

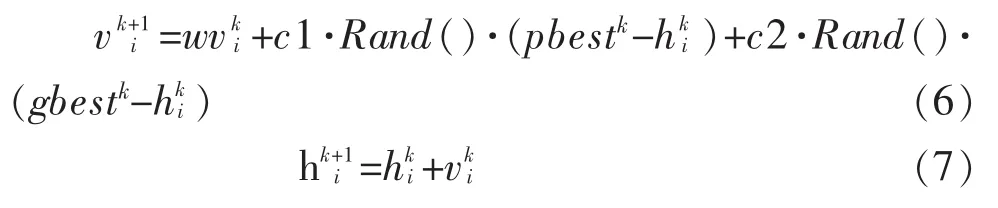

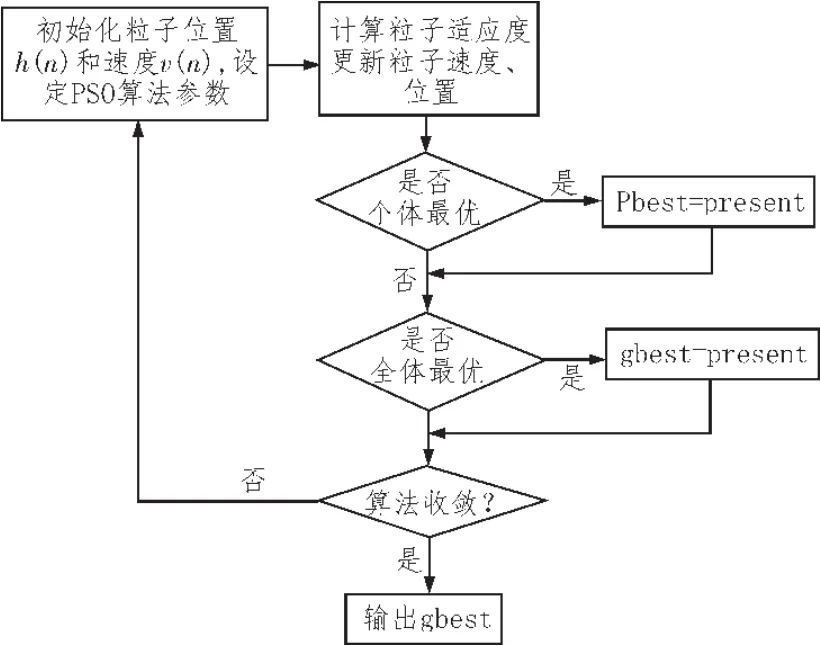

其中k代表迭代次数,w表示惯性权重,pbest表示个体最优,gbest表示全体最优解,c1,c2为加速常数,它们使粒子向pbest和gbest位置运动,Rand()表示(-1,1)的随机数,vi受 vmax限制。 算法流程如图3所示,最终输出的gbest即为FIR滤波器系数的最优解[14]。

图3 PSO算法流程图

文中采用PSO算法进行FIR数字滤波器优化设计,参数设置如下:群体大小为100,参数维数为5,最大惯性权重为0.9,最小权重为0.4,最大速度为1,最大迭代次数为 1000,c1=c2=1.494 45。通过Matlab仿真搜寻得到优化的滤波器系数。

3 算法验证与性能评析

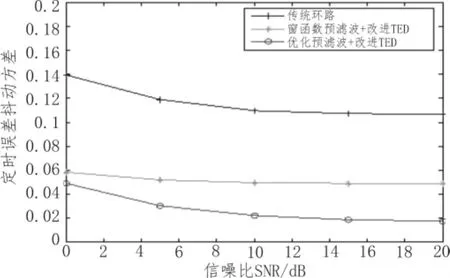

利用Matlab 2012a软件对改进型Gardner定时误差检测算法进行仿真,系统参数如下:高斯白噪声信道下,符号速率为2 MHz,收发端滚降系数为0.35,载波频偏为3 kHz。图4为传统位同步环路和改进位同步环路在不同信噪比下的定时误差方差抖动方差曲线图。图5环路改进前后定时误差输出曲线和NCO输出小数间隔uk收敛曲线对比图如图4所示。

图4 定时误差抖动方差曲线

图4横轴表示信噪比,纵轴表示环路定时误差的方差,由图可以看出传统环路随着信噪比的减小,定时误差抖动增加的最快,而窗函数预滤波、优化预滤波与改进TED相结合的环路相对来说受信噪比影响较小,并且优化预滤波环路定时误差方差相对于窗函数预滤波的环路定时误差方差减小约90%。即说明在较低信噪比的情况下,优化预滤波和改进TED结合的方案仍然可以有效完成位同步功能。

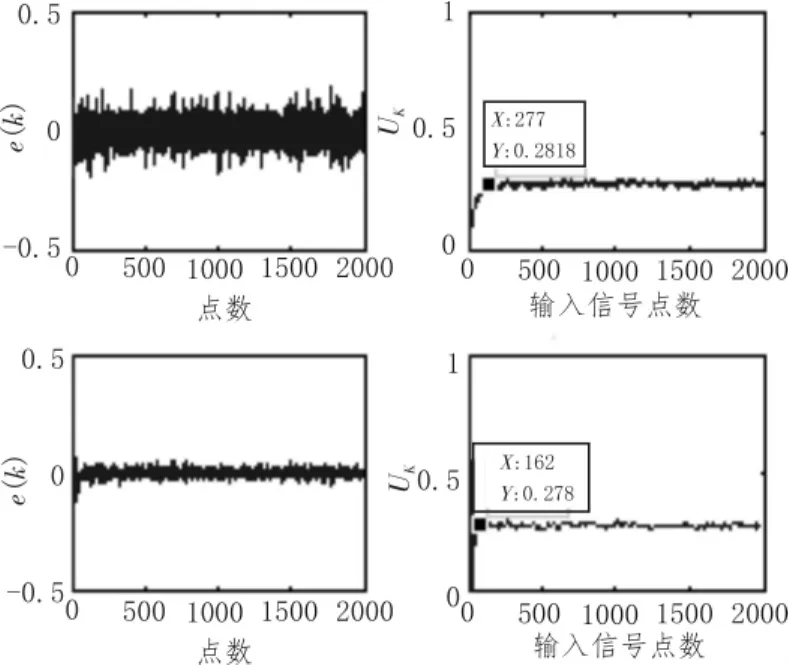

图5 改进前后位同步环路仿真结果图

图5中横坐标表示输入信号点个数,左图纵坐标表示环路输出的定时误差幅度,右图纵坐标表示环路输出小数间隔。由上图可知,传统环路和改进环路的定时误差输出值分别在 [-0.2,02],[-0.04,0.04]范围内,传统位定时环路在277点左右收敛,而改进后环路在162点左右收敛且抖动更小。

综上所述,相较于传统Gardner位同步环路,改进环路定时误差抖动幅度约减小为原来的1/5,环路达到收敛所需点数更少且抖动较小,提升了整个系统的稳定性和准确性,利于后续的恢复与判决。

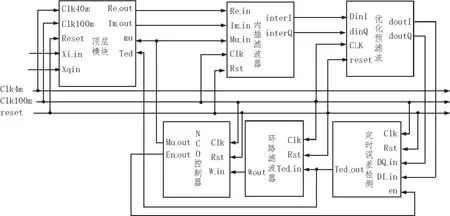

4 FPGA验证

基于Xilinx的Virtex5系列芯片在其配套的ISE开发环境上用VHDL语言[15]进行设计实现。改进位同步环路的FPGA逻辑结构如图6所示,各模块联系如下:NCO控制器产生内插基点间隔,进入插值滤波器模块对输入信号进行插值,计算出正确的内插点,其结果进入优化预滤波模块进行消减噪声后进入定时误差检测模块TED,估计出相应的定时误差经环路滤波器LF平滑滤波后去控制振荡器输出,系统如此循环并不断的进行反馈调节。

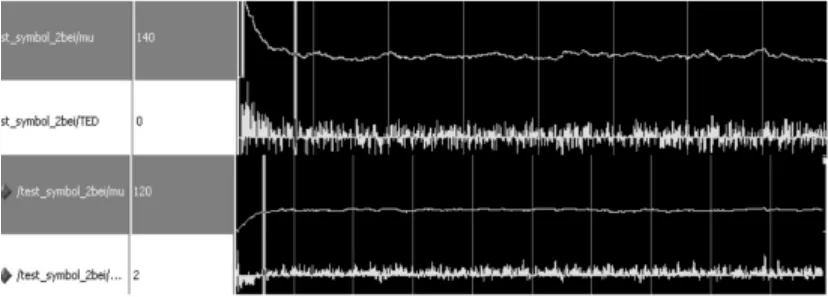

经综合实现后,应用Modelsim软件对上述方案进行功能仿真,其仿真结果如图7所示。

图7中从上到下依次为传统环路收敛曲线、定时误差输出曲线,改进环路环路收敛曲线、定时误差输出曲线,由图可知传统环路在76.6 μs处于收敛状态,其定时误差输出幅度在[-220,220]范围内,改进环路在49.6 μs进入收敛状态,其定时误差输出幅度在[-40,40]范围内。改进环路相较于传统环路定时误差幅度减小为原累的1/5且收敛速度有所提升,与MATLAB仿真结果一致,表明了该环路算法的有效性。综上所述,改进位同步环路显著减小了定时误差幅度,提升了环路收敛速度。

图6 改进位同步环的FPGA逻辑框图

图7 不同位同步环路调整误差和定时误差曲线

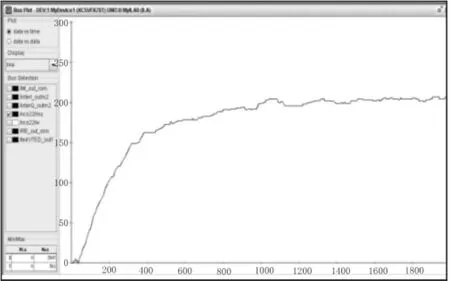

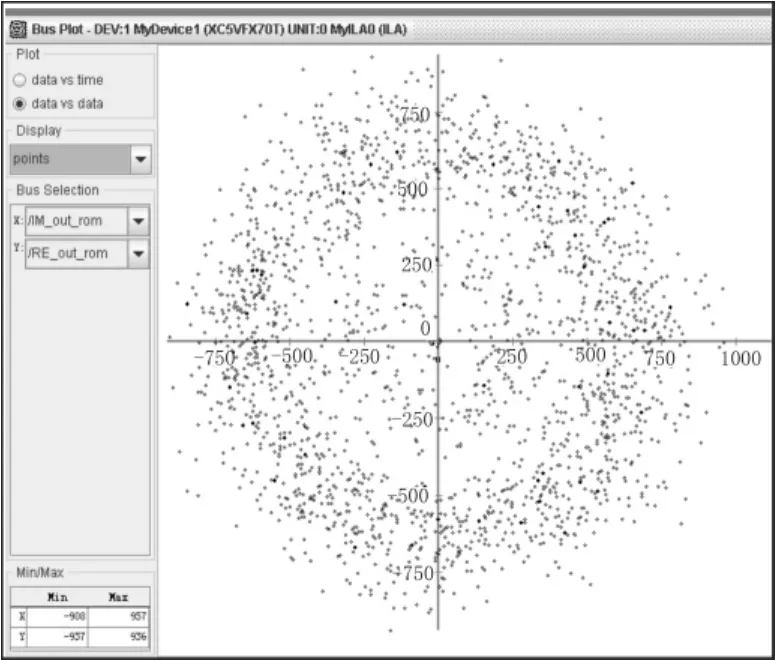

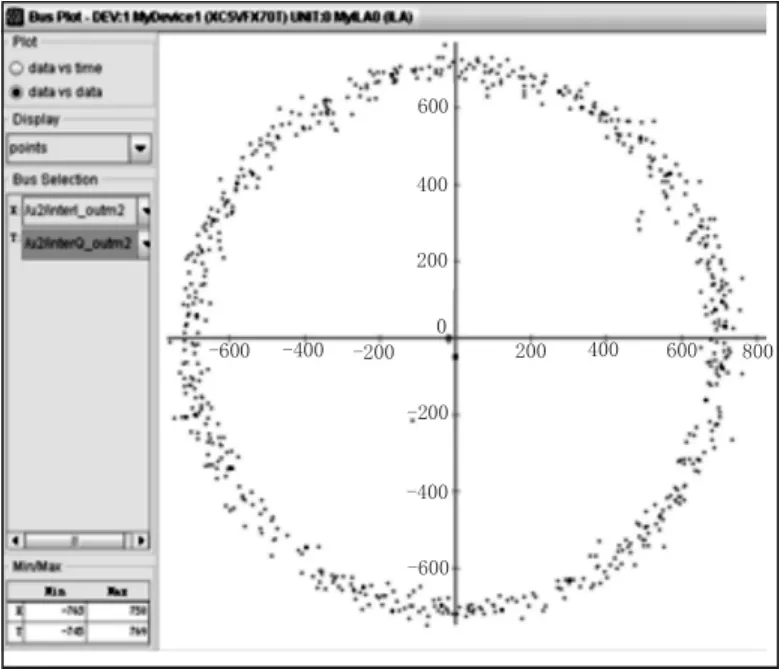

文中采用 Virtex5,MAX2830,AD9861等芯片构成收发板,对上述系统进行仿真验证,经综合实现生成bit文件后下载到FPGA芯片,经chipscope软件抓取个接口数据,结果如图8~10所示。

图8 NCO控制输出小数间隔曲线

由图8可以看出NCO控制输出的小数间隔收敛较好,抖动较小。由图10可以看出,经改进位同步环路抽取后信号星座图为一较窄的圆环,星座图较聚拢,说明该环路有效进行了位定时抽取,且实现结构简单,可靠性高,具有良好的工程应用价值。

图9 抽取前信号星座图

图10 抽取后信号星座图

5 结束语

文中提出的改进位同步环路,在应用改进型Gardner算法基础上,采用PSO算法对预滤波器进行优化设计,有效降低了定时误差抖动,能快速进行位定时抽取。通过Matlab仿真验证,相较于传统环路定时误差幅度降为原来的1/5,且达到同步状态所需点数也减小了约110个点,表明该位同步环路具有较好的收敛性、稳定性和准确性;通过FPGA验证,该环路入锁时间短,且实现结构简单,通用性好,具有良好的工程应用价值。

[1]Floyd M G.A BPSK/QPSK timing-error detector forsampled receivers [J].IEEE Transaction On Communication,1986,34(5):423-429.

[2]付永明,朱江,琚瑛珏,等.Gardner定时同步环路自噪声消减算法研究 [J].现代电子技术,2011,34(21):92-95.

[3]聂伟,林竹.基于FPGA的通用位同步器设计[J].现代电子技术.2013,36(15):45-46.

[4]刘国建,姚远程,秦明伟.定时同步中减小定时抖动的方法的研究与实现 [J].自动化仪表,2015,36(7):15-17.

[5]Kennedly J,Eberhart R C.Particle swarm optimization[A].Proc IEEE IntConf on Neutral Network[C]//Perth,Australia:IEEE,1995:1942-1948.

[6]Sobot R.Phase-LockedLoops[J].Wireless Communication Electronics,2012:253-262.

[7]吴明钦.数字中频接收机同步技术研究[D].成都:电子科技大学,2011.

[8]欧静兰,印勇,等.基于Gardner位同步定时算法的实验教学设计[J].实验科学与技术, 2014,12(4):1-3.

[9]赵秋明,何克森,陈小飞.基于System Generator的内插位同步法 [J].桂林电子科技大学学报,2014(2):96-100.

[10]王星泉.一种改进型APSK盲定时同步误差估算法[J].科学技术与工程.2015,15(10):195-196.

[11]任菊,蔡光君,刘惠英.直接型FIR滤波器的优化和实现[J].现代电子技术.2008,31(7):103-104.

[12]赵艳丽.卫星通信中定时恢复环路的自噪声消减法[J].电光系统.2013,145(3):40-42.

[13]赵安新,陈明,张钟华,等.采用综合学习粒子群算法的有限冲激响应数字滤波器设计[J].西安交通大学学报, 2012,46(8):71-75.

[14]李辉,张安,赵敏,等.粒子群优化算法在FIR滤波器设计中的应用 [J].电子学报,2015,7:1338-1340.

[15]候伯亭,顾新.VHDL硬件描述语言与数字逻辑电路设计[D].4版.西安:西安电子科技大学出版社,2014.

Design and implementation of a symbol synchronization loop to reduce timing jitter

ZHANG Pan1, ZHONG Sheng1, ZHANG Qi1, YANG Heng2

(1.Xi’an Microelectronics Technology Institute, Xi’an 710054, China;2.Xi'an Communication Insititutes, Xi’an 710106, China)

To reduce the self-noise of the symbol timing synchronization loop in a communication system,an improvement of the symbol synchronization loop based on the traditional Gardner algorithm is proposed,using modified Gardner algorithm and optimized prefilter by PSO algorithm to effectively suppress the timing jitter and quicken the convergence rate.The correctness and effectiveness of the improved algorithm is verified by the simulation,and the verification on FPGA indicates that it has a great value in engineering application.

symbol synchronization loop;modified Gardner algorithm;PSO algorithm;timingjitter;FPGA

TN919.3

A

1674-6236(2017)12-0138-05

2016-03-28稿件编号:201603367

张 盼(1990—),女,陕西咸阳人,硕士研究生。研究方向:无线通信。