TRIPLE RESURF LDMOS器件的优化设计

2017-07-12颜世朋薛智民王清波

颜世朋,薛智民,王清波

(西安微电子技术研究所(771所)陕西 西安710119)

TRIPLE RESURF LDMOS器件的优化设计

颜世朋,薛智民,王清波

(西安微电子技术研究所(771所)陕西 西安710119)

提出了一种新型TRIPLE RESURF结构的LDMOS器件,与普通的TRIPLE RESURF结构不同的是埋层采用了分区注入,即在靠近源端一侧采用较高注入剂量,在靠近漏端一侧则采用较低的注入剂量。因而会降低漏端表面电场峰值,提高了击穿电压。利用SILVACO TCAD软件分析了各个参数对击穿电压和比导通电阻的影响,与普通的TRIPLE RESURF结构相比,在比导通电阻不变时,击穿电压则提高了15 V。

LDMOS;TRIPLE RESURF;击穿电压;比导通电阻

随着集成电路的发展,尤其是智能功率集成电路的发展,对功率器件提出了越来越高的要求。LDMOS由于它的电极均可以在器件的表面引出,因而可以与主流的VLSI集成电路工艺技术相兼容,成为了功率集成电路的首选,并广泛应用于LED驱动、电源管理及汽车电子等领域。对于LDMOS来说,比导通电阻和击穿电压是两个重要的参数,同时相互影响,降低比导通电阻和提高击穿电压是器件的设计与研究的热点与难点。目前采用的技术主要有以下几种:场板技术[1],横向变掺杂技术[2],埋层技术[2-3],超结技术[4-8],降低表面电场(RESURF)技术[9-15]等技术,它们对器件击穿电压和比导通电阻的改善起到了很大的作用。

RESURF技术是在LDMOS器件设计中广泛应用的一种技术,它是利用横向与纵向两个PN结的耗尽层相互作用,就是器件在表面电场达到临界电场之前,使漂移区在纵向上完全耗尽,从而使击穿点由表面转移到体内,进而提高击穿电压。目前研究最多的是双RESURF LDMOS器件,它是在单RESURF的基础上,在漂移区顶部注入与漂移区掺杂相反的杂质,利用其辅助耗尽来改善器件的性能。

目前对于TRIPLE RESURF的研究却很少,文中提出了一种新型的TRIPLE RESURF LDMOS结构,这种结构在原TRIPLE RESURF LDMOS上进行了改进,P型埋层采用两次注入,形成靠近源端的浓度较高而靠近漏端的浓度较低。经仿真验证该结构与具有相同尺寸的普通TRIPLE RESURF结构相比,比导通电阻不变,而器件的击穿电压则提高了15 V。

1 器件结构分析

LDMOS器件,根据RESURF理论,nwell作为漂移区必须完全的耗尽,以使击穿发生在psub与nwell所构成的PN结,从而确保整个漂移区承受漏极所施加的高压。在TRIPLE RESURF结构中,降场层(pburied)处于漂移区中,整个漂移区被分成了上下两个部分,因而在纵向上漂移区由pburied和其上部的nwell、pburied和其下部的 nwell及 psub和 nwell构成的3个PN结共同来辅助耗尽,因而可以提高漂移区的浓度,从而可以进一步降低导通电阻。另外,由于离子注入后的杂质在硅中分布近似为高斯分布,因而漂移区中在靠近表面的地方杂质的浓度很高,器件导通的时pburied上方存在一条高电导通路。由于存在两条电流通路,器件的导通电阻进一步的得到降低。当漂移区长度为13.5μm时,击穿电压仅为283 V。

图1 两种TRIPLE RESURF结构的LDMOS器件

图1(b)是文中提出的一种新型的TRIPLE RESURF结构的器件,与图1(a)的结构类似,埋层仍然位于漂移区的中,只是埋层由两部分组成,即pb1和pb2。pb2的浓度小于pb1的浓度,这会降低靠近漏极处的表面电场。因为当漏极上施加高压时,埋层pb1和pb2都会被耗尽,由于此时pb2含有带有负电的受主离子,因而在靠近漏端会产生与外加电场方向相同的电场。Pb2的浓度降低了,这种电场叠加作用减弱,因而靠近漏端附近的表面电场相对降低,击穿电压相对地提高。在相同的器件尺寸及比导通电阻不变的条件下,NEW TRIPLE RESURF LDMOS器件的击穿电压由283 V提高到了298.3 V。

表1 两种结构的参数比较

2 参数分析与结果讨论

文中利用了Silvaco公司的工艺仿真软件ATHENA和器件特性仿真软件ATLAS对NEW TRIPLE RSEURF LDMOS RESURF LDMOS器件进行了优化设计。

2.1 漂移区注入浓度对于击穿电压和比导通电阻的影响

图2为器件的击穿电压和比导通电阻随着漂移区的浓度的变化曲线,此时的pb1和pb2的注入浓度分别为 2.63×1016cm-3和 2.38×1016cm-3, 其中 Nd代表漂移区的注入浓度。由图可知随着Nd的不断增大,击穿电压先是逐渐的增大后逐渐的减小,当漂移区的注入浓度Nd为4.29×1015cm-3时器件的击穿电压达到最大值为298.3 V。当Nd较小时击穿电压较小,因为此时漂移区过渡的耗尽漏极附近也被部分的耗尽,此处较高的空间电荷浓度产生了较高的电场强度,很易在该区发生击穿,导致击穿电压下降;而当Nd较大时击穿电压也比较小,这时是因为此时漂移区的浓度太高,漂移区不能被完全的耗尽,漏极所加的电压分布在很短的空间电荷区,靠近pwell附近的漂移区电势线很密,电场强度很高,因而击穿电压降低。比导通电阻则是随着漂移区的注入剂量的增加不断的减小,对于比导通电阻这个指标,我们希望Nd越大越好。但是对于LDMOS器件来说,我们不但希望击穿电压很大而且希望比导通电阻很小,因此我们选择Nd为4.29×1015cm-3。

2.2 埋层pb1和pb2的注入浓度对击穿电压的影响

图3为击穿电压随埋层pb1和pb2注入浓度的变化曲线,此时的漂移区的注入浓度为4.29×1015cm-3。图 3(a)中埋层 pb1 的注入剂量为 2.63×1016cm-3,击穿电压随埋层pb2的注入浓度先增加后降低。当pb2浓度较小时,等势线在靠近pwell附近的区域较密,因而发生击穿;当pb2浓度较高时,pb2埋层中的空间电荷较多,因而在漏端附近产生的附加电场也增大,使得靠近端的硅材料首先达到临界电场,因而在该处发生击穿。pb击穿电压在的浓度为2.38×1016cm-3时达到最大值298.3 V。图3(b)中埋层pb2的注入浓度为2.38×1016cm-3,击穿电压随着埋层pb1的注入浓度的增加也出现了先增加后降低的趋势,并且击穿电压在pb1浓度为2.63×1016cm-3时达到最大值。当pb1的浓度较小时,pb1埋层产生的反向附加电场减弱,击穿发生在场板末端的峰值电场处;当pb1浓度较高时,其耗尽时空间电荷密度也很高,导致pb1处的电势线很密,在该处出现一个很高的电场峰值,从而使整个器件的击穿电压下降。这说明当漂移区的注入浓度一定时,埋层pb1和埋层pb2的注入浓度之间存在一组最优值使击穿电压达到最大值。

图2 击穿电压和导通电阻随漂移区浓度的变化曲线

图3 两种结构击穿电压随埋层浓度的变化

2.3 器件击穿时的电势和表面电场的分布情况

图4分别为两种器件的表面电场分布,由图可以看出本文所提出的new triple RESURF LDMOS的表面电场分布比普通的triple resurf ldmos器件的分布更加均匀。这是因为new triple RESURF LDMOS的埋层在靠近漏极的一侧采用了比pb1浓度要小的pb2,产生的与外加电场同向的附加电场减弱,因而漏极附近的表面电场降低,从而使整个表面电场的分布更加的均匀,击穿电压也相应的提高。

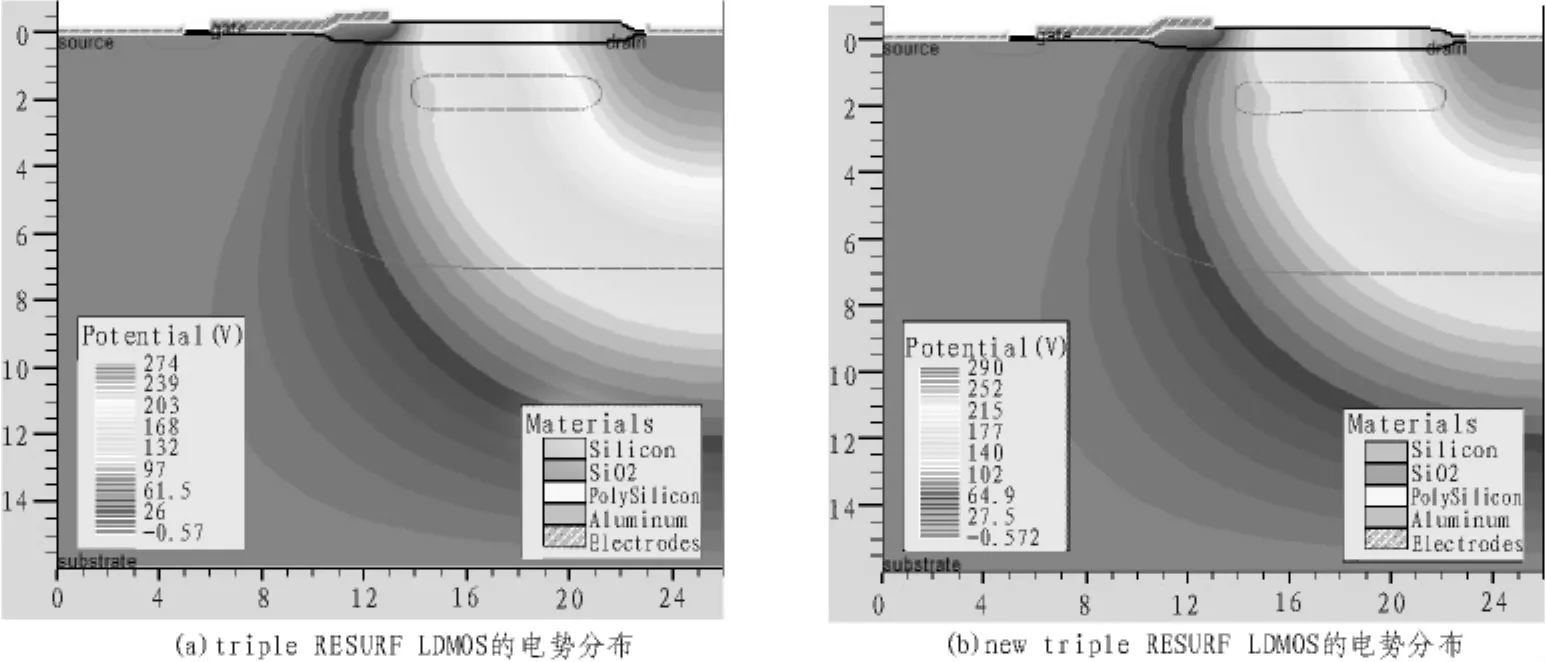

图 5(a)和图 5(b)是利用 ATALAS 仿真得到的triple RESURF LDMOS和new triple RESURF LDMOS两种器件的电势分布。由图可以看出本文所提出的new triple RESURF LDMOS器件的电势线分布的更加的均匀,因而其击穿电压更高。

图4 两种结构的表面电场分布

3 结 论

文中在普通的TRIPLE RESURF结构的基础上,提出了一种新型的TRIPLE RESURF结构,并利用Silvaco TCAD器件仿真软件对本文提出的new triple RESURF LDMOS器件的漂移区参数及pb1和pb2埋层的参数进行了优化,仿真结果表明,新型器件在比导通电阻为19 mΩ·cm2时,击穿电压达到298.304 V。在比导通电阻不变的情况下,击穿电压比普通triple RESURF LDMOS提高了15 V。与文献[9]中的相同尺寸的double RESURF和single RESURFLDMOS器件相比击穿电压分别增加了30 V和69 V。文中所提出的结构能够应用于高压电路,文中的结论对于设计高压低导通电阻的高性能LDMOS器件具有重要的意义。

图5 两种结构的电势分布

[1]文帅,乔明.具有单层浮空场板的高压LDMOS器件研究[J].电子与封装,2015,15(8):34-37.

[2]王卓,周锌,陈钢,等.超薄层SOI高压LVD LDMOS耐压模型及特性研究[J].微电子学,2015,45(6):812-816.

[3]李琦,张扬,段吉海.具有浮空埋层的高压器件新结构和击穿电压模型 [J].固体电子学研究与进展,2011,31(1):35-39.

[4]段宝兴,曹震,袁小宁,等.具有N型缓冲层RESURF Super Junction LDMOS [J]. 物理学报,2014,63(22):227-302.

[5]段宝兴,曹震,袁嵩,等.新型缓冲层分区电场调制横向双扩散超结功率器件[J].物理学报,2014,63(24):247-301.

[6]ZHU Hui,LI Hai-ou,LI Qi,et al.A novel multiple super junction power device structure with low specifi con-resistance[J].Journal of Semiconductors,2014,35(10):104006.

[7]WU Wei,ZHANG Bo,LUO Xiao-rong,et al.Low on-resistance high-voltage lateral double-diffused metal oxide semiconductor with a buried improved super-junction layer[J].Chin.Phys.B,2014,23(3):038503.

[8]WU Wei,ZHANG Bo,FANG Jian,et al.A high voltage Bi-CMOS compatible buffer super-junction LDMOS with an N-type buried layer[J].Journal of Semiconductors,2014,35(1):014009.

[9]朱奎英,钱钦松,孙伟峰.Double RE SURF nLDMOS功率器件的优化设计[J].固体电子学研究与进展,2010,30(2):256-261.

[10]孙鹏,刘玉奎,陈文锁.700 V三层RESURF nLDMOS优化设计[J].微电子学,2013,43(2):278-281.

[11]YIN Shan,Qiao Ming,Zhang Yongman,etal.Design of 700 V triple RESURF nLDMOS with low on-resistance [J].Journal of Semiconductors,2011,32(11):114002.

[12]宋庆文,胡夏融,冯灏.埋层深度对Triple-RESURF LDMOS纵向电场和击穿电压的影响 [J].微电子学, 2015,45(2):253-257.

[13]DUAN Bao-xing,YANG Yin-tang.Low Specific ON-Resistance PowerMOS TransistorWith Multilayer Car rier Accumulation Breaks the Limit Line of Silicon[J].IEEE Transactions on Electron Devices,2011,58(7):2057-2060.

[14]XU Qing,LUO Xiao-rong,ZHOU Kun,etal.Ultralow specific on-resistance high voltage trench SOI LDMOS with enhanced RESURF effect[J].Journal of Semicondurcors,2015,36(2):024010.

[15]LUO Yin-chun,LUO Xiao-rong,HU Gang-yi,et al.A low specific on-resistance SOI LDMOS with a noveljunction field plate [J].Chin.Phys.B,2014,23(7):077306.

Optimal design of TRIPLE RESURF LDMOS

YAN Shi-peng, XUE Zhi-min, WANG Qing-bo

(Xi’an Microelectronic Technology Institute(No.771 Institute),Xi’an 710119,China)

A new TRIPLE RESURF LDMOS was proposed,compared with conventional TRIPLE RESURF LDMOS,the difference was that the P_buried layer was divided into two regions,the region that is closed to the source has a large dose of ion implantation,while the region that is closed to the drain has a small dose of ion implantation.Thus the peak surface electricfield near the drain region was depressed,and the breakdown voltage was increased.Effects of parameters on breakdown voltage and specific on-resistance were analyzed by using device simulator and technology simulator Silvaco TCAD.Compared with conventional TRIPLE RESURF device structure,the specific on-resistance was almost the same,but the breakdown voltage was increased by 15 V.

LDMOS; TRIPLE RESURF; breakdown voltage; specific on-resistance

TN386

A

1674-6236(2017)12-0101-04

2016-05-07稿件编号:201605061

颜世朋(1988—),男,吉林长春人,硕士研究生。研究方向:BCD工艺。