基于可编程逻辑阵列的索贝尔边缘检测算法的两种实现方案

2017-05-15张海斌朱苏磊徐明亮

张海斌, 朱苏磊, 徐明亮

(上海师范大学 信息与机电工程学院,上海 200234)

基于可编程逻辑阵列的索贝尔边缘检测算法的两种实现方案

张海斌, 朱苏磊*, 徐明亮

(上海师范大学 信息与机电工程学院,上海 200234)

基于可编程逻辑阵列(FPGA)的片上可编程及并行流水线具有处理快、实时性等优点,采用Quartus II自带知识产权(IP)核进行设计的方案耗资源多,处理速度慢,针对于此提出了改进的索贝尔(Sobel)算子方案,使以上缺点得到改善;结合Matlab和Modelsim对这两种方案的仿真和验证结果表明,改进后的Sobel算子方案明显优于Quartus II自带IP核进行设计的方案,并且能很好地实现图像边缘检测,减少了偏差.

边缘检测; 可编程逻辑阵列; 数字图像处理

0 引 言

数字图像处理就是采用计算机或嵌入式系统对图像进行深度加工,并从中获得有用的信息.伴随着计算机技术、集成电路技术的飞速发展,数字图像处理技术也得到了很大的发展,并且也出现了许多与数字图像处理技术相关的新理论、新技术、新设备.这些新理论、新技术在工业生产、科学研究、医疗卫生等领域得到了广泛应用,对社会的发展及人类生活水平的提高做出了极大的贡献[1].

边缘是图像的基本特征,是指图像灰度变化率最大的位置,由图像像素点数据局部的不连续而形成.边缘的表现形式有图像纹理结构的突变及灰度级的突变,彩色变化等等,边缘检测利用物体与背景在某些特征上的差异而实现.由于实时图像边缘检测算法涉及到的数据量大,一般运算器的顺序执行或者传统软件处理实时图像很难满足要求.而采用可编程逻辑阵列(FPGA)的流水线和并行处理技术,不仅可以提高数字图像的处理速度,也可以在一定程度上满足实时系统中的应用需求.

边缘检测算子可以分为一阶微分算子和二阶微分算子.常见的一阶微分算子有Prewitt算子,Canny算子、Sobel算子、Roberts Cross算子,Kirsch算子,罗盘算子等等;二阶微分算子包括Laplacian算子以及高斯-拉普拉斯(LOG)算子等等[2].本研究主要介绍了基于FPGA的索贝尔(Sobel)边缘检测算法实现的两种方案,方案一完全采用Quartus II自带的知识产权核(IP)核进行实现,实现简单、工程周期短,但占用逻辑资源多,设计效果不够理想;方案二针对方案一的缺点进行了改进,改善了系统处理速度,减少了逻辑资源的消耗,在一定程度上改善了设计效果,优化了系统性能.

1 Sobel边缘检测算子实现理论及总体框架

1.1 Sobel边缘检测算子

索贝尔算子(Sobel operator)是数字图像处理中的常用算子之一,在图像边缘检测和噪声滤波中都有运用,它是离散型差分算子,用来提取图像亮度函数的梯度近似值.在图像的任何像素点上运用这一算子,都可以产生对应像素点的梯度矢量或是其法矢量[2].

现在假设图像数据点上有9个像素点:

σ=[(-1,-1),(-1,0),(-1,1),(0,-1),(0,0),(0,1),(1,-1),(1,0),(1,1)].

(1)

现用一个二次曲面z(x,y)来拟合这9个点的灰度值,即用

z(x,y)=ax2+bxy+cy2+dx+ey+g.

(2)

来近似图像灰度函数f(x,y),并使均方误差

(3)

将二次曲面z(x,y)对x,y求偏导数,得到梯度的幅度值[3]:

G(i,j)=[f(i-1,j-1)+2f(i-1,j)+f(i-1,j+1)]-

[f(i+1,j-1)+2f(i+1,j)+f(i+1,j+1)]+

[f(i-1,j-1)+2f(i,j-1)+f(i+1,j-1)]-

[f(i-1,j+1)+2f(i,j+1)+f(i+1,j+1)].

(4)

它的两个卷积模块为:

(5)

(6)

1.2 基于FPGA的Sobel算子实现框图

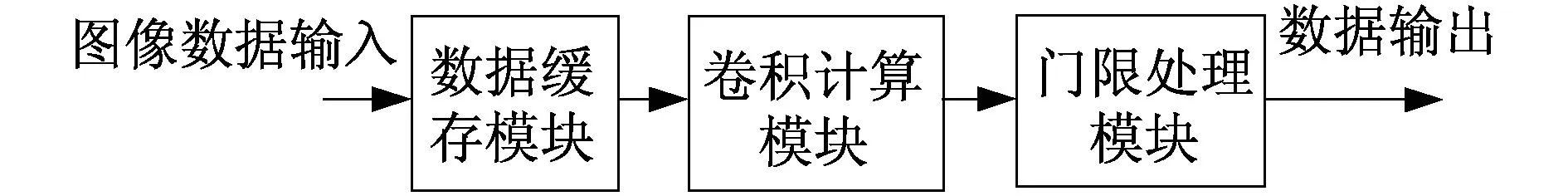

图1 Sobel边缘检测实现的原理框图

Sobel边缘检测算法的实现主要包括三个模块,如图1所示.

图1中,前两个模块主要是实现图像像素点的梯度值计算,图像数据输入通过数据缓存模块构成3×3矩阵像素阵列,然后再分别计算水平梯度和垂直梯度,然后把两个方向上的梯度结合起来,接着通过门限处理模块,实现判别输出.假设输入的像素值依次为:p11、p12、p13、p21、p22、p31、p32、p33,那么在垂直方向上的梯度和在水平方向上的梯度分别为:

GH=(p13+2p23+p33)-(p11+2p21+p31),

(7)

GV=(p11+2p12+p13)-(p31+2p32+p33).

(8)

梯度结合后的梯度值G为:

(9)

通常为了提高程序的运行速度都采用如下的公式:

(10)

门限处理模块之后输出数值P22,当设定的门限值大于G时,输出为0,当G大于设定的门限值时输出为255.综上分析Sobel算子在理论设计上容易实现,并且具有滤除噪声的作用,所以适合用在图像噪声较多的图像处理中.

2 基于IP核的Sobel算子实现方案

2.1 图像缓存实现

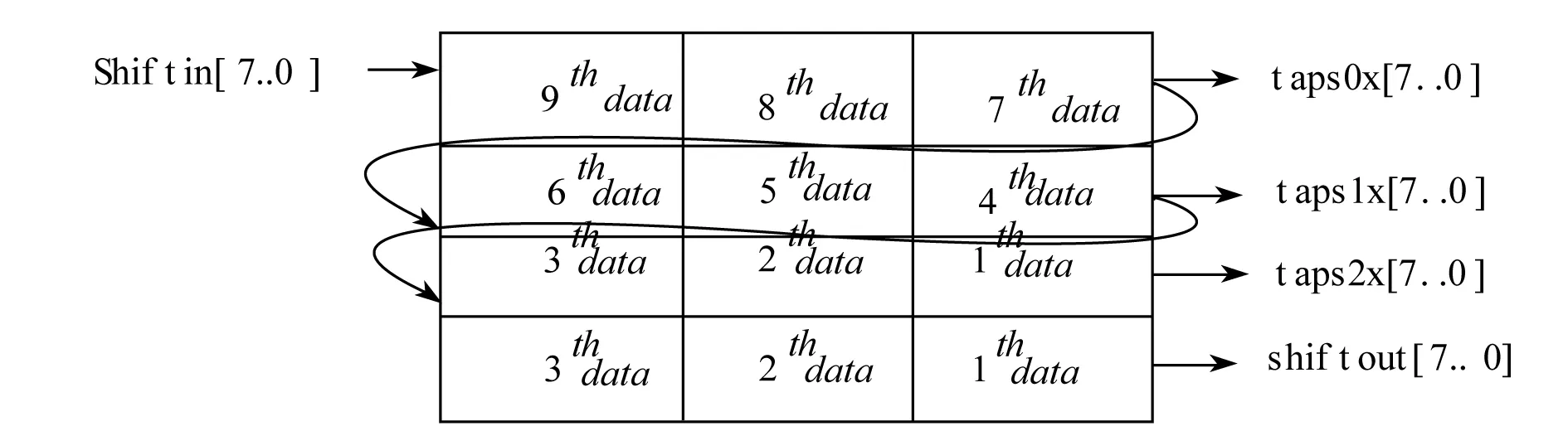

图2 altshift_taps内部数据流

由于Sobel算子理论基于3×3像素块计算中心像素梯度,构造3×3像素矩阵特别重要,要实现这个效果,必须使用一个容量足够大的存储单元来缓存串行输入的图像数据流,并把串行数据转化成并行的3行像素值,这样在3个像素时钟后就可以得到3×3图像像素矩阵.过去常使用先入先出(FIFO)作为图像数据的存储方式,但对FIFO的读写操作较为复杂.而本设计中主要是调用了Quartus II软件自带的altshift_taps移位寄存器宏模块.软件中提供的altshift_taps宏模块是一个可设置参数的并具有多个端口(Taps)输出的移位寄存器,每一个抽头在移位寄存器链的指定位置上输出数据.对于Matlab经常应用的256×256大小图像进行Sobel边缘检测,altshift_taps模块配置为8 bit输入/8 bit输出、3个抽头,相邻两个抽头有256个registor(寄存单元).经过预处理的9个图像灰度像素点进入缓冲区后数据流如,图2所示.

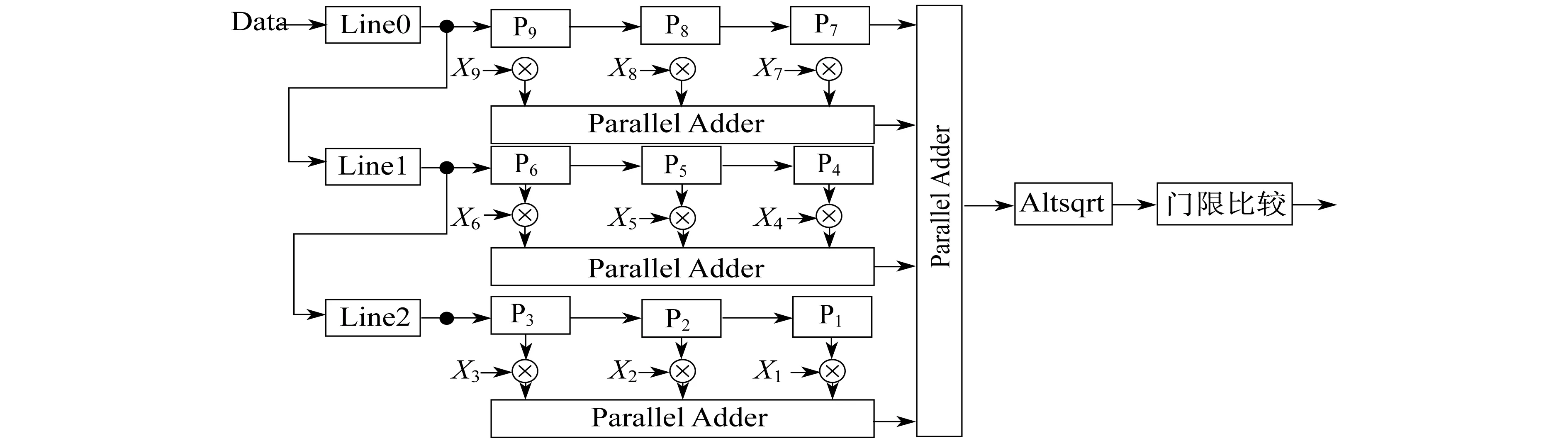

2.2 卷积计算和门限比较模块

编写的卷积计算模块是为了得到水平的、垂直的两个方向上的梯度值,要达到卷积运算的效果需要做大量的乘法、加法运算.若是采用以往分立的D触发器、加法器和乘法器来完成,可以实现预期的功能,但其结构复杂,设计繁琐.在本方案中先通过调用Quartus II开发工具提供的IP核模块中的可编程乘加法器altmult_add、可编程多路加法器parallel_add以及开方模块(altsqrt)来实现.其原理如图3所示.

图3 卷积计算示意图

图3中前面的3个Line就是缓存数据模块,而后面的实现水平梯度和垂直梯度的计算及开方后的结果再与门限比较,输出判别后的结果.

3 改进后的Sobel算子实现方案

考虑到上述方案调用IP时,占用FPGA逻辑资源大,在处理数据乘、开方时,占用大量CPU资源,提出了改进设计方案.

3.1 图像缓冲模块设计改进

基于图2的图像数据缓冲模块的数据流结构,构想在shift_RAM中存储2行数据,同时与当前的输入行数据组成3行的陈列,具体的实现步奏如下:

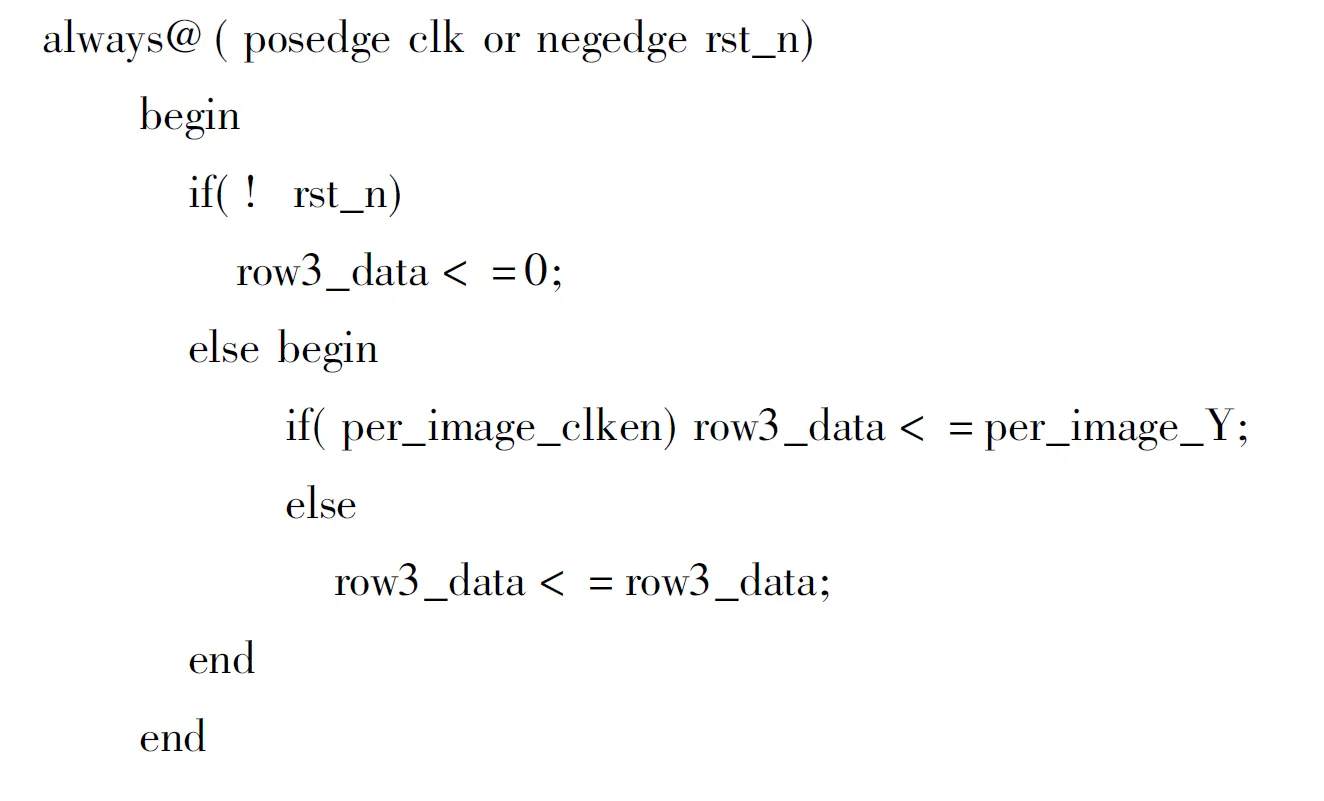

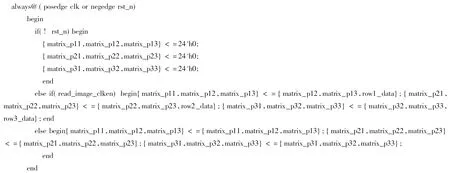

(1) 首先,将输入的信号用像素使能时钟同步一拍,以保证数据和宏模块altshift_taps输出的数据保持同步,主要实现代码如图4所示.

图4 同步宏模块altshift_taps输出数据代码

(2) 例化并输入row3_data,经过Modelsim仿真可以观察到3行数据同时存在.

(3) row_data读取信号的分析及生成数据在altshift-taps里存储消耗一个时钟,因此3×3阵列阵列读取使能需要一个时钟的偏移.

(4) 此时,根据read_image_clken信号直接读取3×3像素阵列,最后得到的matrix_p11、matrix_p12、matrix_p13、matrix_p21、matrix_p22、matrix_p23、matrix_p31、matrix_p32、matrix_p33即为得到的3×3像素阵列,主要代码如图5所示.

图5 3×3像素阵列生成代码

3.2 卷积模块的实现

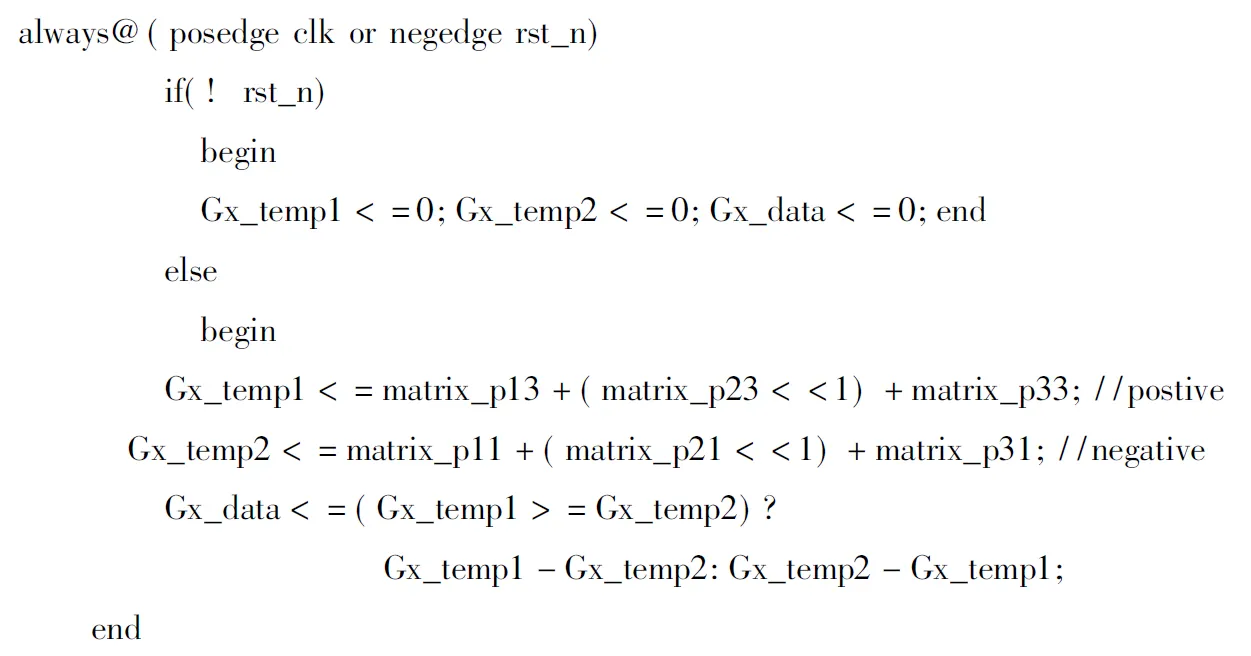

在1.2节中,可以利用(7),(8)式实现Sobel算子算像素点P22处的水平和垂直梯度值计算,在上面构成的3×3陈列中可以得到图像的每一个像素值,所以只要把(7),(8)式用Verilog语言实现就可以了,水平梯度值计算主要代码如图6所示.

图6 水平梯度值计算代码

这里只分析像素P22在水平上的梯度值,从3×3矩阵模块中出来的像素值matrix_p11,matrix_p12,matrix_p13,matrix_p21,matrix_p22,matrix_p23,matrix_p31,matrix_p32,matrix_p33都是reg无符号数型,即分别为P1、P2、P3、…、P9,在计算机内部数字乘以2就是bit位向左移一位,代码中通过暂存正结果和负结果,通过比较这个数值的大小最终给出水平上的梯度值.垂直上的梯度值同理实现.接着另一个进程中实现平方加的结果,最后再把平方加的结果送入开方模块SQRT中,输出对应像素点的估算梯度值,得到的梯度估算值与阀门值比较得出该像素点是否为边缘像素点.

4 实验结果及分析

4.1 两种方案在Quartus II下的分析对比

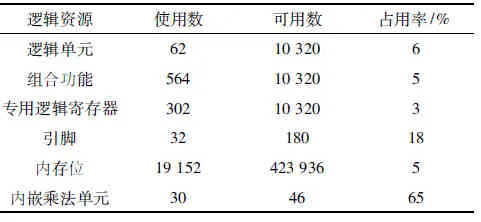

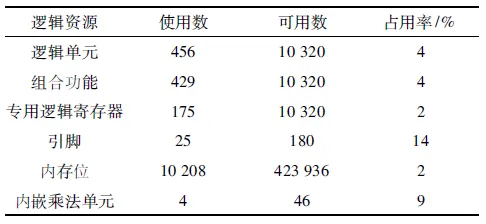

两种方案都是基于altera的CycloneIVE EP4CE10F17C8为目标芯片,在Quartus II下编译综合,得出两种方案的硬件资源使用情况综合报告及在约定输入时钟25 mHz时TimeQuest的时序分析报告如表1、2所示.

表1 IP核设计资源占用情况

表2 改进后的设计资源占用情况

从表1、2可以看出方案二明显比方案一占用资源少,首先,内嵌乘法器只占用了9%,这样数据处理大大减少;其次,专用逻辑寄存器和引脚也明显减少,这样可以在FPGA上留用更多的资源来处理其他信息;最后在25 mHz时钟约束下,从TimeQuest的分析时钟看,方案一最大工作效率为34.19 mHz,方案二可以达到47.78 mHz,这可以看出优化后的方案二数据处理速度明显提高,满足实时性的要求.

4.2 仿真结果分析

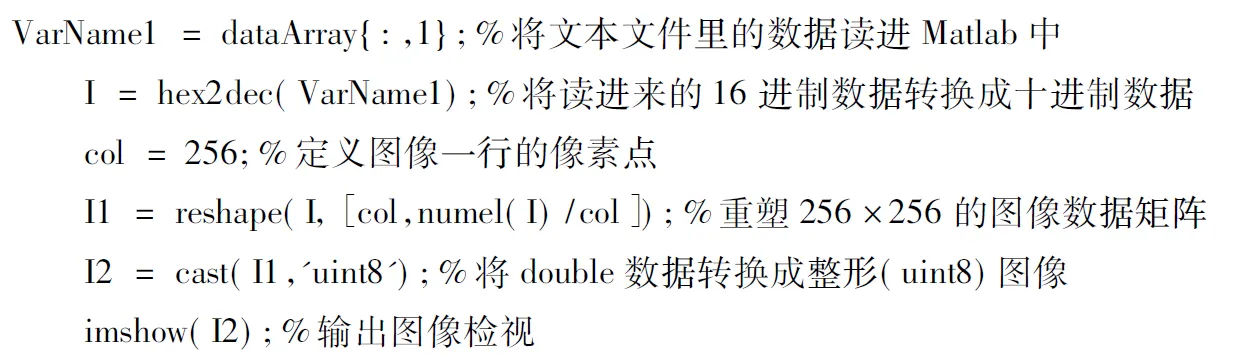

图7 图像显示处理代码

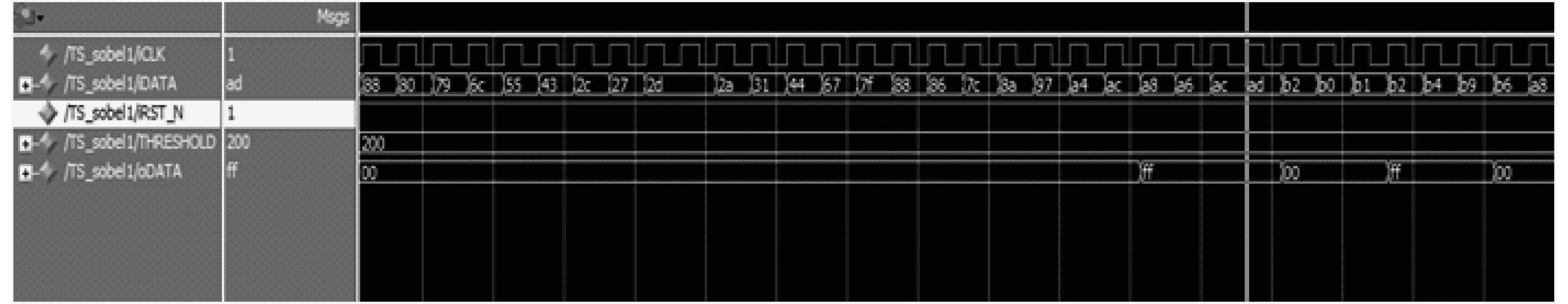

图8,9分别为输入相同图像数据时在Modelsim下两种方案的Sobel边缘检测仿真结果,门限设定都为200,从图8,9中可以看出在clk时钟的作用下,图像的各个像素值逐个输进输入端口,可以从输出端口(oDATA、post_img_Bits)看到只有两种状态,若该点在边缘上,则通过系统后该点值变为0xff,若不在边缘则变为0x00.两种方案可以实现对图像的边缘检测.

图8 方案一仿真结果

图9 方案二仿真结果

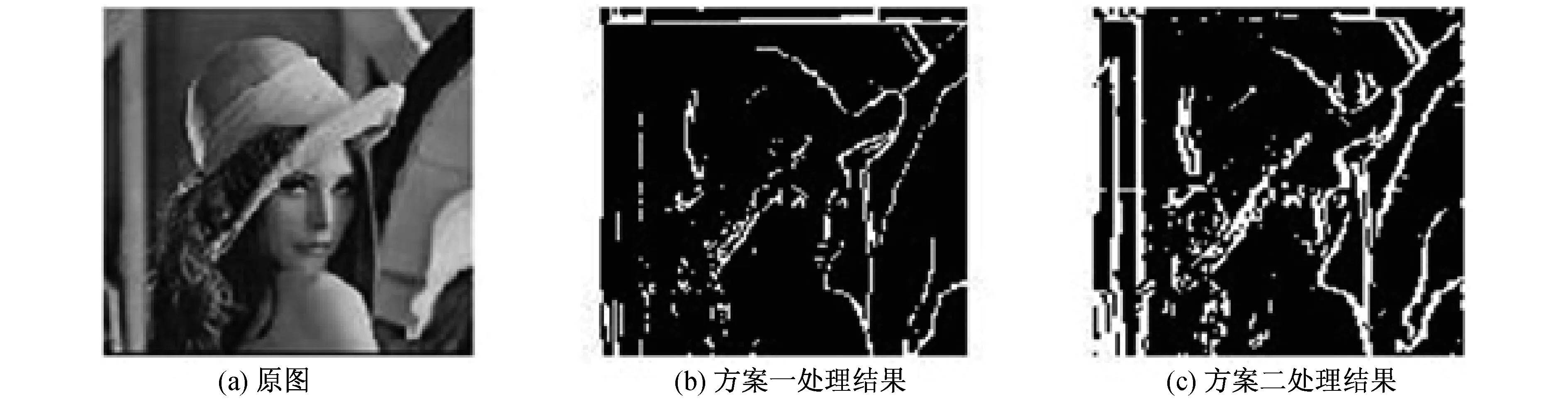

图10是设定阈值为200时两种方案对图像边缘提取后的结果对比,从图10中可以看出方案二的处理效果明显比方案一好,进一步说明改进后的方案优于采用IP核的方案;处理后的图片边沿明显出现了误判,这是没有对边沿像素点采取处理的结果,在实际工程中可以对图像边沿采取重叠复制、忽略处理等方法.

图10 Matlab重构处理后的结果

5 结 论

本文作者基于FPGA采用两种设计方案对Sobel边缘检测进行了实现并仿真分析,首先方案一中完全采用Quartus II自带的IP核设计各个模块,实现图像各个像素值卷积实现图像边缘检测,针对方案一占用FPGA逻辑资源多,处理图像数据慢等特点,设计了另一种设计方案,一方面,针对数据的左移一位(乘2)的思想很好地实现了数据点的水平和垂直梯度的提取,这样大大减少了FPGA内嵌乘法器的使用,也减少了结果误差的舍入;另一方面,为了构建3×3的图像矩阵,就需要构建图像数据缓冲模块,方案一中采用的图像数据缓冲模块完全采用3个taps的数据缓冲模块,每个taps的深度均为图片行的像素点,这样FPGA的逻辑资源很大程度上就被浪费了,影响FPGA的性能.为了改善这种状况,方案二只调用了2个taps的数据缓冲模块,并结合输入的数据端口利用FIFO的思想构成3×3矩阵,很好地改善了方案一中的占用逻辑资源较大的情况.综合对比两种方案,改善后的方案明显比方案一效果好,消耗资源少,耗时少,并且处理效果较好,完全满足实时图像处理的要求.

[1] Fang H R.The application of FPGA in image edge detection [J].Information and Communication,2015(1):9-11.

[2] Yan L,Lei B,Ding W,et al.Based on local adaptive thresholds edge detection of color image color difference [J].Journal of Electronics and Information,2012,34(9):2058-2063.

[3] Liao C Z.A Sobel edge-detection algorithm based on FPGA and emulation [J].Journal of Yangtze University,2015,12 (7):37-40.

[4] Pan M,Chen Y,Li Q.Design of image sampling system based on FPGA [J].Research and Development,2012,31 (3):58-61.

[5] Ruan Q Q,Ruan Y Z.Image processing [M].Beijing:Publishing House of Electronics Industry,2014.

[6] Xia Y W.Verilog course in digital systems design [M].Beijing:Beihang University Press,2008.

[7] Zhang Z Y.The master of Matlab [M].Beijing:Beihang University Press,2011.

[8] Zhang Y J.Design and algorithm realization of FPGA-based image processing systems[D].Chongqing:Chongqing University,2006.

[9] Wu Y.Basic algorithms of digital image processing based on FPGA design and implementation [D].Harbin:Harbin Institute of Technology,2008.

(责任编辑:包震宇)

Two kinds of implementations of sobel edge detection algorithmbased on field programmable gate array

Zhang Haibin, Zhu Sulei*, Xu Mingliang

(College of Information,Mechanical and Electrical Engineering,Shanghai Normal University,Shanghai 200234,China)

In this paper,two kinds of edge detection scheme based on Field Programmable Gate Array(FPGA) are realized and analyzed by using the Sobel operator.In view of the design which utilizes the intellectual property(IP) cores embedded in the Quartus II has some disadvantages such as more resources are consumed、process is relatively slow and so on,an improved scheme which improves the first design′s shortcomings is proposed.Simulation and verification results of these two schemes which are combined with Matlab and Modelsim show that the improved Sobel operator scheme is better than the previous scheme designed by using IP cores embedded in the Quartus II,achieving a good image detection and reducing errors.

edge detection; field programmable gate array; digital image processing

2015-11-10

上海师范大学样级科研项目(SK201410)

张海斌(1989-),男,硕士研究生,主要从事图像处理及模式识别方面的研究.E-mail:838026281@qq.com

导师简介: 朱苏磊(1975-),女,副教授,主要从事图像处理及嵌入式方面的研究.E-mail:suleizhu@163.com

TN 911.73

A

1000-5137(2017)02-0247-07

*通信作者