可变带宽数字下变频的设计与FPGA实现

2016-11-28冯晓东李华会

李 飞,冯晓东,李华会

(重庆邮电大学 通信与信息工程学院,重庆 400065)

可变带宽数字下变频的设计与FPGA实现

李飞,冯晓东,李华会

(重庆邮电大学 通信与信息工程学院,重庆 400065)

分析了数字下变频的结构和原理,提出了一种适用于多种带宽信号的数字下变频方案,并对其中的混频模块和抽取滤波模块进行了详细设计和介绍,最后结合Matlab和FPGA开发平台,分别对不同带宽信号的下变频功能进行了仿真和验证,结果表明方案是可行的。

数字下变频;抽取滤波器;可变带宽;现场可编程门阵列

0 引言

数字下变频技术(Digital Down Conversion,DDC)是软件无线电的关键技术之一,其主要功能是从高速宽带信号中提取到基带信号,同时对基带信号进行抽取和滤波,降低信号速率,以满足后续模块的实时处理[1]。采用DDC技术的数字接收机被广泛应用于广播电视、移动通信和无线电监测等领域。但是,随着通信技术的发展,传统的DDC方案由于支持带宽种类较为单一,已经无法满足上述应用领域的需求。带宽可灵活改变的DDC成为了市场的需求方向,在功能实现方面,由于FPGA具有并行处理能力强、编程开发周期短、灵活性好的特点,是目前实现数字下变频很好的选择。

1 数字下变频的总体设计

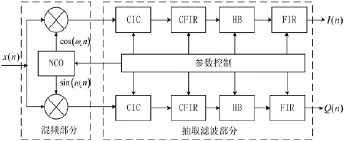

方案的总体结构如图1所示,包括混频部分和抽取滤波部分。

信号下变频的过程为:数字振荡器(Numerical Controlled Oscillator,NCO)产生正余弦本振信号与 A/D转换后的信号相乘进行正交混频,把基带信号搬移到零中频处[2],然后采用积分梳状滤波器(Cascaded Integrator-Comb, CIC)、补偿滤波器(Compensation FIR,CFIR)和半带滤波器(Half-Band,HB)对其进行抽取滤波[3],FIR滤波器对抽取后的信号做整形滤波,最后输出两路基带信号 I(n)和Q(n)。

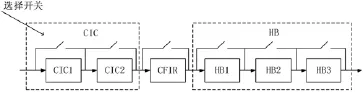

抽取滤波器组包括2个CIC滤波器、1个CFIR滤波器和3个HB滤波器,其结构如图2所示,每个滤波器都设置了选择开关,控制模块可以对滤波器的个数进行选择,同时也可以配置每个滤波器的抽取率,该设计通过对滤波器进行合理的分组级联,可以在满足系统性能的前提下,有效降低滤波器的阶数,更加高效地利用FPGA资源。

图1 数字下变频结构图

图2 抽取滤波器组结构图

2 数字下变频各模块的设计

2.1混频模块的设计

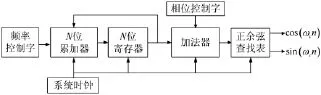

混频模块主要是由NCO和乘法器组成,NCO的功能是产生频率可控的正余弦本振信号,然后与输入信号相乘进行混频。NCO的结构如图3所示,工作原理是:输入的频率控制字与当前相位值不断进行累加计算新的相位值,然后在查找表中以该相位值为地址找出对应的波形数据[4];NCO产生正弦波的初始频率由频率控制字决定,初始相位由相位控制字决定。NCO输出频率由式(1)求得

图3 NCO的原理结构框图

其中,Fclk为系统时钟频率,Fcw为频率控制字,Fout为NCO的输出频率,N为累加器的位数。本文中Fclk=102.4MHz,N=32,参数控制模块通过改变频率控制字就可以改变输出正余弦波的频率。

2.2抽取滤波器组的设计

2.2.1积分梳状滤波器的设计CIC滤波器的冲激响应可表示为:

其中,D为抽取因子,从上式中可以看出CIC滤波器的结构比较简单,系数只有1和0,即只包含加法器不包含乘法器,所以占用资源较少,处理速度快,CIC滤波器常用作DDC滤波器组的第一级[6]。

CIC滤波器是由积分器和梳状滤波器组成,单级CIC滤波器的阻带衰减很小,约为13.4 dB,满足不了实际要求。本设计中使用5级CIC滤波器进行级联,级联之后滤波器具有 67.3 dB的阻带衰减[4],能够满足实际要求。

由CIC滤波器特点可知其比较适合大比例抽取,所以对带宽较小的窄带信号进行数字下变频时,可以通过控制模块配置2个5级CIC滤波器进行大比例抽取;对宽带信号下变频时,不需要很大的抽取率,控制模块可将CIC滤波器旁路。对CIC滤波器进行设计时,可采用Xilinx公司提供的CIC IP Core配置相应的抽取因子、级联数以及数据的位宽[8]。

2.2.2补偿滤波器的设计

CIC滤波器的通带衰减会随着阶数的增加而增大,为了克服信号由于通带衰减造成的失真,要在CIC滤波器后面级联补偿滤波器,对通带衰减进行补偿。

理想的CFIR幅频响应函数为:

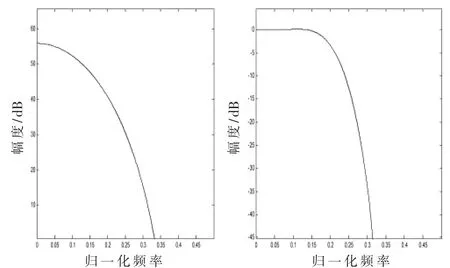

其中Q为CIC滤波器的级数,M为时间延迟,D为抽取因子[3]。补偿滤波器的幅频特性曲线局部放大后如图4所示,从图中能看出补偿滤波器通带增益是增加的。

图4 补偿滤波器幅频特性图

补偿前后CIC幅频特性局部放大后如图5所示。从图5可以看出,补偿滤波器对CIC滤波器通带具有一定的修正作用,使通带增益变稳定了。当CIC滤波器进行大比例抽取时,通带衰减比较大,控制模块选择CFIR滤波器进行补偿,当 CIC滤波器不参与抽取时,CFIR滤波器也被旁路。

图5 CIC滤波器补偿前后幅频特性曲线

2.2.3半带滤波器的设计

半带滤波器是通带宽度和阻带宽度相等的FIR滤波器,适合进行2的幂次方倍抽取或内插。HB滤波器的冲激响应为:

从式(4)可以看出,HB滤波器的冲激响应除了在h(0)零点处值为1外,在其他偶数点的取值均为零,即滤波器近一半的系数为零;比普通的2倍抽取FIR滤波器节省了一半的运算量,具有很高的实现效率[4]。

抽取过程中,控制模块可以对3个HB滤波器进行选择。方案采用Matlab的FADtool工具箱设计HB滤波器,把生成的的系数保存为 Xilinx COE系数文件,然后导入到 FPGA中的FIR IP Core,在 IP Core中配置好各项参数后,通过 Verilog语言编程进行实例化调用[7]。

2.2.4FIR滤波器的设计

半带滤波器阻带大小恒等于通带大小,滤波效果在一定程度上受到了限制,所以抽取滤波器后仍需要级联FIR滤波器,完成最终的整形滤波。由于抽取滤波器组的作用,此时的数据速率已经相对较低,因此减少了FIR滤波器设计时的阶数,进而降低了资源占用率[5]。

设计FIR滤波器时需要由式(5)确定相应采样率。

其中 1.28为滤波器的矩形系数,B为下变频信号的带宽,Fs为滤波器采样率。FIR滤波器的设计过程和HB滤波器类似,在 Matlab中设计需要的滤波器,把滤波器系数导入到FPGA中,然后进行IP Core的调用。

3 数字下变频的FPGA实现

3.1抽取率的配置

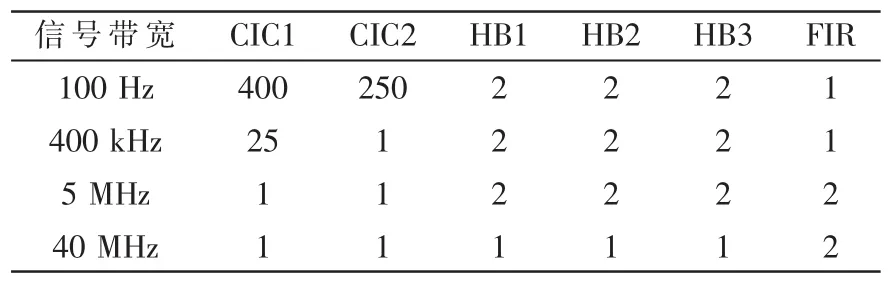

由于控制模块的加入,可以选择滤波器进行灵活组合,DDC可以达到的指标如表1所示。

表1 DDC的性能参数表

从表1可以看出DDC支持信号的带宽范围达到了100 Hz~40MHz;在实现功能的前提下,根据占用 FPGA的寄存器、查找表、BlockRAM等资源尽量少的原则来分配抽取率,表2给出了其中3种信号和抽取率对应关系。

表2 不同带宽信号滤波器抽取率分配表

这里对带宽为400 kHz和5MHz信号的下变频功能进行验证。由上述FIR滤波器设计可得400 kHz带宽信号对应 512 kHz的采样频率,系统采样时钟102.4MHz下降到512 kHz时抽取率为200。同理,5MHz带宽信号对应6.4MHz采样频率,抽取率是16。

从表2中可以看出,当下变频带宽设置为 400 kHz时,CIC1抽取率为25,CIC2滤波器被旁路;HB1、HB2和HB3进行抽取滤波,FIR不抽取,可得总抽取率为200。

当下变频带宽设置为 5MHz时,CIC1和 CIC2滤波器被旁路,HB1、HB2和HB3进行抽取滤波,FIR抽取率为2,总抽取率为16。

3.2实现结果及分析

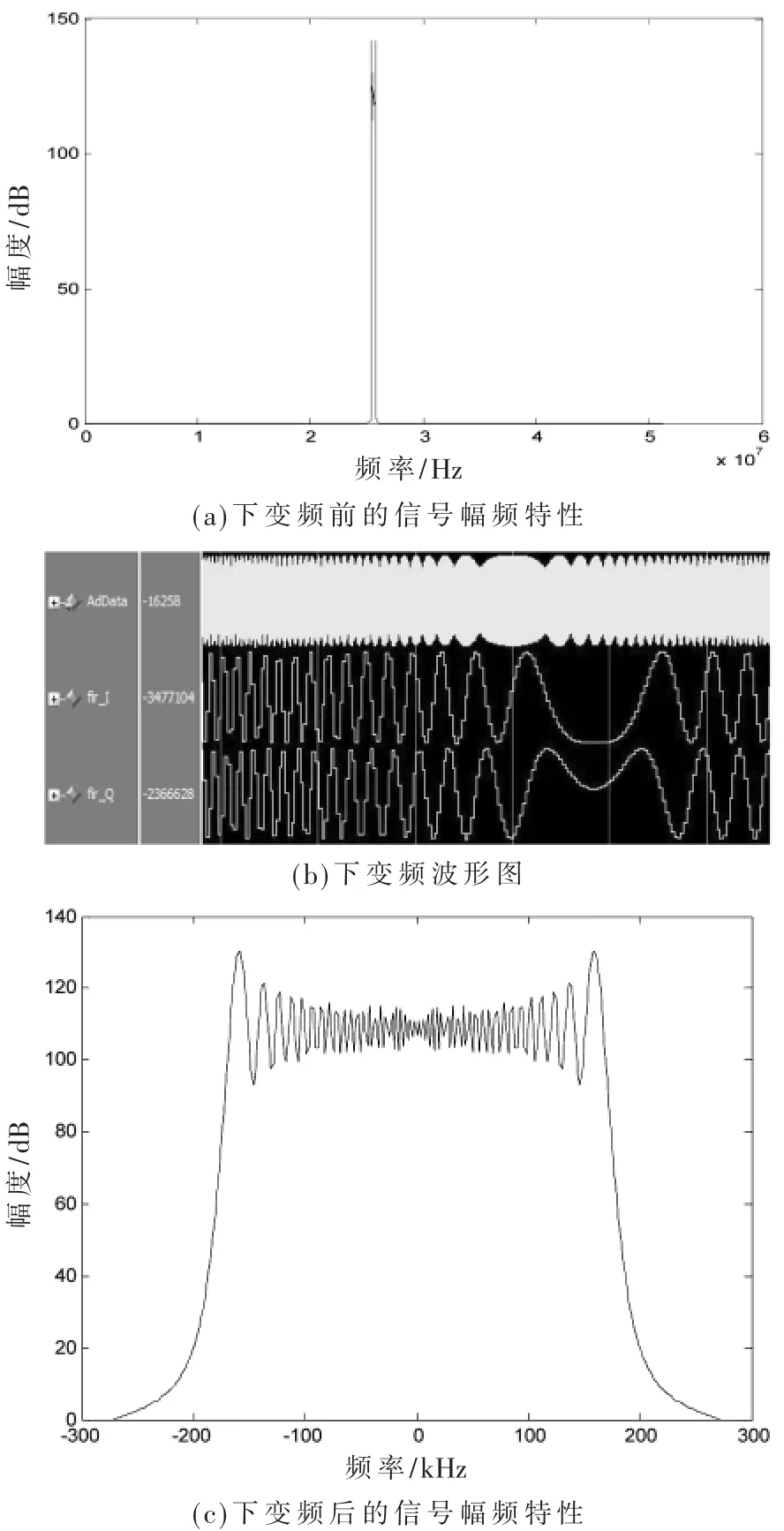

系统采用 Xinlinx公司 Artix-7系列的 xc7a200tfbg-676-2芯片,采样时钟为102.4MHz,输入中心频率为76.8MHz,带宽为 400 kHz的线性调频(LFM)信号,由带通采样定理可知,中频信号经过采样后,在25.6MHz处会出现基带信号的镜像信号,如图6(a)所示。

图6 400kHz带宽信号下变频过程

把采样信号的数据导入到FPGA中进行数字下变频,在 Xilinx Vivado平台上编写顶层模块、混频模块和抽取滤波模块。设置频率控制字,使NCO产生25.6MHz的正余弦信号与输入信号正交混频,把数字下变频带宽设置成400 kHz,控制模块按照表2进行配置抽取率,借助Modelsim 10.1a仿真软件进行仿真,下变频波形如图6(b)所示。

把FPGA输出的基带数据导入到Matlab中进行快速傅里叶变换,可得到基带信号的幅频特性图如图6(c)所示。

从图6中可以看出本设计准确完成了对400 kHz带宽信号的数字下变频。

同理,对5MHz带宽信号进行数字下变频,如图7所示。

图7 5MHz带宽信号下变频过程

从图7可以看出,系统也准确完成了对5MHz带宽信号的数字下变频。

以上仿真结果表明,对于不同带宽信号,本设计都可以通过控制模块对滤波器进行配置,准确完成信号的数字下变频。

数字下变频系统占用资源如表3所示,从表中可以看出,设计方案能够在占用FPGA较少资源的情况下完成数字下变频功能,具有很高的实现效率。

表3 xc7a200t资源占用表

4 结束语

本文提出了一种新的数字下变频方案,在CIC滤波器后加入补偿滤波器,改善了其通带衰减;通过加入控制模块对系统的各部分进行实时配置,使接收信号的带宽范围可达到100 Hz~40MHz,与传统下变频方案相比有很强的灵活性。在基于FPGA实现时,使用了Xilinx公司提供的IP核,大大缩短了开发周期,最后仿真结果表明本设计能够完成不同带宽信号的数字下变频。目前该设计方案已经应用到数字宽带中频接收机中,极大地提高接收机的接收性能。

[1]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[2]赵良羽.可变带宽的多级滤波器数字下变频设计[J].电子技术应用,2014,40(3):32-34.

[3]苏晓晓.数字化接收机的FPGA设计[D].哈尔滨:哈尔滨工业大学,2012.

[4]罗琳.基于FPGA的数字下变频的研究与分析[D].西安:西安电子科技大学,2013.

[5]徐小明,蔡灿辉.基于FPGA的数字下变频(DDC)设计[J].通信技术,2011,44(10):19-21.

[6]杨媛媛,吕幼新.高效实现DDC的多类滤波器级联技术[J].电子信息对抗技术,2011,26(4):72-76.

[7]Xinlinx Inc,LogiCORE IP FIR Compiler v6.3 DS794,2011.

[8]Xinlinx Inc,LogiCORE IP CIC Compiler v3.0 DS845,2011.

Design and implementation of digital down conversion with variable bandwidth based on FPGA

Li Fei,Feng Xiaodong,Li Huahui

(College of Communication and Information Technology,Chongqing University of Posts and Telecommunications,Chongqing 400065,China)

A design of DDC with variable bandwidth is proposed after researching the structure of traditional DDC,the mixer and decimation filters are mainly analyzed.Finally,a simulation of different signals based on Matlab and FPGA is given,the results indicate that this DDC architecture is correct and feasible.

DDC;decimation filter;variable bandwidth;FPGA

TN925

A

10.16157/j.issn.0258-7998.2016.04.010

2015-12-09)

李飞(1988-),通信作者,男,硕士研究生,主要研究方向:数字接收技术、数字信号处理,E-mail:lifeigzuo@163.com。

冯晓东(1970-),男,高级工程师,主要研究方向:射频微波接收技术。

李华会(1990-),女,硕士研究生,主要研究方向:无线电信号识别。

中文引用格式:李飞,冯晓东,李华会.可变带宽数字下变频的设计与 FPGA实现[J].电子技术应用,2016,42(4):35-38.

英文引用格式:Li Fei,Feng Xiaodong,Li Huahui.Design and implementation of digital down conversion with variable bandwidth based on FPGA[J].Application of Electronic Technique,2016,42(4):35-38.