双处理器实时视频拼接系统

2016-08-01冯桂兰吕昌亮

陈 静,冯桂兰,吕昌亮,康 宇

(中国计量大学 光学与电子科技学院,浙江 杭州 310018)

双处理器实时视频拼接系统

陈静,冯桂兰,吕昌亮,康宇

(中国计量大学 光学与电子科技学院,浙江 杭州 310018)

【摘要】当一些视频系统需更大观测范围,同时获得完整场景是一个问题.针对这种情况,提出一套基于FPGA和DSP双处理器协同工作的视频拼接系统,设计了包括双处理器、FLASH程序存储器、SDRAM数据存储器、SRAM数据存储器、视频AD和视频解码器等硬件结构.系统采集两路视频信号输入,对其进行数字视频转换,然后由FPGA做基本图像处理,并将其送入SDRAM进行存储.DSP将初步处理后的图像数据取出,并对其进行图像配准和图像融合.为了保证图像的实时性,系统采用实时高效易实现的改进的PSO算法实现图像配准,采用平均加权法实现图像融合.实验结果表明,此系统可对两幅720×576分辨率、25帧/秒的视频图像进行实时拼接,满足所需大视场视频图像要求.

【关键词】双处理器;现场可编程门阵列;数字信号处理;图像拼接;大视场

视频图像是一种具有直接、客观、记忆功能的信息承载体,在信息表达中起着非常重要的作用[1],与日常生活息息相关.随着电子、计算机、通信等相关技术的发展,视频图像在图像侦查[2]、高速运动目标检测、机器人视觉系统、网络摄像机、车辆检测与跟踪[3]等众多领域中有重要应用.市场上的单个摄像机虽逐步优化,但由于其自身限制并不能满足当前视频系统的应用需求,且超广角、广角等大视场镜头会造成畸变.针对这一问题,文献[4]研究了基于SIFT算法的拼接问题,文献[5]提出了一种分层式自适应采样的视频拼接方法,文献[6]提出了一种基于控制帧的固定摄像头视拼接方法,文献[7]则研究了可以实现全自动视频拼接的方法,这些研究均通过视频拼接来扩大视场范围.近年来,随着FPGA和DSP的快速发展,将FPGA和DSP应用到视频图像领域有一定的研究,文献[8]介绍了一种基于FPGA和DSP的视频处理硬件系统,文献[9]设计并实现了一种基于FPGA和DSP的高清视频图像系统,文献[10]则研究了基于FPGA和DSP的视频图像采集处理系统.基于这些研究,本文提出一套用FPGA和DSP双处理器实现视频拼接[11]的系统,详细叙述了此系统的硬件选择和软件实现,并通过实验验证.试验结果表明,该系统可实现视频图像实时拼接,满足所需大视场视频图像要求.

1双处理器实时视频拼接系统总体设计

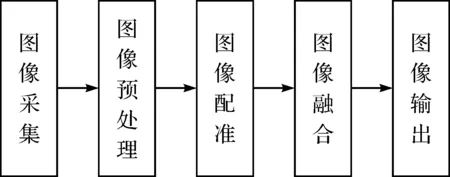

为保证系统的实时性,采用FPGA和DSP作为双处理器[12],双处理器协同工作实现视频数据的采集[13]、处理和输出.双处理器实时视频拼接系统包括图像采集、视频拼接和图像显示三个部分.为获取大视场图像,采用对多幅视频图像进行图像配准和图像拼接,从而得到一幅符合要求的大视场、高分辨图像,其视频图像拼接算法流程图如图1.

多个图像传感器采集到的图像数据经过AD转换变成数字图像数据流,再依次通过图像预处理、图像配准、以及图像融合来实现整个算法.图像传感器所获得图像,由于传感器内部以及一些随机信号影响,会使所得图像被动的加入一些噪声,使图像无法完全正确还原原始图像的有用信息,因此系统进行图像预处理,主要包括图像滤波和图像锐化.图像配准是对有重叠的两幅图像进行搜索,找到位移、旋转角度等特征量,从而实现两幅图像融合,图像融合是根据图像配准提供的位移等特征量,实现将两幅图像拼接在一起,图像融合算法主要用加权平均法.

图1 视频图像拼接算法流程图Figure 1 Flow chart of video image mosaic algorithm

2双处理器实时视频拼接系统的硬件设计

本视频拼接系统需要处理来自两个相同的图像传感器、在同一视场平面内所采集的图像模拟信号,视频图像拼接系统硬件设计总体框图如图2.

图2 视频图像拼接系统硬件设计总体框图Figure 2 Hardware diagram of the video mosaic system

视频拼接系统采用FPGA+DSP双处理器结构,FPGA采用Altera公司Cyclone Ⅲ系列EP3C40F484,具有丰富的硬件资源,包括40K逻辑单元(LE)、1.61Mbit片内RAM、126个18×18硬件乘法器以及4个PLL单元等,可以充分的保证较为复杂的图像处理算法的硬件实现需求.TMS320DM642是TI公司推出的一款面向数字多媒体应用的DSP,其工作频率为600 MHz,处理能力为4800MIPS,具有8个并行处理单元、两级缓存的Cache结构,结合TI公司的图像处理库,可实现多种高级图像处理程序.本系统采用两个视频通道输入,实验中两相机机械安装位置如图3.

图3 相机安装图Figure 3 Camera location

两路独立CCD摄像机视场角分别为β1,β2,两路视频的视场保证一定的重叠场景,为后续图像拼接提供基础.所采集视频均为模拟视频,需进行A/D转换.视频解码芯片将PAL视频信号转换为符合BT.656标准的数字信号后经过FPGA控制中,以备图像预处理.FPGA与DSP地址线和数据线相连,通过分时复用,达到对SDRAM数据存储器的访问,从而完成视频数据的存储和传递.FPGA连有两块SDRAM,这也是FPGA向DSP传送图像数据和处理结果的主要通道.其工作模式为FPGA将当前帧的图像数据和处理结果写入其中一块SDRAM时,DSP可以从另一块SDRAM中读取上一帧的图像数据和处理结果,并进行下一步处理操作.这种并行工作方式使系统具有高速实时性,其中SRAM存储器负责系统的数据暂存.DSP将两幅图像拼接处理后的数据通过I2C配置视频编码芯片进行视频编码,视频编码主要功能是把YCbCr数字图像信号或者MPEG格式数字图像信号编码成视频信号S-VIDEO,以供VGA显示屏对系统完成输出图像的显示.

3双处理器实时视频拼接系统的算法

为了实现大视场高分辨的视频图像,需要对前端获取的图像进行图像拼接,主要包括两个部分,首先进行图像配准,然后进行图像拼接.

3.1图像配准

图像配准核心是如何利用相邻图像重叠区域的相似性,求解出两幅图像间的空间变换关系.最大互信息(MI)图像配准方法,是基于像素灰度的配准方法,具有亚像素级的配准精度,且不需对图像进行分割、特征提取等预处理,本文采用以图像最大MI为匹配测度的粒子群优化算法完成图像拼接.以下详细介绍经典粒子群优化算法的原理.由美国社会心理学家Kenndedy和电气工程师Eberhart共同提出的粒子群优化算法(PSO)是智能优化算法的一种[14],其基本思想源于鸟群觅食行为,具有简单、易理解、参数少的优点,在很多领域有重要应用.鸟群在未知食物位置时最有效的搜寻方式是寻找离食物最近的鸟的周围区域.PSO初始化为一群随机粒子,通过迭代在搜索空间找到最优值.如式(1),Xi(t)和Xi(t+1)分别代表xi上一次的以及当前位置,Vi(t+1)表示粒子的行进速度.

Xi(t+1)=Xi(t)+Vi(t+1).

(1)

正是这个行进速度驱使粒子走向更优的位置速度更新的公式如下:

V(t+1)=ωVi(t)+c1r1(Pi-Xi(t))+

c2r2(Pg-Xi(t)).

(2)

式(2)中:Xi(t)是粒子当前位置信息;Pi为粒子Xi所找到的最佳位置,也称自身最优位置(personal best);Pg是粒子Xi的“邻居们”所找到的最佳位置,也叫做全局最优位置(global best);Vi(t)是Xi的速度值;c1、c2表示学习因子,且为常数,c1主要是用来调节粒子飞向自身最优位置的权重系数,c2则用来调节粒子向全局最优位置方向飞行的权重系数;ω为惯性因子,使粒子保持运动惯性的同时具有探索新区域的能力;r1、r2分别为0~1之间的随机数;主要目的是为了保证在进化过程中粒子一直在搜索空间的范围之内.为保证足够次数的迭代,速度Vi(t)一般需要限定于一定范围内.由于PSO算法是基于随机搜索的,一种改进后的IPSO算法步骤为:1)初始化种群,包括最大进化数种群规模,学习因子参数设置、粒子速度、位置及每个粒子历史最优值和种群历史最优值的初始化.2)据式(1)和(2)对每个粒子的速度更新,且取反,得到一个新速度.3)根据粒子的当前速度和取反后的速度,分别求出对应的速度以及适应值,对比适应值,保留适应值较好的速度给当前粒子.4)据当前的适应值更新粒子的历史最优值和种群的历史最优值.5)判断是否达到最大进化数或者满足精度要求,若是满足则结束算法,返回步骤2).算法流程如图4.

图4 MPSO算法流程图Figure 4 Flow chart of MPSO algorithm

3.2图像融合

算法取得最佳的位置后,为了保证系统的实时性,本文在重叠区域采用平均加权法实现了图像融合,融合效果较好.以A和B两图像为例,加权平均的数学表示为

F(x,y)=ω1A(x,y)+ω2B(x,y).

(3)

式(3)中,A和B代表两幅待融合图像,A(x,y)和B(x,y)分别为A和B图像在(x,y)的像素灰度值.ω1和ω2为加权系数,ω1+ω2=1;若ω1+ω2=0.5,则为平均融合[15].

4实验结果

为验证设计系统的性能进行相关实验,分别取两CCD摄像机拍摄视频中的一帧,如图5,一幅为参考图像(a),另一幅为浮动图像(b),其中图像浮动图(b)与(a)相比有水平位移、垂直位移.实验结果如图(c).

图5 系统输出结果图Figure 5 Output images

5结语

基于大视场视频图像的需求,提出一套基于FPGA+DSP双处理器的视频拼接系统.实验结果表明,此系统可对两幅720×576分辨率的视频图像进行实时拼接,满足大市场视频图像要求.

【参考文献】

[1]雷中锋,王广生,方穗明.视频图像拼接和应用[J].中国有线电视,2003(22):70-71.

LEI Zhongfeng,WANG Guangsheng,FANG Suiming.Video image stitching and its application[J] .China Cable Television,2003(22):70-71.

[2]孙展明,尹伟中.论视频图像侦查[J].中国人民公安大学学报(自然科学版),2011(3):25-28.

SUN Zhanming, YIN Weizhong. The theory of the video investigation[J].Journal of Chinese People’s Public Security University( Science and Technology),2011(3):25-28.

[3]许洁琼.基于视频图像处理的车辆检测与跟踪方法研究[D].上海:中国海洋大学,2012.

XU Jieqiong. Research on vehicle detection and tracking method based on video image processing[D].Shanghai: Ocean University of China,2012.

[4]YANG Jinkun,PEI Yijian,LI Bo, et al. Multivideo mosaic based on SIFT algorithm[C]// 2011 International Conference on Computer Science and Network Technology.Portugal:[s.n],2011:1497-1501.

[5]刘永,王贵锦,姚安邦,等.基于自适应帧采样的视频拼接[J].清华大学学报(自然科学版),2010,50(1):108-112.

LIU Yong,WANG Guijin,YAO Anbang, et al. Video mosaicking based on adaptive sampling[J].Journal of Tsinghua University(Science and Technology),2010,50(1):108-112.

[6]刘畅,金立左,费树岷,等.固定多摄像头的视频拼接技术[J].数据采集与处理,2014,29(1):126-133.

LIU Chang, JIN Lizuo, FEI Shumin, et al. Video stitching technology based on fixed multi-camera[J].Journal of Data Acquisition and Processing,2014,29(1):126-133.

[7]王小强,陈临强,梁旭.实时全自动视频拼接方法[J].计算机工程,2011,37(5):291-293.

WANG Xiaoqiang,CHEN Linqiang,LIANG Xu. Method of real time automatic video stitching[J].Computer Engineering,2011,37(5):291-293.

[8]刘晓明,田雁,许朝晖.基于DSP和FPGA的视频处理系统设计及其实现[J].激光与红外, 2007,37(12):1328-1330.

LIU Xiaoming, TIAN Yan, XU Zhaohui. Design and realization of video-processing system based on DSP and FPGA[J].Laser and Infrared,2007,37(12):1328-1330.

[9]高杨,刘荣科,胡伟.基于FPGA+DSP的高清视频图像系统设计与实现[J].电子测量技术,2011,34(1):69-73.GAO Yang, LIU Rongke, HU Wei. Design and implementation of high definition video image system based on FPGA+DSP[J].Electronic Measurement Technology,2011,34(1):69-73.

[10]李易难,牛燕雄,杨露.基于DSP+FPGA视频图像采集处理系统的设计[J].电子测量技术,2014,37(1):58-61.

LI Yinan,NIU Yanxiong,YANG Lu. Design of video image sampling and processing system based on DSP and FPGA[J]. Electronic Measurement Technology,2014,37(1):58-61.

[11]OKUMURA KI, RAUT S,GU Qingyi,et al. Real-time Feature-based Video Mosaicing at 500 fps[C]//2013 IEEE/RSJ International Conference on Intelligent Robots and Systems (IROS).Portugal:[s.n],2013:2665-2670.

[12]冯桂兰,田维坚,屈有山,等.实时视场拼接系统的设计与实现[J].光电工程,2007,34(4):144-147.

FENG Guilan ,TIAN Weijian, QU Youshan, et al. Design of real-time video mosaic system[J]. Opto-Electronic Engineering,2007,50(1):144-147.

[13]高站力,余桂英,唐玮.FPGA图像采集系统研究与设计[J].中国计量学院学报,2014,25(1):75-79.

GAO Zhanli,YU Guiying,TANG Wei. Research and design of an image acquisition system based on FPGA[J].Journal of China University of Metrology,2014,25(1):75-79.

[14]杨维,李岐强.粒子群优化算法综述[J].中国工程科学.2004,6(5):87-94.

YANG Wei,LI Qiqiang. The review of Particle Swarm Optimization[J].Engineering Science,2004,6(5):87-94.

[15]牛文宾.图像融合算法研究及应用[D].重庆:重庆理工大学,2012.

NIU Wenbin. Research and application on image fusion algorithm[D].Chongqing:Chongqing University of Technology,2012.

【文章编号】1004-1540(2016)02-0223-05

DOI:10.3969/j.issn.1004-1540.2016.02.017

【收稿日期】2015-12-08《中国计量学院学报》网址:zgjl.cbpt.cnki.net

【基金项目】浙江省科技厅公益技术应用研究项目(No.2013C31061).

【作者简介】陈静(1987-),女,湖北省孝感人,硕士研究生,主要研究方向为图像处理.E-mail:532519842@qq.com 通信联系人:冯桂兰,女,副教授.E-mail:fengguiian@cjiu.edu.cn

【中图分类号】TN911.73

【文献标志码】A

Real-time video mosaic systems based on double processors

CHEN Jing, FENG Guilan, LYU Changliang, KANG Yu

(College of Optical and Electronic Technology, China Jiliang University, Hangzhou 310018, China)

Abstract:It is difficult for some video systems to capture the whole scene simultaneously. In view of this situation, a video mosaic system based on FPGA and DSP dual-processors was proposed. A hardware architecture including dual-processors, FLASH program memory, SDRAM data memory, SRAM data memory, video AD and video decoder was designed. Two video input signals were captured and converted to digital signals and were stored in the SDRAM after basic image processing by FPGA. The image data readout, registration and fusion were processed by DSP. To ensure the real-time property of the system, the improved particle swarm optimization (IPSO) algorithm was adopted to process the image registration; and the image fusion was processed by the weighted average method. The test results show that two images were acquired and stitched simultaneously at resolution of 720×576 and 25FPS.

Key words:dual processor; FPGA; DSP; image stitching; wide field of view