高频小信号频率计的设计*

2016-07-23李江坤李可人

李江坤,李 阳,李可人

(太原科技大学 电子信息工程学院,山西 太原 030024)

高频小信号频率计的设计*

李江坤,李阳,李可人

(太原科技大学 电子信息工程学院,山西 太原 030024)

摘要:本方案设计的频率计由衰减电路、宽带通道放大器、整形电路、FPGA测量模块、STM32单片机最小系统组成。设计了一个放大倍数为40 dB的两级宽带通道放大器,将10 mV(有效值)的信号放大到1 V(有效值)左右。第一级使用OPA847实现了26 dB的放大,第二级使用THS3201实现了14 dB的放大。当被测信号幅度较大时,使用衰减网络将被测信号衰减到10 mV左右。放大后的信号整形后产生相同频率的方波信号,使用CycloneIV FPGA芯片实现等精度法测量频率、时间间隔和占空比。测量结果通过串口传给STM32单片机系统进行相关处理和显示。

关键词:STM32单片机;FPGA;等精度法;宽带通道放大器

基于FPGA的数字信号频率计早就有了相应的设计方法和算法实现,但在满足高频如100 MHz以上和小信号如10 MV左右的情况下仍能设计出相对应的频率计还没有对应的设计实现。本设计的特色就是小信号和高频,此外本设计也应用了等精度测量法[1],可以很大程度上减小误差。而且本设计中对高频小信号的放大经验也可应用于其它设计。

1系统方案

1.1方案论证与比较

方案一:FPGA普通测量法。在1 s闸门时间内,记录被测信号的脉冲个数Fx,则被测频率为Fx=Nx。此方法的精度主要取决于被测信号频率,被测信号频率越高,误差越小。由于精度与被测频率相关,低频信号的频率测量误差较大,故舍弃此方案。

方案二:FPGA等精度测量法。本方案除给定闸门时间外,还由被测信号再生成一路计数允许信号。计数允许信号在闸门时间内第一个被测信号的上升沿开启,在闸门时间结束后被测信号的第一个上升沿结束,最后在计数允许信号的有效时间内,分别对标准频率信号个数、被测信号个数和被测信号高电平时间内标准频率信号个数计数后,再经过相关运算即可得所求频率、占空比和时间间隔。此方案的误差与被测信号无关,测量精度大大提高。故本设计采用此方案。

1.2方案描述

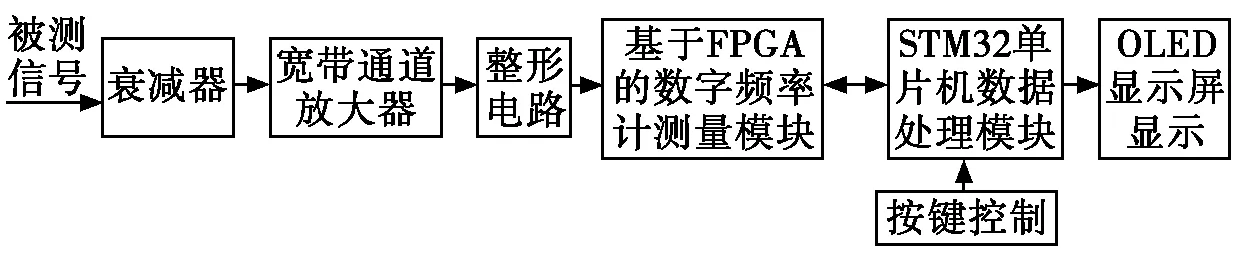

系统总体实现框图如图1所示。

图1 数字频率计组成框图

本方案中衰减电路用于将不定幅值的输入信号有选择性地衰减至固定范围内的小信号,带宽通道放大器再将此范围内的小信号放大至可开启整形电路的大信号,再由整形电路将信号整形为TTL电平方波信号,最后使用FPGA实现了等精度测量算法,对相关参数进行计数后经按键控制有选择性地将有关数据传输给STM32单片机,单片机经过运算处理后将结果显示在显示屏上[2]。

2理论分析与计算

2.1宽带通道放大器分析

本设计中要求的测量范围是有效值10 mV~1 V的信号,满足FPGA识别的电平约3 V左右峰峰值,可知需设计一个40 dB的宽带通道放大器。一级放大很难满足要求,因此设了一个两级宽带通道放大器。当被测信号较大时,使用衰减器将被测信号衰减到10 mV左右。本设计中采用的是前级为OPA847,第二级为THS3201的两级放大电路。按最低输入有效值为10 mV计算,总共放大40 dB即可使峰峰值达到2.8 V,再加上1.4 V左右的直流偏置即可达到设计要求。本次设计由OPA847进行第一级26 dB、最大频率100 MHz的放大。根据器件手册可知,OPA847是一个电压反馈放大器,在增益为26 dB时带宽是350 MHz,压摆率950 V/μs,低噪声等特性可满足设计要求。再由THS3201进行第二级14 dB、最大100 MHz放大,根据器件手册可知此芯片是电流反馈型,压摆率为6 700 V/μs的运算放大器,当宽带通道放大器最终输出峰峰值为3 V,100 MHz时所需的压摆率为600 V/μs,可知本芯片完全可胜任第二级放大的需求[3]。

2.2各项被测参数测量方法的分析

2.2.1频率和周期测量方法

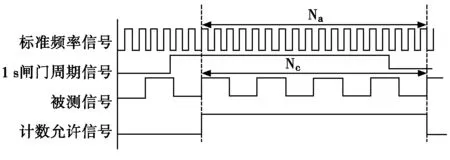

本设计中频率和周期测量采用的是等精度测量原理,等精度测量原理的时序图如图2所示。

图2 等精度测量原理时序图

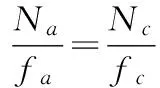

如图所示,在计数允许信号有效的时间内,采用两个计数器分别对标准频率信号和被测信号进行计数,计数结果分别为Na、Nc,若标准频率信号和被测信号频率分别为fa和fc,则有 :

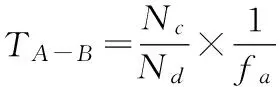

2.2.2占空比测量方法

占空比测量可在频率和周期测量方法之上进行改进,除了计数允许信号有效时间内标准频率信号的计数结果Na外,增加一个计数器对计数允许信号有效时间内被测信号为高电平时,标准频率信号的个数进行计数Nd,可得占空比:

D=Na/Nd.

2.2.3时间间隔测量方法

时间间隔测量在占空比测量方法之上改进得到,如图3所示。先通过预处理将A、B两路信号整合为TA-B信号,由

图3 时间间隔测量时序图

2.3提高仪器灵敏度的措施

1) 用射频线代替普通导线及示波器连线;

2) BNC接头和SMA-KWE内孔母头代替排针;

3) 加铝箔外壳抗干扰;

4) 设计电路时PCB板大面积铺地。

3结束语

本作品方案合理,对系统各个部分的设计难度进行了仔细考虑,较好地完成了设计的基本部分及发挥部分要求。系统整体性能良好,各被测参数的误差的绝对值均没有超出设计要求。

参考文献

[1]林建英,高苗苗,杨素英.基于SOPC的等精度数字频率计设计[J].研究与开发,2010,29(12):51-55.

[2]潘松,黄继业,潘明.EDA技术实用教程[M].第5版.北京:科学出版社,2013.

[3]毕满清.模拟电子技术基础[M].第2版.北京:电子工业出版社,2015.

收稿日期:2015-12-22

基金项目:太原科技大学大学生创新创业计划项目(Xj2014069)

作者简介:李江坤(1995- ),男,山西运城人,本科学历,主要研究探寻STM32系列单片机、现场可编程门阵列FPGA的使用。

文章编号:1674- 4578(2016)02- 0026- 02

中图分类号:TM935.13

文献标识码:A

Design of High Frequency Small Signal Frequency Meter

Li Jiangkun, Li Yang, Li Keren

(CollegeofElectronicandInformationEngineering,TaiyuanUniversityofScienceandTechnology,TaiyuanShanxi030024,China)

Abstract:This project consists of following modules: the damping circuit, wideband pass amplifier, reshaping circuit, FPGA measure module and the minimum units of STM32 single chip microcomputer. The paper designs a double amplifier with magnification of 40 dB which can amplify the valid values of signal from 10 mV to 1 V. The first stage uses OPA847 to realize the amplification of 26 dB, while the second stage uses the THS3201 to realize 14 dB. When the measured signal amplitude is high, the signal will be attenuated to 10 mV by the damping circuit. The reshaped signal produces a same frequency square wave signal. It uses the equal precision measurement method to measure frequency, time interval and duty cycle by Chip Cyclone IV FPGA. The measurement is transmitted to the STM32 single chip system through the serial for relevant processing and display.

Key words:STM32; FPGA; equal precision measurement method; wideband pass amplifier